## Synthesis of High-Speed Digital Systems<sup>1</sup>

Technical Report CRI-85-23

Nohbyung Park

November 8, 1985

<sup>&</sup>lt;sup>1</sup>This research was supported by the Army Research Office (Grant DAAG29-80-k-0083 and Grant DAAG29-83-K-0147) and the International Business Machines Corporation (Grant S 956501 Q LX A B22).

Approved for public release; distribution unlimited.

The views, opinions, and/or findings contained in this report are those of the authors, and should not be construed as an official Department of the Army position, policy or decision, unless so designated by other documentation.

## SYNTHESIS OF HIGH-SPEED DIGITAL SYSTEMS

bу

Nohbyung Park

A Dissertation Presented to the

FACULTY OF THE GRADUATE SCHOOL

UNIVERSITY OF SOUTHERN CALIFORNIA

In Partial Fulfillment of the Requirements for the Degree DOCTOR OF PHILOSOPHY

(Electrical Engineering)

September 1985

#### SECURITY CLASSIFICATION OF THIS PAGE (When Dete Entered)

| REPORT DOCUMENTATION                                                                                                      | PAGE                       | READ INSTRUCTIONS BEFORE COMPLETING FORM                                                           |  |

|---------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------|--|

| T. REPORT NUMBER  CRI-85-23                                                                                               | 2. GOVT ACCESSION NO.      | 3. RECIPIENT'S CATALOG HUMBER N/A                                                                  |  |

| Synthesis of High-Speed Digital Systems                                                                                   |                            | 5. Type of REPORT & PERIOD COVERED  Technical  Jan. 84 - Oct. 85  6. PERFORMING ORG. REPORT NUMBER |  |

| Nohbyung Park                                                                                                             |                            | DAAG29-83-K-0147                                                                                   |  |

| 9. PERFORMING ORGANIZATION NAME AND ADDRESS<br>Army Research Office<br>P.O. Box 12211<br>Research Triangle Park, NC 27709 |                            | 10. PROGRAM ELEMENT, PROJECT, TASK<br>AREA & WORK UNIT NUMBERS                                     |  |

| 11. CONTROLLING OFFICE NAME AND ADDRESS U. S. Army Research Office Post Office Box 12211 Research Triangle Park, NC 27709 |                            | November 1985  13. NUMBER OF PAGES  121                                                            |  |

| 14. MONITORING AGENCY NAME & ADDRESS(II ditional                                                                          | i tree Centrelling Office) | Unclassified  15. DECLASSIFICATION/DOWNGRADING SCHEDULE                                            |  |

16. DISTRIBUTION STATEMENT (of this Report)

Approved for public release; distribution unlimited.

17. DISTRIBUTION STATEMENT (of the electract entered in Block 20, If different from Report)

NA

#### IS. SUPPLEMENTARY NOTES

The view, opinions, and/or findings contained in this report are those of the author(s) and should not be construed as an official Department of the Army position, policy, or decision, unless so designated by other documentation

19. KEY WORDS (Continue on reverse side if necessary and identify by block number)

Automated design, synthesis, pipelining, overlapped execution, maximum execution overlap, clocking scheme synthesis, resource sharing, speed-cost tradeoff, scheduling, urgency measure, resource allocation, allocation table, latency, delay insertion.

#### 26. ASSTRACT (Continue on reverse side H necrossry and Identify by Meck number)

The design of high-speed systems and the automation of the design tasks involved is the topic of this thesis. In particular, the focus is on the use of pipelining and general overlapped execution. This thesis contains new techniques for speed-up, and describes the implementation of these techniques in a set of design automation programs. The new techniques produce designs

which share resources in a manner which is more complex than that used as common practice in working systems. The design of such complex hardware manually would be virtually impossible; thus, automated design is a key aspect of the proposed design methodology. The specific problem the thesis addresses is the following: the determination of the point in time each operation in a set of tasks is performed, and the manner in which the operators which execute each operation are reused from cycle to cycle. The first topic investigated in the thesis is clocking scheme synthesis. This type of synthesis involves selection of the number of clock phases, the duration of each phase, the amount of overlap in time between phases, and the assignment of functions to each clock phase. A theory of clocking is developed in the thesis, and used as the basis for software which automatically synthesizes clocking schemes. This program has been shown to improve manual designs by as much as a 60% The potential for application of the clocking scheme performance gain. synthesis to more general systems, including systolic arrays, is also described. Synthesis of pipelined data paths is the second topic investigated. synthesis task involves the generation of data paths along with a clocking scheme which overlaps execution of multiple computation tasks. Theory of general execution overlap is presented, including a description of four different scheduling techniques. The third topic covered is the insertion of delays into pipelined systems to avoid resource conflicts while increasing performance. The thesis describes a set of algorithms which perform optimal delay insertion. The algorithms described in the thesis have been programmed in Franz LISP, and execute quickly for problems of practical size.

# UNIVERSITY OF SOUTHERN CALIFORNIA THE GRADUATE SCHOOL UNIVERSITY PARK LOS ANGELES, CALIFORNIA 90089

| This dissertation, written by                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Nohbyung Park                                                                                                                                                                                                                |

| under the direction of his Dissertation Committee, and approved by all its members, has been presented to and accepted by The Graduate School, in partial fulfillment of requirements for the degree of DOCTOR OF PHILOSOPHY |

|                                                                                                                                                                                                                              |

| Aslian La Studies  jean Graduate Studies                                                                                                                                                                                     |

| Date October 4, 1985                                                                                                                                                                                                         |

| DISSERTATION COMMITTEE                                                                                                                                                                                                       |

| alie C. Parker Chairperson                                                                                                                                                                                                   |

| Ang n mille                                                                                                                                                                                                                  |

#### **DEDICATION**

To

My father and mother,

and my family

#### **ACKNOWLEDGEMENT**

I thank my advisor Professor Alice Parker for her guidance, support and endless encouragement. Her enthusiasm towards research and her insight into the problems of design automation made this thesis possible. I will never forget her warm heart and friendship that she showed towards me even when she herself was struggling.

I thank Professor Melvin Breuer and Professor Gary Miller for their valuable criticisms and suggestions which enhanced both technical contents and readability of this thesis.

I thank my parents for their endless love, support and patience, which made it possible for me to continue my graduate study, and finally to finish this thesis.

My wife, Jung-Ju, and my two little angels, Sehwa and Julie, also deserve my sincere thanks for their patience and sacrifices throughout my graduate study.

I thank my friends John Granacki, David Knapp, Fadi Kurdahi and Sarma Sastry for the warm friendship. They were my English teachers, technical consultants, and buddies. Thank you guys for lending your hands and helping me throughout the struggle I had to fight for a small piece of truth.

I gratefully acknowledge the financial support received from the Army Research Office (Grant DAAG29-80-k-0083 and Grant DAAG29-83-K-0147) and the International Business Machines Corporation (Grant S 956501 Q-LX A B22).

#### ABSTRACT

The design of high-speed systems and the automation of the design tasks involved is the topic of this thesis. In particular, the focus is on the use of pipelining and general overlapped execution in order to speed up the systems being implemented.

This thesis contains new techniques for speed-up, and describes the implementation of these techniques in a set of design automation programs. The new techniques produce designs which share resources and time in a manner which is more complex than that used as common practice in working systems. The manual design of such complex hardware would be virtually impossible; thus, automated design is a key aspect of the proposed design methodology.

The specific problem the thesis addresses is the following: the determination of the point in time each operation in a set of tasks is to be performed, and the manner in which the operators which execute each operation are reused from cycle to cycle.

The first topic investigated in the thesis is clocking scheme synthesis. This type of synthesis involves selection of the number of clock phases, the duration of each phase, the amount of overlap in time between phases, and the assignment of functions to each clock phase. A theory of clocking is developed in the thesis, and used as the basis for software which automatically synthesizes clocking schemes. This program has been shown to improve manual designs by as much as a 60% gain in performance. The potential for application of the clocking scheme synthesis to more general systems, including systolic arrays, is also described, and an example given.

Synthesis of pipelined data paths is the second topic investigated. This synthesis task involves the generation of data paths along with a clocking scheme which overlaps execution of multiple computation tasks. A theory of general execution overlap is presented, including a description of four different scheduling techniques. There is a brief description and example of the use of the pipeline synthesis software.

The third topic covered is the insertion of delays into pipelined systems to avoid resource conflicts while increasing performance. The thesis describes a set of algorithms which perform optimal delay insertion.

The algorithms described in the thesis have been programmed in Franz LISP, and execute quickly for problems of practical size.

### Table of Contents

| 1. | Introduction                                                      | 1  |

|----|-------------------------------------------------------------------|----|

|    | 1.1. The General Digital Design Optimization Problem              | 1  |

|    | 1.2. Design Issues                                                | 3  |

|    | 1.2.1. Speeding up digital systems                                | 3  |

|    | 1.2.2. Logic design and clocking                                  | 3  |

|    | 1.2.3. An example digital circuit design task                     | 5  |

|    | 1.2.4. Overlapping multi-phase clocks                             | 10 |

|    | 1.2.5. Two sequencing levels of a digital system                  | 12 |

|    | 1.2.6. Overlapped execution in micro-level sequencing             | 13 |

|    | 1.2.7. Definitions of the speed of digital systems                | 16 |

|    | 1.3. Research Overview                                            | 18 |

|    | 1.3.1. Clocking scheme synthesis for maximum execution overlap    | 18 |

|    | 1.3.2. Pipeline synthesis                                         | 21 |

|    | 1.3.3. Exhaustive algorithms                                      | 23 |

|    | 1.4. Related Work                                                 | 24 |

|    | 1.4.1. Clocking scheme synthesis                                  | 24 |

|    | 1.4.2. Pipeline clocking schemes                                  | 27 |

|    | 1.4.3. Pipeline scheduling                                        | 28 |

|    | 1.4.4. Other related work                                         | 31 |

|    | 1.5. Thesis Outline                                               | 33 |

| 2. | . Theory of Maximum Execution Overlap                             | 34 |

|    | 2.1. Introduction                                                 | 34 |

|    | 2.2. Definition of the Clocking Scheme Synthesis Task for Maximum | 36 |

|    | Execution Overlap                                                 |    |

|    | 2.3. The Problem Formulation                                      | 38 |

|    | 2.3.1. Specifying the functioning times of digital circuits       | 38 |

|    | 2.3.2. Modeling sequencing behavior of micro cycles               | 42 |

|    | 2.3.2.1. The micro-cycle graph                                    | 42 |

|    | 2.3.2.2. The chain of minor cycles                                | 45 |

|    | 2.3.3. The minimum possible length of a clock phase               | 47 |

|    | 2.3.4. A static clocking assumption                               | 50 |

|    | 2.3.5. Sequencing behavior of overlapped micro cycles             | 51 |

|    | 2.4. Synthesis of Clocking Schemes for Maximum Execution Overlap  | 56 |

|    | 2.4.1. Definition of variables                                    | 56 |

|    | 2.4.2. Execution speed analysis                                   | 57 |

|    | 2.4.3. Maximum execution speed analysis                           | 63 |

|                                                                           | vii |

|---------------------------------------------------------------------------|-----|

| 3. Synthesis of Maximum Execution Overlap Designs                         | 71  |

| 3.1. Introduction                                                         | 71  |

| 3.2. Optimal Stage Partitioning                                           | 72  |

| 3.2.1. Stage partitioning with a fixed stage time                         | 72  |

| 3.2.2. Stage partitioning with a fixed number of stages                   | 77  |

| 3.3. Performance Comparison - K Stage vs. Single Stage                    | 80  |

| 3.4. An Example Maximum Overlap Scheme For a Microprogrammed CPU          | 81  |

| 3.5. Extensions to More General Digital Designs                           | 86  |

| 3.5.1. Execution overlap schemes for completed designs                    | 86  |

| 3.5.2. A systolic array example                                           | 88  |

| 4. Theory of Pipeline Synthesis                                           | 92  |

| 4.1. Introduction                                                         | 92  |

| 4.1.1. Pipelining                                                         | 92  |

| 4.1.2. Synthesis of pipelines at the functional level                     | 95  |

| 4.1.3. Basic terms                                                        | 97  |

| 4.1.4. A fixed latency assumption                                         | 99  |

| 4.2. A Data Flow Graph Model for Pipeline Synthesis                       | 100 |

| 4.2.1. A brief review of the behavioral subspace                          | 100 |

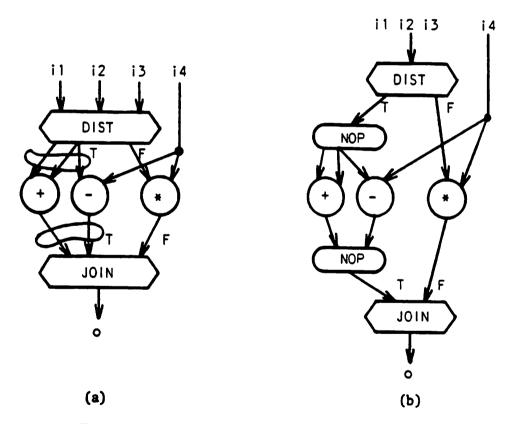

| 4.2.2. Merging data flow graphs                                           | 103 |

| 4.2.3. Conditional execution paths                                        | 104 |

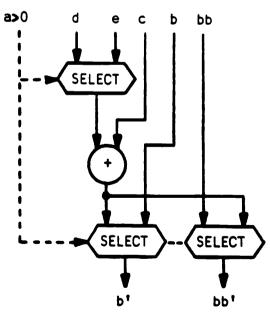

| 4.2.4. Conditional value selection                                        | 107 |

| 4.2.5. Insertion of no-operation (NOP) nodes                              | 109 |

| 4.2.6. Loop unrolling                                                     | 110 |

| 4.3. Scheduling and Resource Allocation                                   | 113 |

| 4.3.1. Relation between the scheduling and resource allocation tasks      | 113 |

| 4.3.2. Basic requirements of scheduling and resource allocation           | 114 |

| 4.3.3. Performance estimation                                             | 115 |

| 4.3.4. Cost constrained scheduling and resource allocation                | 116 |

| 4.3.5. Speed constrained scheduling and resource allocation               | 118 |

| 4.3.6. Patterns of resource allocation                                    | 121 |

| 4.4. Resource Sharing between Mutually Exclusive Operations               | 124 |

| 4.4.1. Conditional execution paths and stage construction                 | 125 |

| 4.4.2. Conditional and unconditional resource sharing                     | 126 |

| 4.5. Node Coloring for Automatic Testing of Mutual Exclusion              | 129 |

| 4.5.1. A node coloring algorithm                                          | 129 |

| 4.5.1.1. Node coloring rules                                              | 130 |

| 4.5.1.2. A procedure for mutual exclusion testing                         | 132 |

| 4.5.2. Computation of the maximum number of actually performed operations | 134 |

| 4.6 Some Remarks on Cost-performance Ontimization                         | 136 |

|                                                                          | viii |

|--------------------------------------------------------------------------|------|

| 5. Synthesis of Pipelines                                                | 137  |

| 5.1. Introduction                                                        | 137  |

| 5.1.1. Three types of polynomial-time scheduling algorithms              | 137  |

| 5.1.2. Urgency measures of operations                                    | 138  |

| 5.1.3. Forward scheduling and backward scheduling                        | 139  |

| 5.1.4. The maximal-scheduling and nonoverlap-scheduling                  | 141  |

| 5.2. The Feasible-scheduling Algorithm                                   | 144  |

| 5.2.1. Algorithm outline                                                 | 144  |

| 5.2.2. Resource allocation table                                         | 147  |

| 5.2.3. Resource sharing between mutually exclusive operations            | 150  |

| 5.3. Scheduling with Speed and Cost Constraints                          | 150  |

| 5.3.1. Design-space boundaries                                           | 150  |

| 5.3.2. Synthesis with a cost constraint                                  | 15   |

| 5.3.3. Synthesis with performance constraints                            | 16   |

| 5.4. An Exhaustive Algorithm for Pipeline Synthesis                      | 16   |

| 5.5. A Synthesis Example                                                 | 17   |

| 6. Pipeline Delay Insertion                                              | 18   |

| 6.1. Performance Improvement by Delay Insertion                          | 18   |

| 6.2. Definition of the Problem                                           | 18   |

| 6.3. An Optimal Delay Insertion Algorithm                                | 18   |

| 7. Conclusions and Future Research                                       | 193  |

| 7.1. Main Contributions                                                  | 19   |

| 7.2. Future Research                                                     | 19   |

| Appendix A. A Stage Partitioning Algorithm for Maximal Execution Overlap | 197  |

| Appendix B. A Node Coloring Algorithm                                    | 203  |

| Appendix C. An Algorithm for Counting Module-usage Frequency             | 206  |

| References                                                               | 200  |

|                                                                          |      |

.

.

### List of Figures

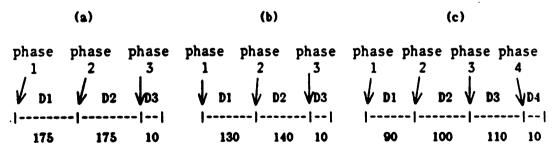

| Figure 1.2-1: | A data flow graph for a 16-bit unsigned integer multiplication.                         | 5          |

|---------------|-----------------------------------------------------------------------------------------|------------|

| Figure 1.2-2: | A 16-bit parallel unsigned integer multiplier.                                          | 6          |

| Figure 1.2-3: | Timing diagram for the multiplier of Figure 1.2-2.                                      | 7          |

| Figure 1.2-4: | A multiplier with execution overlap.                                                    | 8          |

| Figure 1.2-5: | Overlapped execution on the multiplier of Figure                                        | 10         |

|               | 1.2-4.                                                                                  |            |

| Figure 1.2-6: | A non-overlapping 3-phase clock.                                                        | 11         |

| Figure 1.2-7: | An overlapping 3-phase clock.                                                           | 11         |

| Figure 1.2-8: | Sequencing engines of a digital system.                                                 | 12         |

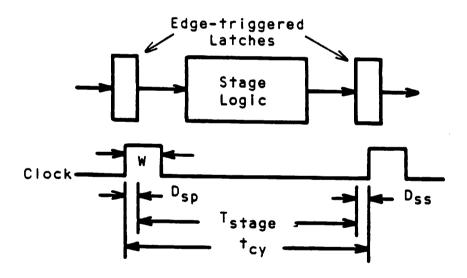

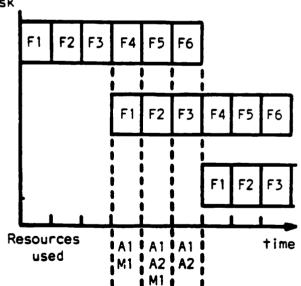

| Figure 1.2-0: | Examples of micro cycle sequencing (Gantt Chart).                                       | 15         |

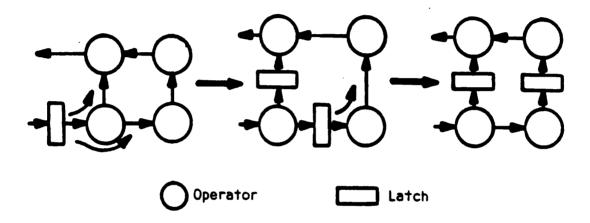

| Figure 1.4-1: | Leiserson's retiming.                                                                   | 25         |

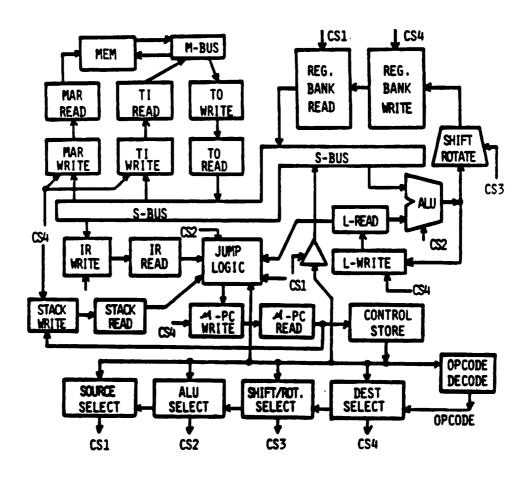

| Figure 2.3-1: | A circuit graph of a microprogrammed CPU                                                | 41         |

|               | (HP-21MX).                                                                              |            |

| Figure 2.3-2: | Examples of the micro-cycle graphs in the circuit                                       | 44         |

|               | graph of Fig. 2.3-1.                                                                    |            |

| Figure 2.3-3: | The chains of minor cycles derived from the results                                     | 46         |

|               | of stage partitioning.                                                                  |            |

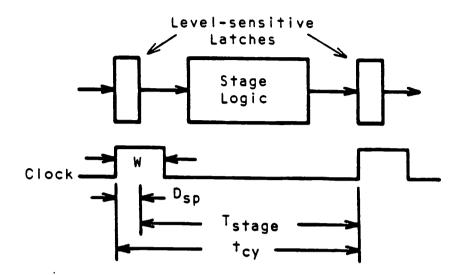

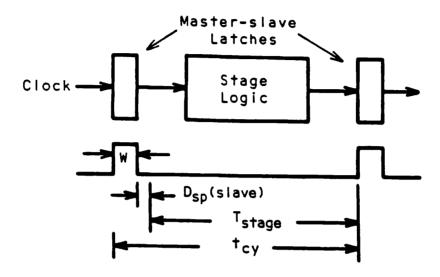

| Figure 2.3-4: | Clock timing for level-sensitive latches.                                               | 49         |

| Figure 2.3-5: | Clock timing for edge-triggered latches.                                                | 49         |

| Figure 2.3-6: | Clock timing for master-slave latches.                                                  | 50         |

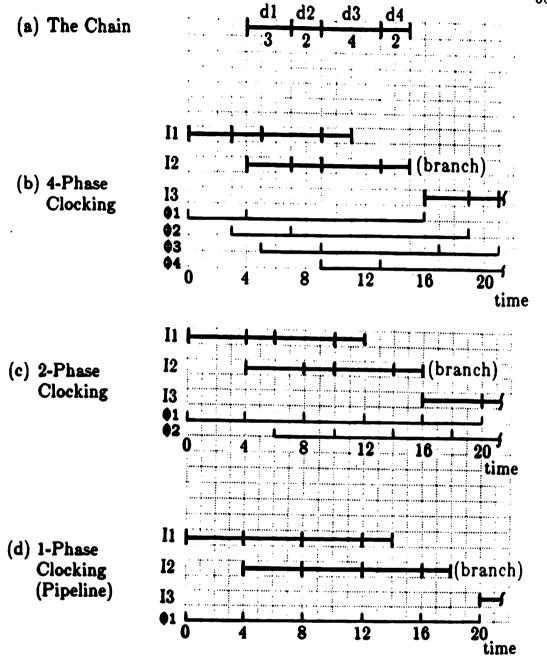

| Figure 2.3-7: | Examples of micro cycle sequencing and clocking.                                        | 52         |

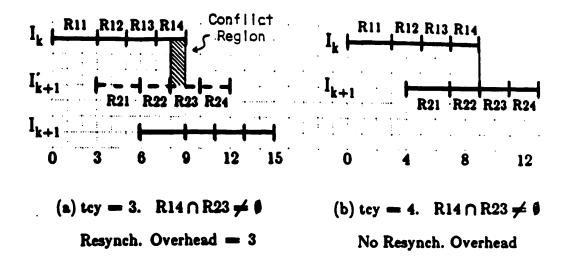

| Figure 2.3-8: | Resynchronization overhead due to data/resource contention.                             | 54         |

| Figure 2.3-9: | The number of clock phases vs. resynchronization overhead.                              | 55         |

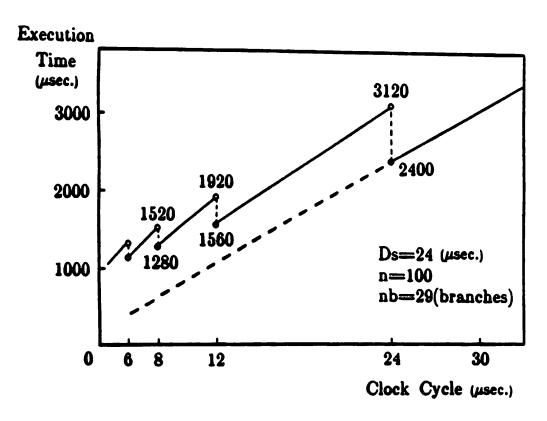

| Figure 2.4-1: | Execution time vs. clock period.                                                        | 68         |

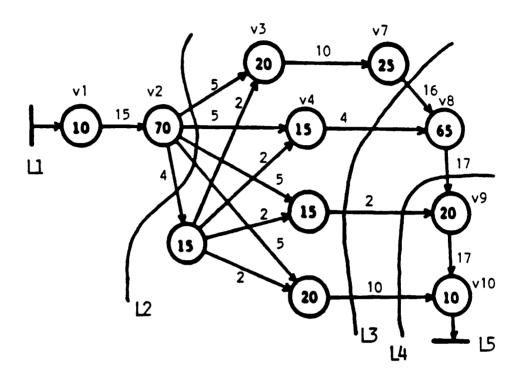

| Figure 3.2-1: | An example of a partitioned micro-cycle graph.                                          | <b>7</b> 5 |

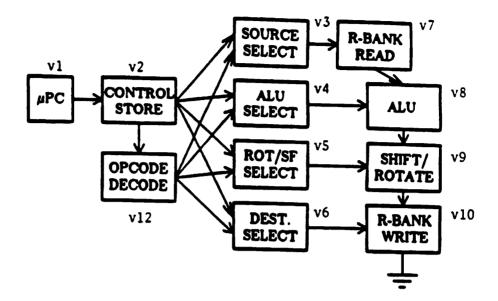

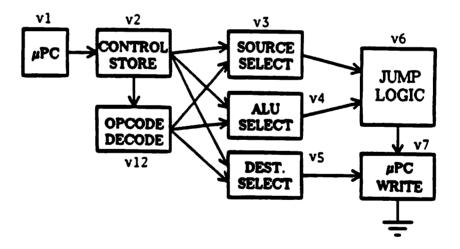

| Figure 3.4-1: | Stage partitioning of the HP-21MX CPU.                                                  | 82         |

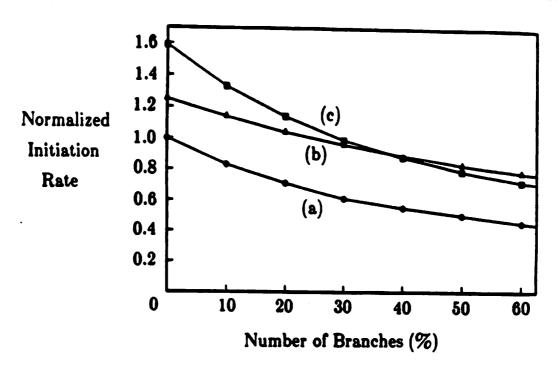

| Figure 3.4-2: | Performance comparison of the HP-21MX CPU.                                              | 85         |

| Figure 3.5-1: | An example of circuit partitioning.                                                     | 87         |

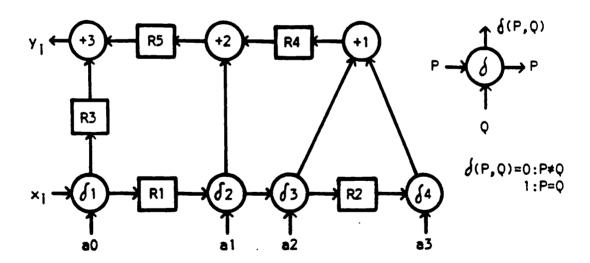

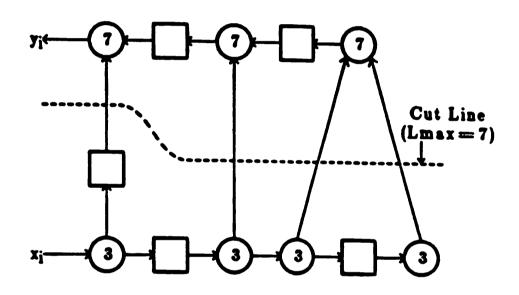

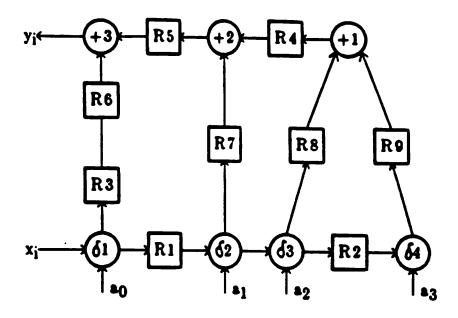

| Figure 3.5-2: | A systolic array evaluating $\sum_{j=0}^{3} \delta(\mathbf{x_{i-j}}, \mathbf{a_{j}})$ . | 88         |

| Figure 3.5-3: | Stage partitioning of the systolic array of Fig. 3.5-2.                                 | 88         |

| Figure 3.5-4: | Stage partitioning result of the systolic array of Fig. 3.5-2                           | 80         |

|               |                                                                                                             | x   |

|---------------|-------------------------------------------------------------------------------------------------------------|-----|

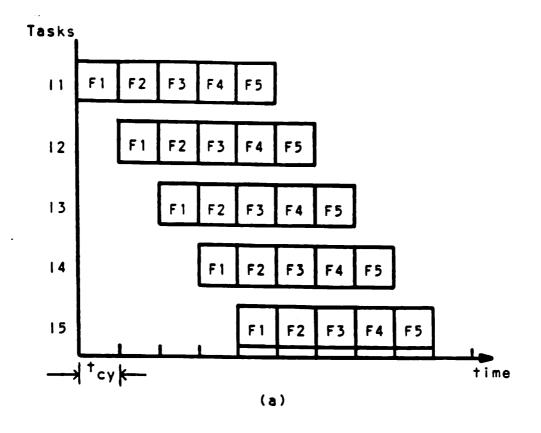

| Figure 4.1-1: | A partitioned data flow graph and its execution                                                             | 93  |

| rigute 4.1-1. | timing.                                                                                                     | 80  |

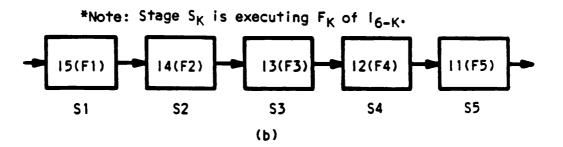

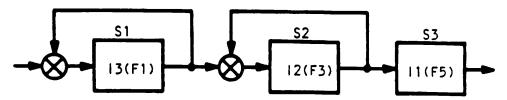

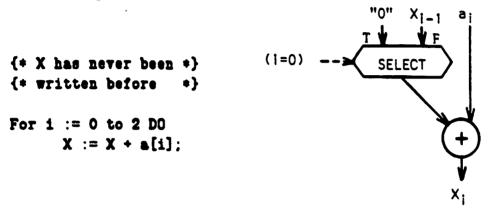

| Figure 4.1-2: | (a) A pipelining schedule and (b) a pipeline.                                                               | 94  |

| Figure 4.1-3: |                                                                                                             | 95  |

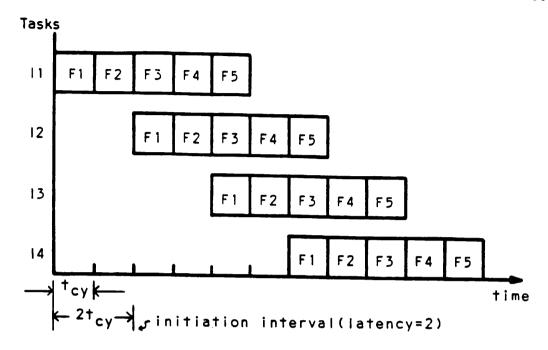

| Figure 4.1-4: | An example of pipelining with a fixed latency of 2.                                                         | 96  |

| Figure 4.2-1: |                                                                                                             | 101 |

| Figure 4.2-2: | An example data flow graph with implicit conditionals.                                                      | 102 |

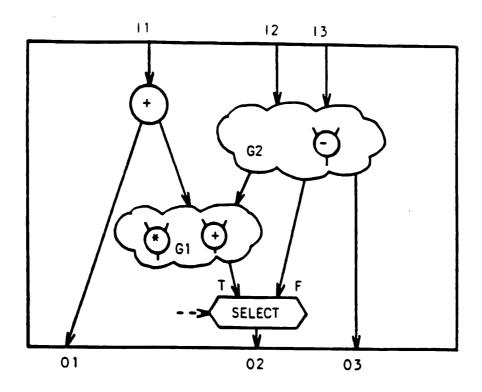

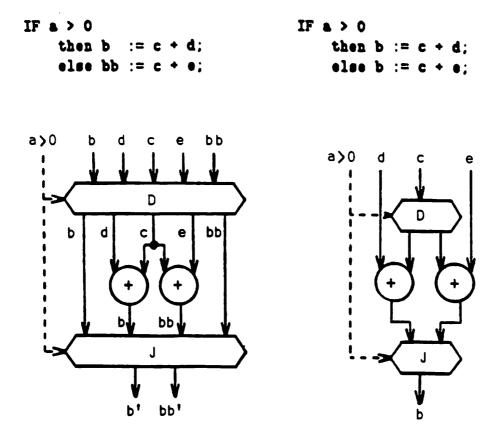

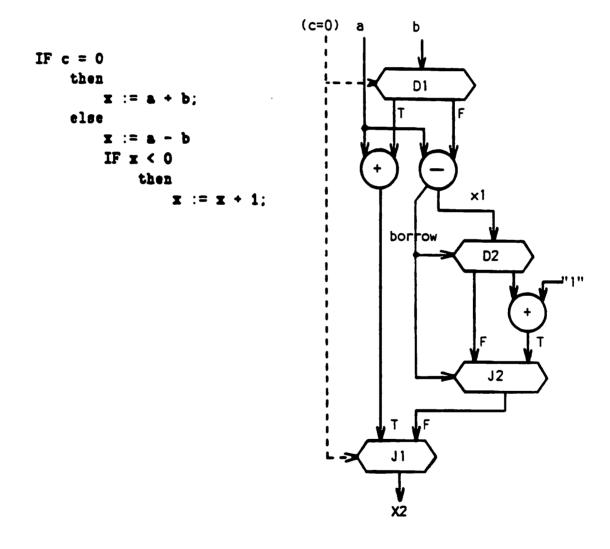

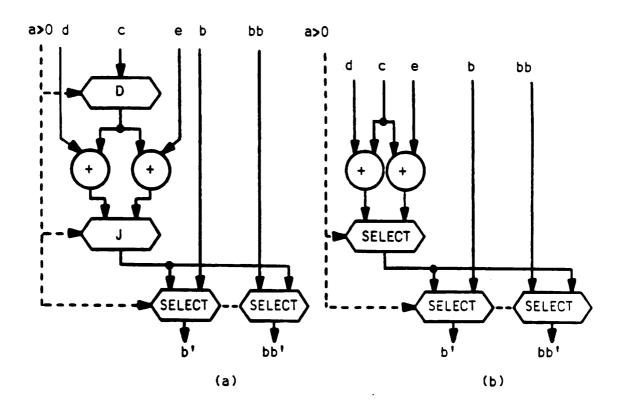

| Figure 4.2-3: | data flow graphs with conditional execution paths.                                                          | 105 |

| Figure 4.2-4: | An example of nested distribute-join pairs.                                                                 | 106 |

| Figure 4.2-5: |                                                                                                             | 107 |

|               | 4.2-3: (a) simplification and (b) elimination of the distribute-join pair.                                  |     |

| Figure 4.2-6: | Transformation of the graph of Figure 4.2-5-(b).                                                            | 108 |

| Figure 4.2-7: |                                                                                                             | 109 |

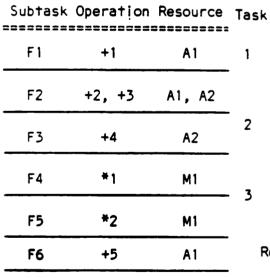

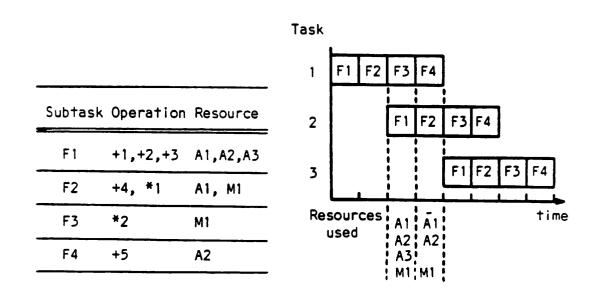

| Figure 4.3-1: | An example of cost constrained scheduling and resource allocation.                                          | 119 |

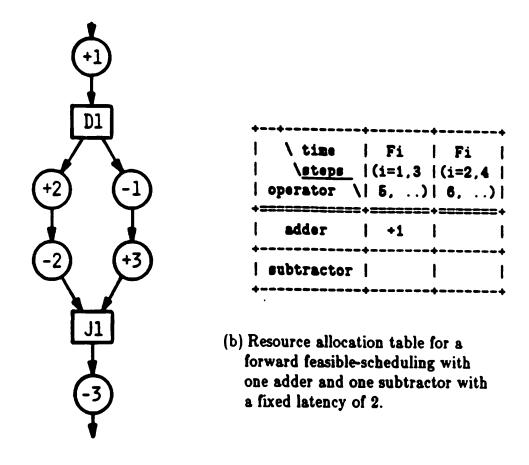

| Figure 4.3-2: | A scheduling and resource allocation with fixed latency 2 for the data flow graph of Figure 4.3-1.          | 121 |

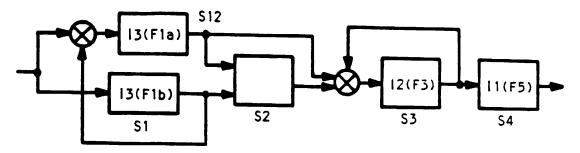

| Figure 4.3-3: |                                                                                                             | 122 |

| Figure 4.3-4: | A more generalized form of shared resource allocation.                                                      |     |

| Figure 4.3-5: | An example of generalized resource sharing: (a) a staged data flow graph and (b) a pipeline implementation. | 124 |

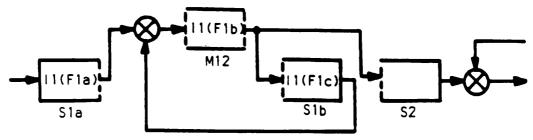

| Figure 4.4-1: | Resource sharing between mutually exclusive operations within a subtask.                                    | 125 |

| Figure 4.4-2: | Moduling sharing between mutually exclusive operations.                                                     | 128 |

| Figure 4.5-1: | A node-colored data flow graph.                                                                             | 131 |

| Figure 5.1-1: | • • • • • • • • • • • • • • • • • • • •                                                                     | 140 |

| Figure 5.1-2: | A forward maximal-schedule for the data flow graph of Figure 5.1-1.                                         | 142 |

| Figure 5.1-3: | A nonoverlap schedule for the data flow graph of Figure 5.1-1.                                              | 143 |

| Figure 5.2-1: | •                                                                                                           | 146 |

| Figure 5.2-2: |                                                                                                             | 148 |

| Figure 5.2-3: | An example usage of the allocation table during the forward scheduling shown in Figure 5.2-1-(a).           | 149 |

| Figure 5.2-4: |                                                                                                             | 152 |

| Figure 5.2-5: | The data flow graph of Figure 4.4-1 scheduled.                                                              | 153 |

| Figure 5. | .2-6: | The completed resource allocation.                                                                                             | 154 |

|-----------|-------|--------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5. | 2-7:  | An example of a deadlock due to forced conditional                                                                             | 155 |

|           |       | resource sharing.                                                                                                              |     |

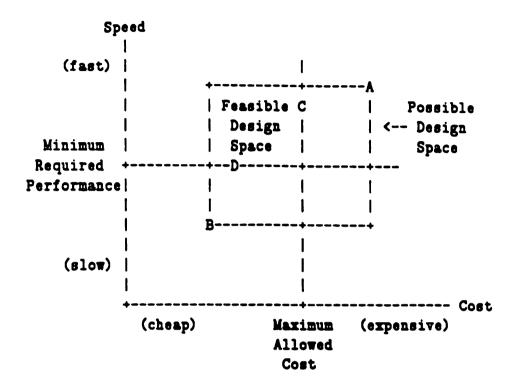

| Figure 5. | 3-1:  | Design space boundaries.                                                                                                       | 157 |

| Figure 5. | 3-2:  | Performance improvement by adding more modules.                                                                                | 161 |

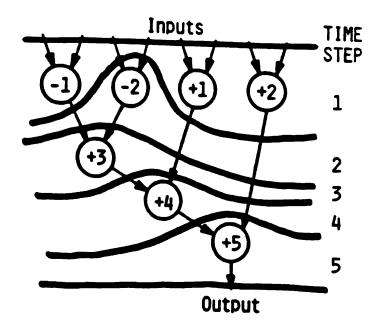

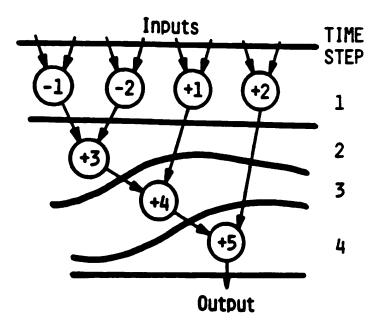

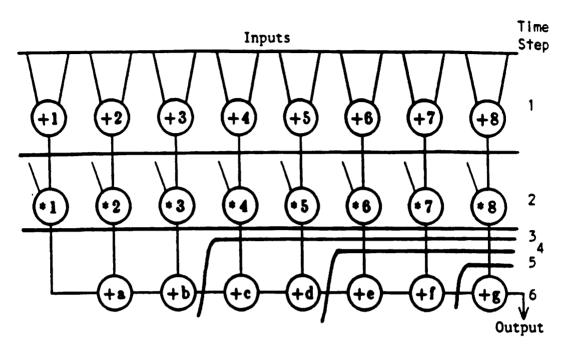

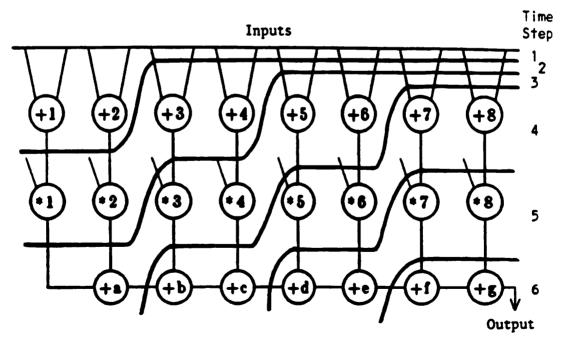

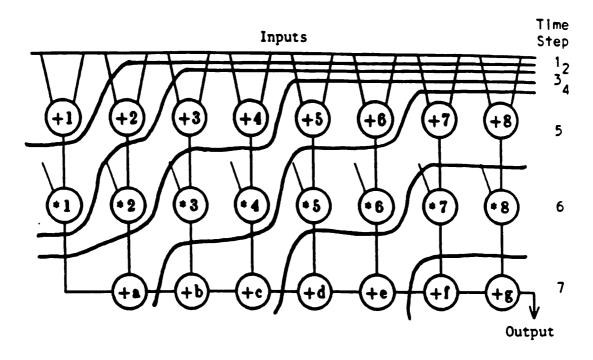

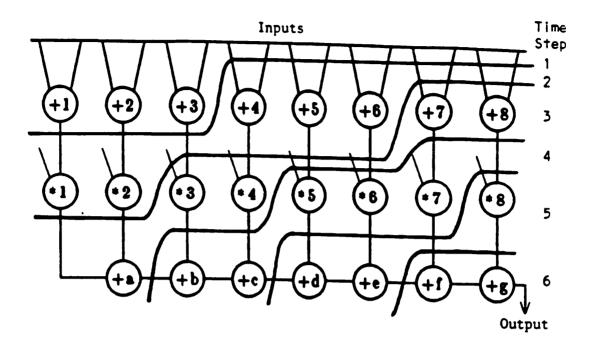

| Figure 5. |       | The maximal schedules for a 16-point FIR digital filter with stage time limit 100 nsec.                                        | 166 |

| Figure 5. |       | A backward feasible schedule for the digital filter with 3 multipliers and 5 adders, latency 3, and stage-time limit 100 nsec. | 167 |

| Figure 5. |       | Time step ranges of the nodes of the FIR filter example.                                                                       | 168 |

| Figure 5. | .4-4: | An optimal feasible schedule for the digital filter.                                                                           | 171 |

| Figure 6. | .1-1: | An example reservation table.                                                                                                  | 182 |

| Figure 6. | .1-2: | An example of delay insertion.                                                                                                 | 183 |

| Figure 6. | .2-1: | A reservation table marked with delay elements.                                                                                | 186 |

| Figure 6  | .2-2: | Delay insertion for the reservation table of Figure 6.2-1.                                                                     | 187 |

| Figure 6  | .3-1: | Left-to-right sequential adjustment.                                                                                           | 190 |

| Figure 6  |       | Right-to-left sequential adjustment.                                                                                           | 191 |

| Figure 6  |       | An optimal delay insertion for the reservation table of Figure 6.2-1 for latency 3.                                            | 192 |

# Chapter 1 Introduction

#### 1.1. The General Digital Design Optimization Problem

The general digital design problem is that of producing a hardware implementation of a system which exhibits a required behavior and satisfies any constraints imposed on it. Among the most typical design constraints are minimum required speed and maximum allowed cost and power consumption. Examples of desired goals are to maximize speed, to maximize speed-to-cost ratio, and to maximize speed-to-power consumption ratio.

Unfortunately, these optimization tasks often compete with each other. For example, the minimum cost implementation will rarely be the maximum speed implementation. For this reason, desired design goals are often used in addition to constraints in order to direct the optimization process towards a certain direction. Whenever there is more than one noninferior design alternative, the one that best meets the desired goals will be chosen.

The synthesis task can be partitioned into subtasks which will be repeated as the design proceeds towards a direction guided by constraints and desired goals, as listed below:

- 1. choose an appropriate design style (design style selection),

- 2. choose potentially optimal sets of functional and storage modules which can maximize speed and minimize cost and/or power consumption (module selection),

- 3. allocate operations and data values to functional and storage

elements. Partial interconnection may also be carried out (resource allocation),

- 4. find an optimal configuration and/or interconnection of modules so as to maximize performance. Detailed control hardware and/or microprograms are also synthesized during this phase (configuration and interconnection), and

- 5. for a given design which is non-optimal, find a near-optimal reconfiguration of the design within an allowed cost increase or speed decrease limit (performance increase or cost reduction by reconfiguration).

In cases when near-optimal solutions are desired, the complexity of these tasks is in decreasing order, since the solutions for the earlier phase problems can only be guaranteed to be optimal after a large number of (in worst case, all possible) solutions for the later-phase problems are compared. Unfortunately, finding optimal solutions even for some of the later phase problems is known to be intractable. For example, the resource allocation problem can be modeled as a precedence constrained scheduling problem, which is known to be NP-Complete [Gary 79]. Also, as a subproblem of subtask 4, the microcode compaction problem has been proven to be NP-Complete [Robertson 79]. Many other problems with exponential complexity in various design phases have been identified [Breuer 72, Sastry 82]. Only several problems of the last subtask turn out to be polynomial-time solvable [Dervos 83, Leiserson 83].

In practice, synthesis tasks are carried out by estimating and evaluating cost and speed of feasible hardware implementations of the system at various stages of the design process. Naturally, in order to carry out these tasks efficiently and to get a near-optimal design, a good estimation and evaluation strategy is crucial. Especially, in the last two phases described above, it is desirable that the speed estimation and evaluation procedures be able to suggest possible changes in the given design which can increase the speed.

#### 1.2. Design Issues

#### 1.2.1. Speeding up digital systems

Although there are many styles and variations of techniques for the control of high-performance digital systems, they can be classified as following two basic concepts:

- distributed processing under asynchronous distributed control, and

- overlapped (parallel) processing under centralized control.

The former class includes digital systems with multiple autonomous control sequencers such as multi-microprocessor systems, and VLSI circuits with multiple autonomous control modules and interfaces (e.g., a UART with separate sequencers for receiver and transmitter). The latter class includes systems or modules with only a single centralized controller. Any system belonging to the first class can be partitioned into subsystems and/or modules each of which can be classified under the latter class, although there are several complex control partitioning problems which must be addressed. The overall speed of such a distributed processing system will be determined as a function of the speed of each partitioned subsystem and/or module. Accordingly, we will focus our discussion on the latter case, overlapped processing under centralized control.

#### 1.2.2. Logic design and clocking

In any sequential circuit, there are two logic components: the combinational logic blocks which perform the required functions and the storage elements which save the results of the combinational logic blocks. In the case of simple, sequential circuits, where an instruction or a state transition requires a part or all of the combinational circuitry and the results are latched into storage elements all at once, the interaction between the two components

is simple. The timing characteristics of the combinational circuitry dominates the determination of the speed of the circuit. However, in the case of complex, fast systems such as mainframe computer systems, a system is partitioned into subsystems (or stages as in a pipelined system) and fast multiple-phase clocks are used. System partitioning is performed for four reasons:

- due to physical limitations such as size or power consumption,

- to provide modularity and maintainability such as testing and design changes,

- to support resource sharing, and/or

- to support overlapped execution of different tasks.

In such a partitioned or staged system, the timing characteristics of the combinational and sequential components interact very closely and affect the performance of the systems in a different way. A computation task is partitioned into subtasks and subtasks are carried out in many subsystems or stages. The results of one or more subsystems may need to be fed to other subsystems to complete the original task. Then, the subsystems freed up can be used for other tasks. There are two obvious objectives in designing such complex systems:

- optimal system partitioning into subsystems, and

- optimal sequencing control to carry out tasks and subtasks.

Both partitioning and sequencing control require proper buffering and synchronization of value transfer from subsystem to subsystem, which involves placement of storage elements in between and/or inside each subsystem, and the proper timing and sequence for clocking the storage elements.

#### 1.2.3. An example digital circuit design task

In any digital system, cost (sometimes analogous to chip area) and speed are traded off to get a system which meets particular requirements. How cost and speed are traded off, however, varies from design to design. The complexities of the problem are illustrated by a brief multiplier example.

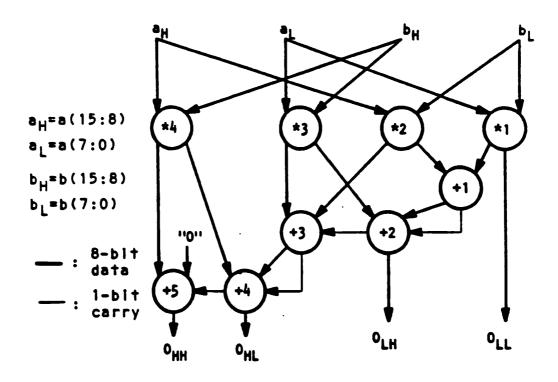

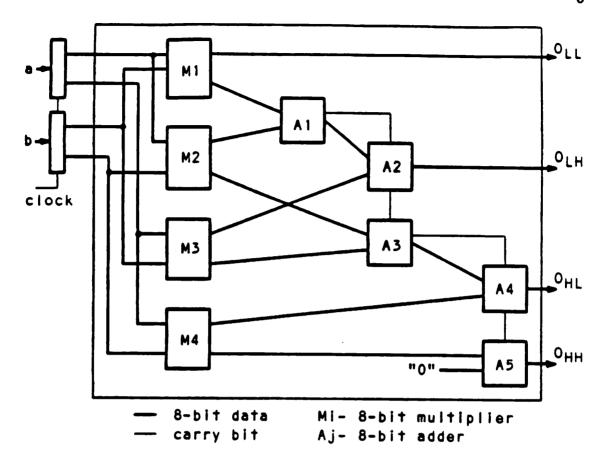

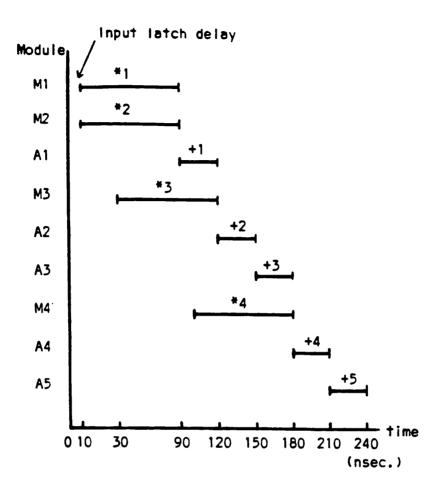

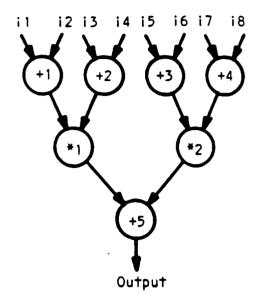

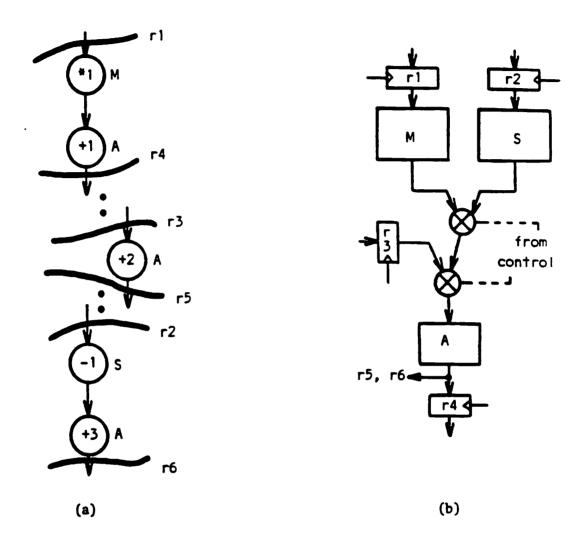

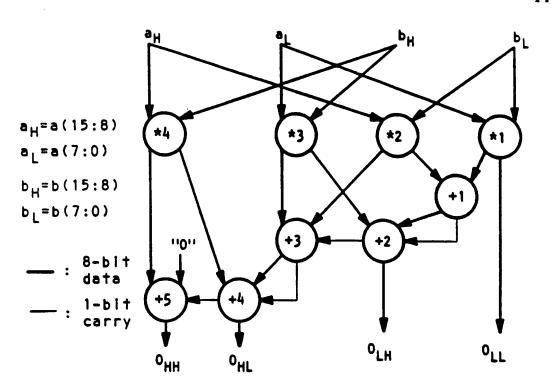

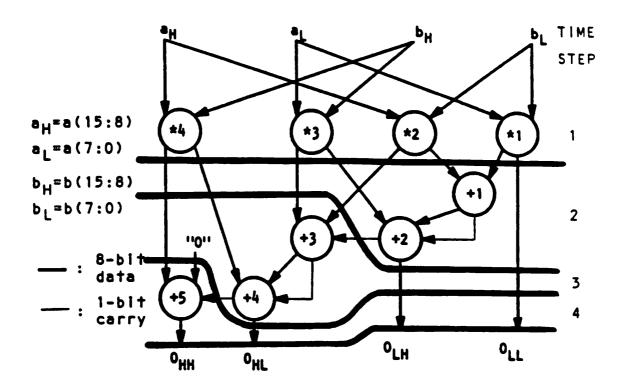

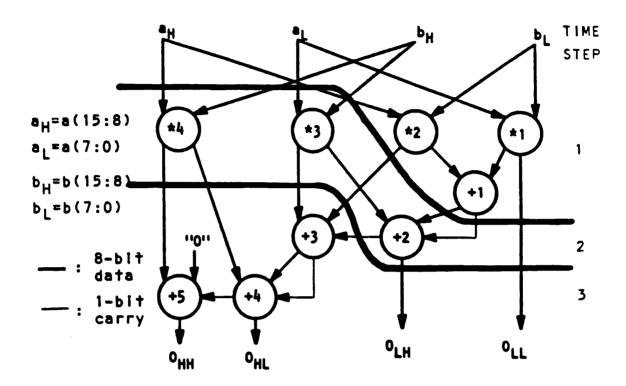

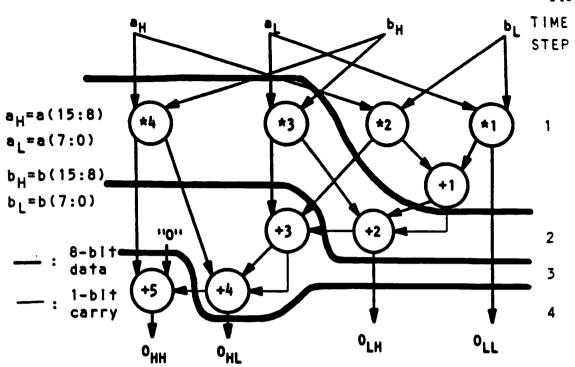

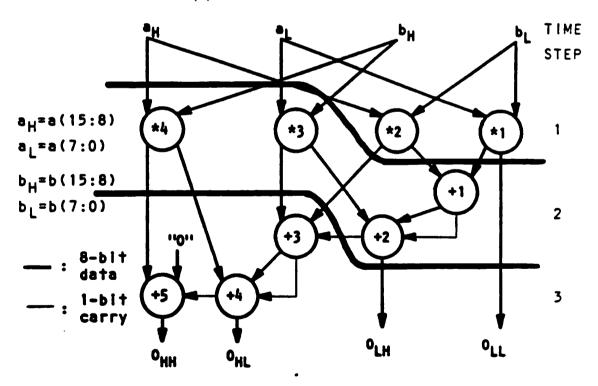

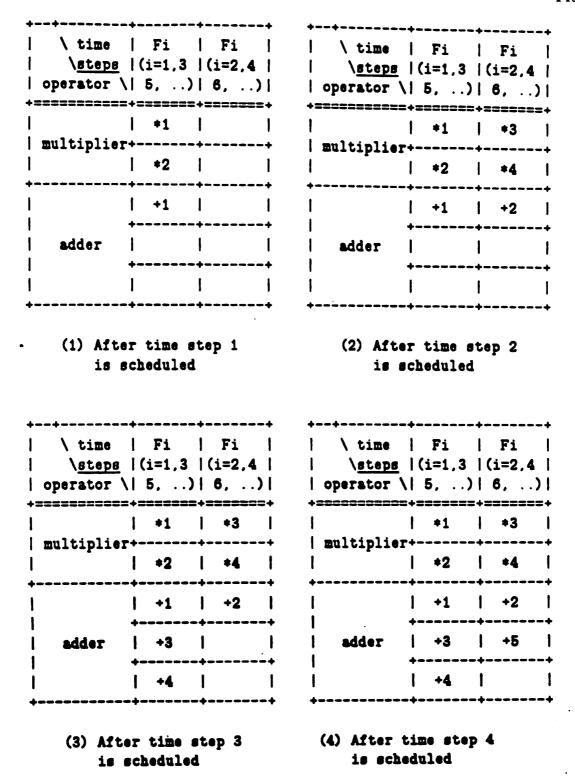

Suppose we have decomposed a 16-bit multiply operation as shown in Figure 1.2-1, using 8-bit multiply and addition operations. The nodes indicate operations, and the arcs indicate values. The task is to design an inexpensive, fast multiplier from this data flow graph. An obvious solution using four 8-bit multipliers  $(M_1 \text{ through } M_4)$  and five 8-bit adders  $(A_1 \text{ through } A_5)$  is shown in Figure 1.2-2. The timing diagram for this multiplier is shown in Figure 1.2-3, where the delay time of an 8-bit multiplier and an 8-bit adder are 80 and 30 nsec., respectively. The register propagation delay is 10 nsec.

Figure 1.2-1: A data flow graph for a 16-bit unsigned integer multiplication.

Figure 1.2-2: A 16-bit parallel unsigned integer multiplier.

However, since there has been no reuse of resources, the resources are only busy a fraction of the time. There are two possible ways to increase resource utilization without sacrificing performance.<sup>1</sup> These are

- 1. use less modules and reuse them for different operations as many times as necessary, or

- 2. when multiple tasks are to be executed sequentially, partition each task into subtasks and execute subtasks of multiple tasks on different parts of the circuit simultaneously (overlapped execution of multiple tasks).

<sup>&</sup>lt;sup>1</sup>We could increase resource utilization greatly by using only one multiplier and one adder, but at a great sacrifice in performance!

Figure 1.2-3: Timing diagram for the multiplier of Figure 1.2-2.

The first method takes a local view of the multiply operation, and assumes it is required to be performed only as often as the outputs can be produced. No other multiply operation would require the hardware until the present task was completed. As long as multiplies come along slower than the speed of the multiplier, this is a valid viewpoint.

Sometimes, we cannot consider a single multiply operation in isolation. In some cases the multiply tasks can be generated at a faster rate than the total multiply time. In this case, we must begin a second multiply before the first is completed, utilizing the resources left idle by the first multiply as it goes into the later stages of its computation. In the extreme case, we can overlap

enough multiply operations so that the resources are all busy all the time, and the multiplies are handled as fast as required. This overlapping in time, in its simplest form, is sometimes referred to as pipelining.

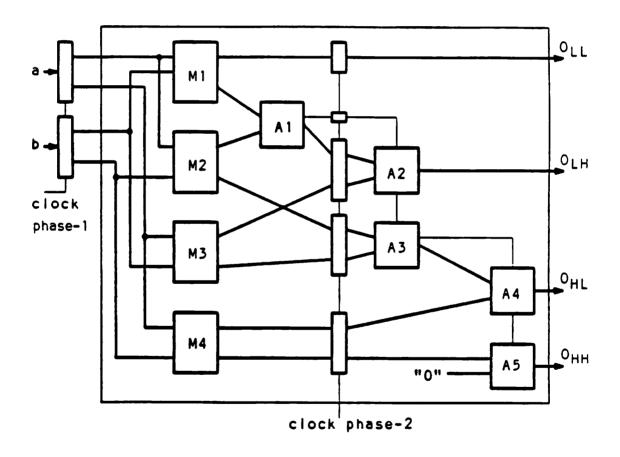

An implementation of the multiplier with overlaps is shown in Figure 1.2-4. This multiplier uses the same set of functional modules as the multiplier in Figure 1.2-2. Only some latches have been added. These latches divide the circuit into two stages and prevent direct flow of values between stages. For this reason, they are called stage latches.

Figure 1.2-4: A multiplier with execution overlap.

With this multiplier, a 16-bit multiply is performed in two steps as follows. (Refer to the data flow graph of Figure 1.2-1.)

- The input latches are clocked by clock phase-1 and store the inputs.

8-bit multiplications \*1 through \*4 are performed by 8-bit multipliers M<sub>1</sub> through M<sub>4</sub>. As soon as the results of \*1 and \*4 are available, the +1 operation is performed by adder A1.

- 2. The stage latches are clocked by clock phase-2 and store the results of the previous step, i.e., the outputs of M1 through M4, and A1. Addition operations +2 through +4 are performed by adders  $A_2$  through  $A_5$  and the results are output.

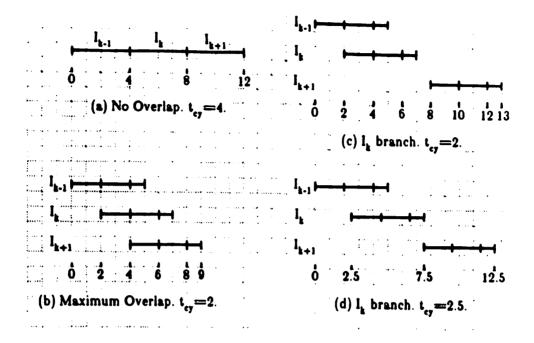

The timing diagram for this multiplier is the same as Figure 1.2-3 except that the operations +2 through +5 are delayed by 10 nsec. due to the propagation delay of the stage latches. Therefore we cannot perform a multiply operation faster than before. However, the effective throughput is greatly increased since we can perform more than one operation in parallel. As soon as a 16-bit multiply operation moves to the second stage by storing the results of the first stage in the stage latch, another 16-bit multiply can start on the first stage. On this multiplier, a new multiply task can be initiated every 130 nsec. The resource utilization for the 8-bit multipliers has increased to 61 percent as a result of the overlaps.

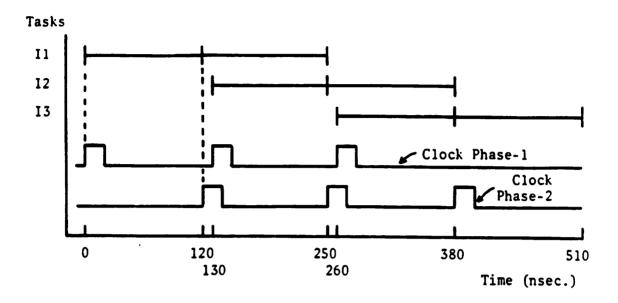

Figure 1.2-5 shows the timing of overlapped execution of three multiply tasks,  $I_1$ ,  $I_2$ , and  $I_3$ , using an overlapped multi-phase (two-phase) clock which we will discuss in the following section.

The choice of the two speed-up techniques depends on the design constraints, the desired optimization goals and the input task stream. If the computation tasks arrive at a high rate and the designer wants to make the design as fast as possible, he may choose the latter technique. On the other hand, if the cost budget (either the total cost or the total area) is very tight, he would choose the former technique. Depending on the tightness of the constraints, the desired optimization goals, and the arrival rate of the tasks, the best choice might be a mixture of both techniques.

Figure 1.2-5: Overlapped execution on the multiplier of Figure 1.2-4.

#### 1.2.4. Overlapping multi-phase clocks

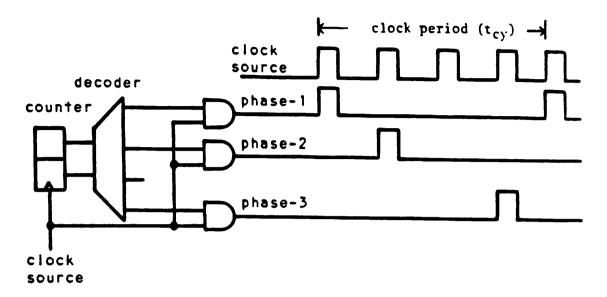

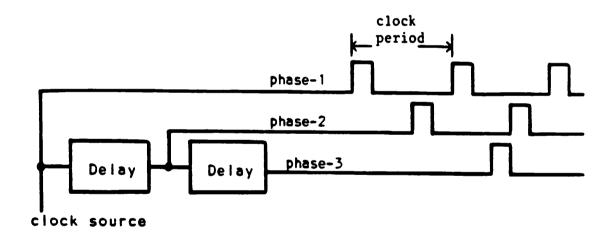

A multi-phase clock cycle consists of a sequence of clock phases delayed from a single clock source. Since each phase is delayed from a single clock source, all the phases have the same pitch, which is called a clock period. The time interval from the tick of a phase to the tick of its next phase is called the length of the phase. Each phase can be of different length. An example of a non-overlapping 3-phase clock is shown in Figure 1.2-6. In case of a non-overlapping multiphase clock, the clock period is the same as the sum of the lengths of the clock phases.

An overlapping multiphase example is shown in Figure 1.2-7. In the case of an overlapping multi-phase clock, the clock period is shorter than the total sum of the clock phases. A new clock cycle starts before the last clock phase of the previous cycle.

Figure 1.2-6: A non-overlapping 3-phase clock.

Figure 1.2-7: An overlapping 3-phase clock.

The clock needed for the sequencing of Figure 1.2-5 is an overlapping two-phase clock with a clock period of 130 nsec. The length of the first phase is 120 nsec. and the second phase 130 nsec.

#### 1.2.5. Two sequencing levels of a digital system

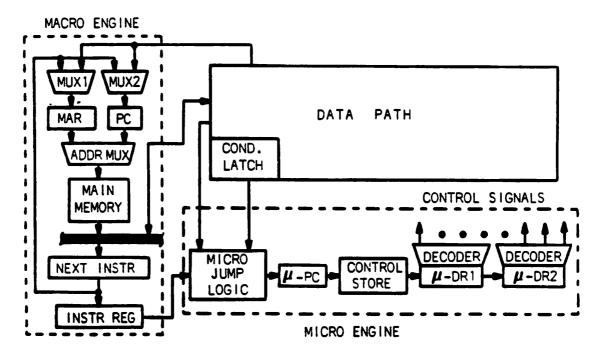

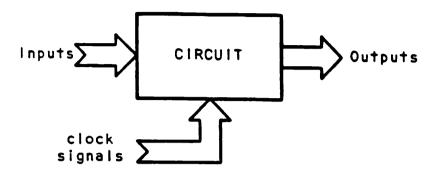

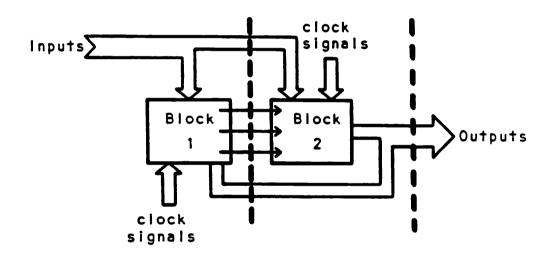

In digital systems with two-level control structures, sequencing is carried out on two levels, the macro and micro levels. An execution instance of a machine instruction or a major loop of a finite-state-machine (macro task) corresponds to a macro cycle and an execution instance of a microinstruction or a state of an finite-state-machine (micro task) corresponds to a micro cycle, which are carried out by a macro engine and a micro engine, respectively. Most Von Neumann-type computer CPUs and simple digital systems have a two-level control structure. In most digital systems whose control structure has more than two levels, we can also find similar levels of sequencing corresponding to the macro and micro levels.<sup>2</sup> Figure 1.2-8 shows an example of a microprogrammed computer CPU.

Figure 1.2-8: Sequencing engines of a digital system.

<sup>&</sup>lt;sup>2</sup>For a nano-programmed CPU such as the Nanodata QM-1, nanoinstruction cycles can be considered to be the micro cycles, and microinstruction cycles and machine instruction cycles can be merged and considered to be the macro cycles of our classification.

Macro cycles consist of sequences of one or more micro cycles. Overlapping macro cycles are implemented by proper partitioning of macro cycles into sequences of micro cycles. For example, an operand needed by the current machine instruction being executed could be fetched by some microinstruction of the previous machine instruction and some microinstruction of the current machine instruction may fetch the next machine instruction in advance.

A micro cycle consists of **minor** cycles (register-transfers). Each minor cycle reads from storage elements, transforms and stores data and/or control values to storage elements which are used to buffer the flow of the values between functional elements.<sup>3</sup> Such buffering storage elements are called stage latches. For the micro engine of figure 1.2-8,  $\mu$ -PC,  $\mu$ -DR1,  $\mu$ -DR2 and "Cond. Latch" can be considered to be stage latches. In general, any storage element in the system can be a stage latch.

#### 1.2.6. Overlapped execution in micro-level sequencing

At the macro level, various techniques for speeding up digital systems exist. Examples are instruction look-ahead [Keller 75], stack architectures [McKeeman 75], and dataflow machines [Dennis 75]. However, the ultimate performance of these speed-up techniques will depend greatly on good sequencing control schemes at the micro level, since each macro-level task is eventually implemented by micro cycles.

At the micro level, execution overlap is achieved by overlapping the execution of minor cycles of multiple micro cycles. As shown in Figure 1.2-9-(a), simple overlap is often used in small computer CPUs. As data path

<sup>&</sup>lt;sup>3</sup>In other words, a minor cycle corresponds to a primitive operation at the register-transfer level.

cycles overlap ((b) and (c) of Figure 1.2-9), overlap within functional units can also be used (e.g., the pipelined multiplier of the IBM 360/91). Possible places where micro-level overlap can be achieved are

- 1. between stages of the micro engine,

- 2. between the micro engine and the data path, and

- 3. between the data path stages.

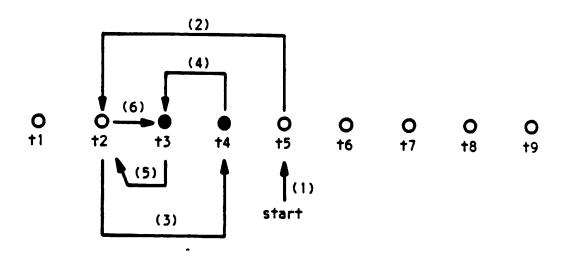

Figure 1.2-9 shows timing examples of micro cycles. Case (b) corresponds to the digital system of Figure 1.2-8, where, for a microinstruction i, the minor cycles Ii1, Ii2, Ii3 and Ii4 start by clocking  $\mu$ -PC,  $\mu$ -DR1,  $\mu$ -DR2 and Cond. Latch, respectively. As we show later, if there is no conflict in stage usage and no branches are executed, the maximum execution speed of a micro engine is determined by the longest interstage propagation delay (which is the minimum possible clock period) as in static pipelines without loops. Of course, the actual interstage propagation times depend on the number and length of the clock phases.

As shown in Figure 1.2-9, a branch delays fetch of the next micro cycle until the earliest fetch clock phase after the completion of the branch. Accordingly, the time delay due to a branch is a function of the execution time of the branch and the clock period. Thus, the overall performance of the micro engine also depends on the sequence of micro cycles to be executed.

Resource conflict and data dependency (data precedence) are other factors reducing the advantages of execution overlap. For example, two microinstructions,  $I_i$  and  $I_{i+1}$ , are executed consecutively and each has three microoperations (data path cycles), as follows:

lij : j-th minor cycle of micro cycle i.

```

111

I12

| |-----|

control

(branching)

I21

|----|

flow

I31

I32

|----|

(a) Conventional 2-stage scheme with 2-phase clock

control | I11 I12 I13 I14

| |----|---|

(branching)

I21 I22 I23 I24

|----|---|----|

I31 I32 I33 I34

|----|

(b) 4-stage scheme with 2-stage data path (needs 4-phase clock)

control | III II2 II3 II4 II5

| |----|---|--|

(branching) I21 I22 I23 I24 I25

|----|---|---|--|

I31 I32 I33 I34 I35

|----|---|--|--|

(c) 5-stage scheme with 3-stage data path (needs 5-phase clock)

```

Figure 1.2-9: Examples of micro cycle sequencing (Gantt Chart).

$$I_{i,1}: \quad C \leftarrow MDR \quad NEXT \qquad I_{i+1,1}: \quad C \leftarrow D*2 \quad NEXT$$

$$I_{i,2}: \quad A \leftarrow B + C \quad NEXT \qquad I_{i+1,2}: \quad C \leftarrow C + 2 \quad NEXT$$

$$I_{i,3}: \quad A \leftarrow A*2 \qquad \qquad I_{i+1,3}: \quad E \leftarrow C + D$$

$I_{i+1,1}$  has a data-dependency relation with  $I_{i,1}$  and  $I_{i,2}$  [Dasgupta 76]. It also has a resource conflict (assuming only one multiplier) with  $I_{i,3}$ . Thus  $I_{i+1,1}$

cannot start execution until all the data path cycles of I<sub>i</sub> complete. These situations can also be found in pipelines where a stage is used more than once during a computation of a single task [Kogge 81]. Forbidden latencies of a pipeline are determined by resource conflicts between tasks and loops are major contributors to them. These problems slow down the execution speed as well as increase the complexity of the control circuitry.

The delay of an initiation of a task due to any of these problems is called resynchronization of the pipeline, and the time overhead due to such a delay is called resynchronization overhead.

Similar problems arise at various levels of most digital designs [Ramamoorthy 77, Kartashev 82]. The higher the level, the harder the analysis and the higher the control cost. An example of a higher-level resynchronization is a page fault in a virtual memory computer system. If the page fault was for a new instruction, the pipeline must be stopped until the needed page is read in from the disk, which usually requires quite a long time compared to the speed of the pipeline.

At the micro-sequencing level, these problems can be analyzed in a formal way using a graph-theoretic, algebraic methodology, which will be discussed in this thesis.

#### 1.2.7. Definitions of the speed of digital systems

As mentioned in the previous sections, the system tasks (processes or programs) consist of sequences of macro tasks, each of which consists of one or more fixed sequences of micro cycles. Therefore, execution times of system tasks can be determined by the execution sequences of their micro cycles and the execution time of those sequences. In this sense, the execution speed of the micro engine can represent the execution speed of the system. There are

several ways of defining the execution speed of a micro engine of a digital system for performance evaluation:

- 1. maximum possible execution speed,

- 2. execution speed for certain micro cycles, and

- 3. execution speed for a (weighted) average mixture of micro cycles.

The first two parameters are not realistic since they do not involve an actual mixture of the micro cycles. The third parameter, which is an overall performance measure of the system, can be computed by assuming the average mixture of micro cycles over a long enough time period. The total estimated execution time divided by the number of micro cycles executed will be the average expected execution time of a micro cycle. Appropriate weighting functions may be used to indicate the average occurrence and/or importance of each micro cycle.

#### 1.3. Research Overview

In this thesis, we consider synthesizing high-performance digital systems with centralized control at the micro level. The main objective of the research is to achieve maximum performance with minimum hardware cost and design effort.

Among the most costly and time consuming tasks at the early stages of data path design are module selection and allocation, which select functional and storage elements and assign functions and values to them. Also, during or after the module selection and allocation phases, control is synthesized, involving the synthesis of either a microprogrammed or a hardwired sequential machine. When near optimal design is required, all these tasks are computationally intractable.

Furthermore, once all these tasks are completed, any non-trivial change in either control flow or data flow may require almost the same effort as the initial design. Naturally, we consider the following two fundamental questions:

- 1. During the module selection and allocation phases of the data path design (assuming a fixed control sequence), how can we efficiently estimate and compare the performance of alternative decisions?

- 2. For a completed design, how can we increase the performance of the system at minimum hardware cost and minimum design and/or design change time?

The main goal of this research is to develop a methodology which can answer these questions at the micro level of digital systems.

We divide the design tasks into two cases depending on the design input and design constraints as follows:

- 1. Case 1: The maximum possible performance is desired with no cost constraint.

- 2. Case 2: A cost/performance tradeoff is either forced due to the cost constraint or desired for cost and speed optimization.

#### 1.3.1. Clocking scheme synthesis for maximum execution overlap

In the first case of the design tasks mentioned above, we assume there is no resource sharing within a micro cycle in order to maximize the performance, i.e., no micro cycle is using the same module more than once. Let us consider this case now.

As mentioned in Section 1.1, the module selection and allocation phases of the design are complicated, timing consuming tasks. Also, whenever there is any change in either module selection or allocation, both the data and control flow must be altered to take maximum advantage of the change. Thus, the task will involve almost the same amount of work as the initial design. For example, if a new, faster ALU is chosen, it often requires rewriting the microprogram as well as changing the values allocated to the operand and/or result registers. This automatically involves changing the interconnections for both the data flow and control flow.

In order to avoid such costly and time consuming iterations for this task, we consider adding or reconfiguring only storage elements. This can be done without altering the basic structure of the original control and data flow and thus is considered to be transparent to the data flow and control flow analyzer. This gives the designer an efficient estimation tool for the comparison of alternative module selections and allocations.

Assuming that the control sequence of the micro cycles is fixed, we consider two basic approaches to the above problem:

- 1. For a set of allocated functional modules (for both the data path and the micro engine), add and connect the minimum number of storage elements necessary to achieve a certain level of performance.

- 2. For a completed design, add a certain number of storage elements to the data path and/or micro engine in such a way that the performance increase will be **maximized** by virtue of maximum execution overlap of the micro cycles.

In either case, we try to maximize execution overlap of the micro cycles considering the time overhead due to branches, resource conflicts and data dependency relations. Maximum execution overlap can be achieved by synthesizing an optimal clocking scheme, which involves the following tasks:

- optimal assignment, relocation, addition or deletion of the stage latches,

- choice of an optimal clock period and the number and lengths of the clock phases, and

- optimal clock signal gating and routing.

In carrying out these tasks, we formulate the problem as a graph theoretic problem. Digital circuits are modeled by directed graphs which show the pathways of the data and control flow. By properly weighting the vertices and the directed edges, we can model the execution sequences of the micro cycles as tours on the graphs. Also, the time taken by each segment of the tours can be computed easily. Assigning and/or inserting stage latches can be modeled as finding multiple-edge cut sets. Once the locations of the stage latches are determined, then the optimal clock period and clock sequence can be computed, considering the synchronization overhead discussed before. Software has been written to perform these tasks.

#### 1.3.2. Pipeline synthesis

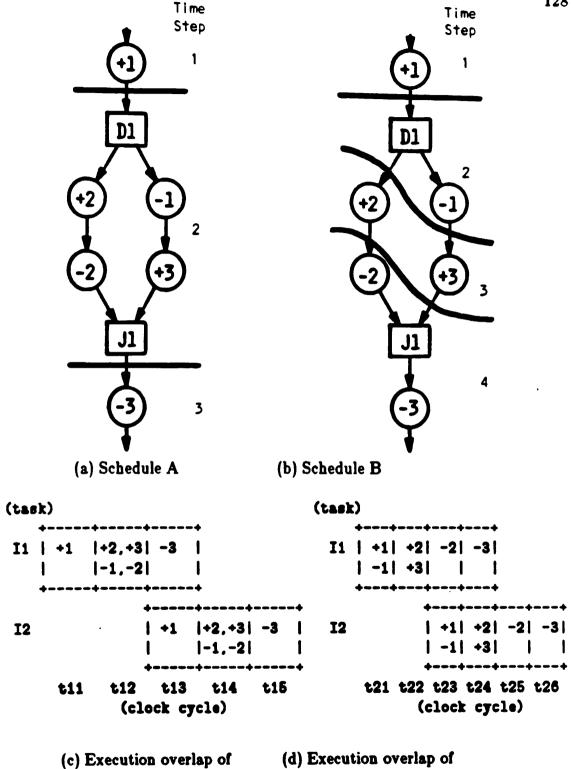

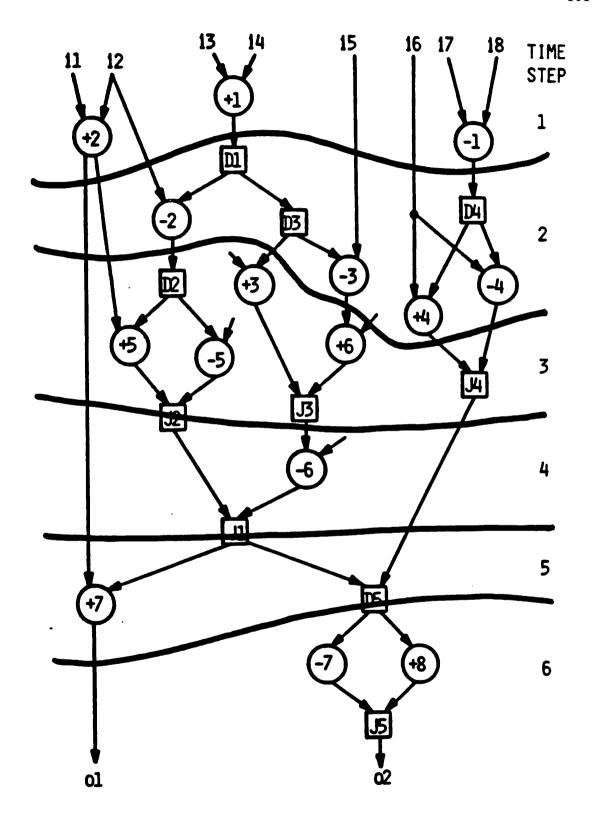

For the second type of design task described above, we must consider sharing resources, even during a micro cycle, in order to meet certain cost limits. Due to the control complexity of general execution overlap with resource sharing,<sup>4</sup> we make an assumption that a micro cycle is divided into a sequence of equal length minor cycles, which reduces the design problem to a pipeline style.

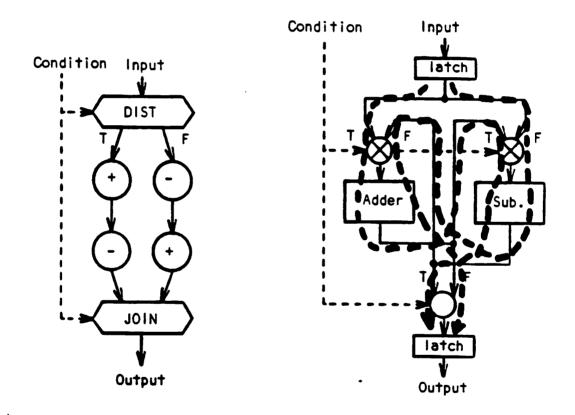

In pipelining, each unit computation task (corresponding to a micro task) is partitioned into a sequence of subtasks (corresponding to minor cycles) and each subtask is assigned to and executed during a phase or a clock cycle. Every phase has the same time period. Consecutive tasks are initiated at some fixed or variable intervals which are integer multiples of a phase and shorter than the execution time of a unit task. In this fashion, subtasks of consecutive tasks are to be executed in parallel and, in fact, consecutive tasks are to be executed overlapped in time on different parts of a circuit.

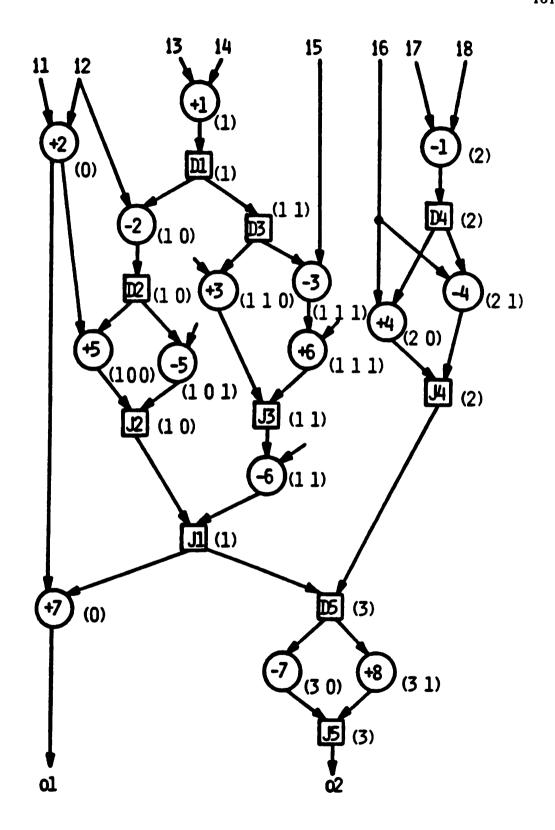

We approach the problem of pipeline synthesis from the behavioral level of design description. A data flow graph model is used to specify behavior. It can have both

- multiple disconnected graphs for parallel independent tasks, and

- conditional branches allowing modeling of more than one task in a single data flow graph.

The design inputs are the data flow graph, specifying the desired behavior of the pipeline, and design constraints on either cost or speed. We assume that module selection is done, i.e., we know that which operations or

<sup>&</sup>lt;sup>4</sup>This problem is considered to be a combination of resource-constrained scheduling and predecence constrained scheduling problems, each of which is NP-Complete [Gary 79].

types of operations are to be executed by which type of modules. The scheduling task is modeled as a graph partitioning into disconnected subgraphs, where a partitioned subgraph corresponds to a time step of the pipeline execution. The distribution of the operations in the subgraphs determines the number of functional modules and multiplexers needed. The locations of the edges separating subgraphs determine the number and locations of stage latches. The critical path of a stage determines the clock cycle of the pipeline. The number of subgraphs corresponds to the number of clock cycles for a task to complete.

The goal of the scheduling task is either

- 1. maximizing the effective performance while satisfying the cost constraint, or

- 2. minimizing the total cost while satisfying the minimum performance constraint.

For a sequence of tasks, the maximum performance of a pipeline is determined by

- 1. the minimum possible clock cycle time,

- 2. the minimum possible initiation interval between consecutive tasks, and

- 3. the number of clock cycles required to complete a task.

However, optimization tasks for these three performance parameters compete with each other. For example, partitioning the data flow graph into a smaller number of subgraphs will increase the length of the critical path in each subgraph. Due to resource sharing, longer subgraphs will have more possibility of resource conflict when they overlap. However, making the subgraphs short will increase the number of stages in the pipeline, which increases the number and cost of stage latches, as well as slows down the

execution time of a task due to the propagation delays of more stage latches. In either case, scheduling and resource allocation are constrained by either the cost or the performance constraint.

In this thesis, we present a set of fast scheduling procedures which are iterated and guided by a good optimization strategy. These procedures carry out resource allocation at the same time in order to make the schedule as feasible as possible and to maximize the performance. After scheduling is done, the actual cost is estimated by adding the cost for latches and multiplexers. The next scheduling cycle is guided by the performance and cost estimation for the previous schedule.

These procedures have been programmed and tested. Test results show that these heuristic procedures produce near-optimal schedules in most cases. These heuristic procedures have polynomial time complexity  $(O[n^2logn])$  and will be an extremely useful tool for quick design space exploration.

#### 1.3.3. Exhaustive algorithms

We also examine the possibility of using an exhaustive algorithm for an optimal scheduling of the operations while satisfying the cost constraint. This exhaustive scheduling algorithm takes the best result of polynomial-time scheduling algorithms as a good lower bound on performance to prune the search space.

Finally, we discuss another exhaustive algorithm for performance improvement of an already existing static pipeline,<sup>5</sup> by inserting non-operational delay cycles into some stages into the pipeline.

<sup>&</sup>lt;sup>5</sup>A pipeline without any conditional branches.

#### 1.4. Related Work

Since the task of high-level (functional level) digital design synthesis was launched more than a decade ago [Friedman 69, Darringer 69], there has been a vast amount of effort in automating various steps of the digital design process such as design style selection [Thomas 77, Lawson 78], data path synthesis Irani 72, Snow 78, Hafer 81, Hitchcock 83, Kowalski 83, Girczyc 84. Tseng 84, microprogram synthesis [Agerwala 76, Patterson 76, Nagle 80], and integrated design automation systems [Parker 79, Estrin 78, Zimmermann 79. Foulk 801. However, there has not been much work in the area of clocking scheme synthesis except that done for pipeline control [Cotten 65, Davidson 71, Davidson 75, Patel 76, Kogge 81] which can be considered to be a special case of general clocking scheme synthesis. As we have discussed before, the clocking scheme synthesis task is important in optimizing the speed of digital systems and must be carried out together with the data path and control design. However, it has been either buried under architectural design [Parker 79, Estrin 78, Zimmermann 79, Foulk 80, or assumed a priori, as a part of the control design [Boulaye 71, Katzan 71, Nagle 80, Andrews 80] or data path design [Hafer 81]. In some cases, clocking scheme synthesis alone is carried out for already completed designs [Davidson 75, Leiserson 82, Leiserson 83]. Among them, we will briefly discuss several which are most closely related to our research.

#### 1.4.1. Clocking scheme synthesis

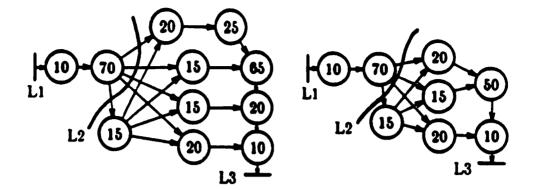

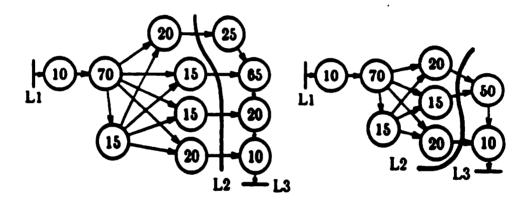

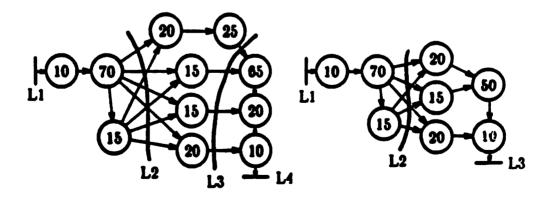

Leiserson [Leiserson 82, Leiserson 83] proposed a technique which determines a relocation of the registers in a given systolic-type data path in order to minimize the clock period. The data path is modeled as an acyclic directed graph where the vertices represent functional modules and the directed edges represent interconnections. The locations and the number of registers are indicated by the edge-weights. The basic assumption of this

technique is that all the hardware modules are performing useful operations at any time and thus all the registers are clocked at the same time by a single clock source (e.g., a systolic array). The technique moves the registers of the original design along the direction of the data flow. If the movement is to be made onto any forked<sup>6</sup> edges, registers are copied to all of the fork-edges in order not to change the original data flow. Figure 1.4-1 shows an example of step-by-step relocation of registers.

Figure 1.4-1: Leiserson's retiming.

The optimal relocation of registers is determined as the design in which the longest propagation delay between any two registers is minimized, which minimizes the clock period. The major contribution of this work is that it suggests several formal tools for timing analysis of digital circuits, which are a graph model of the digital circuit and a problem formulation using linear and/or mixed-integer linear programming. There are several shortcomings of this technique to be used in the general case of digital systems speed-up. They are

• the technique assumes fixed clocking for all the registers at the same time,

<sup>&</sup>lt;sup>6</sup>In this model, all the forks are AND forks since every hardware module is performing useful operations and thus all the interconnections are carrying useful data values.

- the technique assumes fixed data flow for all time,

- control hardware timing is not considered, and

- register propagation delays are ignored.

Also, this technique does not handle execution overlap between multiple computation tasks. In Chapter 4, we will show an example of how the clock period can be reduced further by using execution overlap.

Boulaye [Boulaye 71] discusses speeding up pipelined micro engines by minimizing the time overhead caused by the conditional branches, which is accomplished by clocking the condition latch (which contains values that determine selection of the next microinstruction) as early as possible. This approach can also be considered as relocation of registers to reduce the critical path or the critical stage of a pipeline. However, if the propagation delays of both the data path stages and the stages of the micro engine are not considered together, optimal relocation cannot be determined. Also, in an instruction pipeline, branches cause resynchronization overhead, which also involves the termination and re-initiation of the data path stages.

Andrews [Andrews 80] considers using multiphase clocking as one way of reducing the number of microinstruction fetches from slow microcode storage. By using a multiphase clock, microinstructions can be horizontally coded and executed serially in several clock phases without having an expensive data path. As he mentions, the performance of this technique depends on the coding efficiency of the horizontal microprogram. If the microinstructions are sparsely coded, then the resource utilization efficiency will be low. Also, after the completion of a microinstruction which has only microoperations with short execution times, there will be idle time until the fetch cycle of the next microinstruction. This is true for any microprogram (vertical or horizontal) if execution overlap is not used. However, if execution overlap is used, this is not

always true, since the execution speed of the micro engine depends much more on the longest microoperation execution time rather than the total execution time span of each of the microinstructions. Moreover, as we shall show in Chapter 3, if execution overlap is properly used, vertically coded microinstructions can be executed as fast as horizontally coded ones. This saves a significant amount of design time and avoids the complexity of horizontal microprogram compaction, which is known to be intractable [Horowitz 78, Robertson 79].

As another approach, Berg [Berg 79] characterized the timing behavior of a given control and clocking scheme in order to provide a guideline for the synthesis of a fast and correct microprogram. The timing behavior of a controller at the macro level is modeled as a finite state machine. The model allows multiphase execution of micro-instructions. However, the model is focused on timing the interactions between main system blocks such as the CPU, main memory, and I/O controller.

#### 1.4.2. Pipeline clocking schemes

Basic timing requirements and clock skew problems for pipelines were first analyzed by [Cotten 65], and well explained in [Kogge 81]. If the shortest path through a stage is shorter than the width of a clock pulse, then the output of a latch can change the input of the next stage latch while the clock pulse is active, which is termed a *critical race* by [Cotten 65]. There are four solutions to the critical race problem:

- 1. the short paths which might cause critical races must be augmented by time-delaying and doing-nothing circuits [Cotten 65],

- 2. the width of the clock pulse must be reduced by using a faster latch.

- 3. master-slave flip-flops must be used, or

#### 4. edge-triggered flip-flops must be used.

A recent work by [Unger 83] at IBM discusses the third and forth solution approaches. In brief, master-slave and edge-triggered types of latches/flip-flops are race-free themselves and therefore can prevent critical races.

Another problem, called clock skew, must be considered in order to get the right timing, and cannot be avoided even with master-slave or edge-triggered flip-flops. In real designs of a pipeline, stages are physically apart from each other. Different interconnection lines carrying the clock signal have different lengths and loading effects causing different transmission delays. Also, clock signal drivers have different delay times depending on the size. Due to all these factors, the arrival times of the clock signal to different stages are not the same. This may cause latching wrong results by clocking latches either too early or too late. The maximum difference of any two clock signal arrival times is called clock skew. A solution to the critical race problem due to clock skew has been proposed by [Cotten 65]. It uses a chain of clock pulses to clock the latches in sequence instead of clocking all the latches at the same time with a single clock source.

All the timing issues we have discussed in this section are critical to pipeline design at the gate level, where delay times of the latches are comparable to the stage logic block delays. Although the basic problems remain the same, however, in the case of pipelined designs at the functional module (e.g. a 4-bit adder, an ALU, etc.) level or register-transfer level, these issues have relatively little importance compared to partitioning the circuit into stages and scheduling computation tasks on the pipeline.

#### 1.4.3. Pipeline scheduling

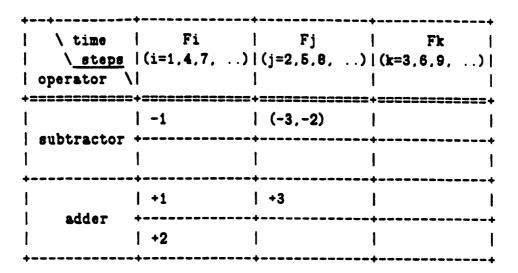

The pipeline scheduling problem has been studied by several researchers. In general, most scheduling problems (e.g. job shop scheduling, flow shop scheduling, etc.) have been known to be NP-Complete or NP-hard [Baker 74, Horowitz 78, Gary 79]. Ramamoorthy and Li [Ramamoorthy 75] have shown that the general pipeline scheduling problem is also NP-Complete. Some engineering solution techniques for pipeline scheduling have been developed in a series of papers, [Davidson 71, Shar 72, Davidson 75, Patel 76]. We summarize the common characteristics of these techniques.

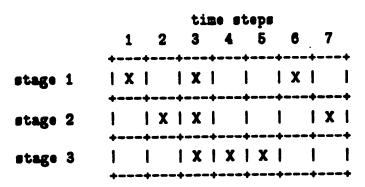

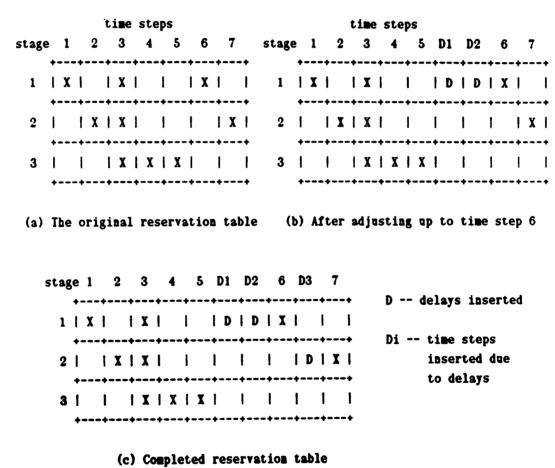

The basic tool for schedule analysis is the reservation table developed by Davidson [Davidson 71]. A reservation table is a two-dimensional tabular description of the pattern and sequence of stage usage of a computation task. Each column corresponds to a time step and each row corresponds to a stage. Resource conflicts or collisions between any two consecutive computation tasks can be detected by superposing their reservations. The goal of the scheduling task is to find out an optimal sequence of initiation intervals for a sequence of computation tasks such that the average initiation interval is minimized.

The lower bound on the average initiation interval for a reservation was computed by Shar [Shar 72], and is equal to the maximum number of marks in a single row in terms of the number of time steps. However, there is no guarantee that the lower bound can be achieved, depending on the pattern of the reservation table. The reason is that the desirable small initiation intervals may not always be permissible due to collision. Another situation that possibly makes the average initiation interval longer than the lower bound is when an already existing pipeline is asked to perform a new type of computation. The new type of task may have very much different stage usage, which may increase the average initiation interval. In such a case the designer has little

control over the reservation table of the new type of task. A solution technique to these problems has been reported by Patel [Patel 76]. The solution technique selectively delays some of the marks in each row of the reservation table. The number of marks in each row is not changed. One column delay of a mark corresponds to a delay of a time step. In brief, the marks in each row is relocated such that a certain desired sequence of initiation intervals does not cause any collision.

The actual implementation of a delay step can be either (i) a real empty stage with only stage latches or (ii) skipping clock phases, depending on whether buffering (saving) the inputs for the delayed computation is necessary. In other words, if the latches storing the input values for a delayed computation are not overwritten by some other computation step, there is no need to pipe the values through any other storage elements.

All the pipeline scheduling techniques we have discussed in this section assume the following three restrictions:

- Partial sharing of a stage (substaging of a stage) is not allowed.

- The execution time for all stages is fixed and the same.

- No conditional selection of stages is allowed during the execution of any computation (i.e. the sequence of stage usage of any task is always fixed).

These restrictions constitute the major differences between the general execution overlap problem we are studying and the traditional pipelining problem discussed above. The third restriction, especially, prevents the usage of these synthesized pipelines in general-purpose digital systems such as a computer CPU or a digital controller. Also, the first restriction makes the cost-speed tradeoff of pipeline designs rigid and leaves little freedom. In Chapters 4 and 5, we will discuss how we can remove the first and third restrictions.

#### 1.4.4. Other related work

The basic concept of execution overlap at the micro-level under a centralized control originates from the look-ahead technique [Keller 75] for the prefetch of instructions and operands. Examples of machines which implement macro level execution overlap include the CDC6600, and the IBM 360/91, 195 and 370/165. They assume that instruction fetch, decode, and execute cycles, each consisting of a sequence of micro cycles, take almost equal time, which is the basic assumption of general pipelines. Possible execution overlap is predicted by checking the type and execution status of the current macro task being executed. Typical checking mechanisms use condition flags and/or counters which represent the state of associated resources. Naturally, look-ahead techniques assume flexible execution control mechanisms implemented by micro-level sequencing primitives [Katzan 71]. However, at the micro level, implementing look-ahead is costly and difficult since the look-ahead mechanism must be much faster than the micro cycle time in order to achieve execution overlap, which, in most cases, requires hardware level primitives.