# PARALLEL COMPUTING WITH OPTICAL INTERCONNECTS by Mehrnoosh Mary Eshaghian Technical Report No. CENG 89-02

A Dissertation Presented to the FACULTY OF THE GRADUATE SCHOOL UNIVERSITY OF SOUTHERN CALIFORNIA In Partial Fulfillment of the Requirements for the Degree DOCTOR OF PHILOSOPHY (Computer Engineering)

December 1988

Copyright 1988 by Mehrnoosh Mary Eshaghian

## UNIVERSITY OF SOUTHERN CALIFORNIA THE GRADUATE SCHOOL UNIVERSITY PARK LOS ANGELES, CALIFORNIA 90089

| This dissertation, written by                  |

|------------------------------------------------|

| Mehrnoosh Mary Eshaghian                       |

| under the direction of h.e.r Dissertation      |

| Committee, and approved by all its members,    |

| has been presented to and accepted by The      |

| Graduate School, in partial fulfillment of re- |

| quirements for the degree of                   |

| DOCTOR OF PHILOSOPHY                           |

| Barbara Selomon                                |

| / /                                            |

| Dean of Graduate Studies                       |

| December 15, 1988                              |

| DateDecember 15, 1988                          |

| DISSERTATION COMMITTEE                         |

| 0                                              |

| V- U. Presama Climar                           |

| Chairperson                                    |

| Hay I milh                                     |

| B Xix lex                                      |

| 0 = 6 0 = 1                                    |

| B. Kirl Jili<br>Javing S. asad                 |

|                                                |

$To\ my\ parents$

## Table of Contents

| Lı | st of | Figures                          | viii |

|----|-------|----------------------------------|------|

| Li | st of | Tables                           | ix   |

| A۱ | ostra | ct                               | x    |

| Ι  | Ba    | ackground                        | 1    |

| 1  | Intr  | oduction                         | 2    |

|    | 1.1   | VLSI Interconnection topologies  | 3    |

|    | 1.2   | Optical Interconnection Networks | 5    |

|    | 1.3   | Summary of Results               | 7    |

| 2  | Opt   | ics and VLSI                     | 9    |

|    | 2.1   | Preliminaries                    | 10   |

|    | 2.2   | Photonic Fundamentals            | 12   |

|    | 2.3   | Why Optics in VLSI               | 15   |

|    | 2.4   | Transmitting Channels            | 16   |

|    |       | 2.4.1 Fiber Optics               | 16   |

|    |       |                                  |      |

|    |     | 2.4.2  | Free Space Interconnects                                 | 18  |

|----|-----|--------|----------------------------------------------------------|-----|

|    | 2.5 | Gratin | ıg                                                       | 19  |

|    |     | 2.5.1  | Acousto-Optical Elements                                 | 21  |

|    |     | 2.5.2  | Holographic Optical Elements                             | 22  |

|    | 2.6 | Source | es                                                       | 25  |

|    |     | 2.6.1  | Laser Diodes                                             | 25  |

|    |     | 2.6.2  | Light Emitting Diodes                                    | 26  |

|    | 2.7 | Detect | ors                                                      | 26  |

|    | 2.8 | Semice | onductor Integration                                     | 27  |

|    |     | 2.8.1  | Silicon Substrate                                        | 27  |

|    |     | 2.8.2  | Gallium Arsenide                                         | 28  |

|    |     | 2.8.3  | Hybrid Integration                                       | 28  |

|    | 2.9 | Limita | ations                                                   | 29  |

|    |     |        |                                                          |     |

| II | C   | ompi   | utational Models                                         | 30  |

| •  | 0 1 | . 134  |                                                          | 0.1 |

| 3  |     |        | lodels of Computation                                    | 31  |

|    | 3.1 | Lower  | bounds                                                   | 32  |

|    |     | 3.1.1  | An Optical Model                                         | 32  |

|    |     | 3.1.2  | Optical Volume, VLSI Area and 1-way Information Transfer | 36  |

|    |     | 3.1.3  | Lower bounds On Optical Volume For Image Convolution     | 41  |

|    | 3.2 | Upper  | bounds                                                   | 43  |

|    |     | 3.2.1  | Optical Mesh Using Mirrors                               | 44  |

|    |     | 3.2.2  | Reconfiguration Using Acousto-Optic Devices              | 46  |

|         |                    | 3.2.3 Electro Optical Crossbar                                                                                                                                                               | 47                                     |

|---------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|         | 3.3                | Performance Issues                                                                                                                                                                           | 48                                     |

|         |                    | 3.3.1 Connectivity                                                                                                                                                                           | 50                                     |

|         |                    | 3.3.2 Size                                                                                                                                                                                   | 50                                     |

|         |                    | 3.3.3 Speed                                                                                                                                                                                  | 51                                     |

|         |                    | 3.3.4 Power and Energy                                                                                                                                                                       | 52                                     |

|         |                    | 3.3.5 Cost                                                                                                                                                                                   | 52                                     |

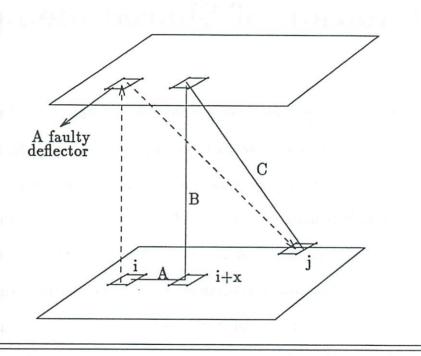

|         |                    | 3.3.6 Fault Tolerance                                                                                                                                                                        | 53                                     |

| 4       | C:                 | ulation of Chanad mamony                                                                                                                                                                     | ==                                     |

| 4       | Sim                | ulation of Shared memory                                                                                                                                                                     | 55                                     |

|         | 4.1                | Deterministic Simulation                                                                                                                                                                     | 57                                     |

|         | 4.2                | Probabilistic Simulation                                                                                                                                                                     | 59                                     |

|         | 1.2                |                                                                                                                                                                                              |                                        |

|         | 1.2                |                                                                                                                                                                                              |                                        |

| II      |                    | 2 11.                                                                                                                                                                                        | 64                                     |

| II      |                    |                                                                                                                                                                                              |                                        |

| II<br>5 | I.                 |                                                                                                                                                                                              |                                        |

|         | I.                 | Applications                                                                                                                                                                                 | 64                                     |

|         | I .                | Applications  nal and Image Processing                                                                                                                                                       | 64<br>65                               |

|         | Sign               | Applications  nal and Image Processing  Optical Mesh and EREW Algorithms                                                                                                                     | <b>64 65</b> 66                        |

|         | Sign               | Applications  nal and Image Processing  Optical Mesh and EREW Algorithms                                                                                                                     | <b>64 65 66 69</b>                     |

|         | Sign               | Applications  That and Image Processing  Optical Mesh and EREW Algorithms  Optimal Geometric Algorithms  5.2.1 Labeling Digitized Images                                                     | 64<br>65<br>66<br>69<br>70             |

|         | Sign               | Applications  That and Image Processing  Optical Mesh and EREW Algorithms  Optimal Geometric Algorithms  5.2.1 Labeling Digitized Images  5.2.2 Convexity Algorithms                         | 64<br>65<br>66<br>69<br>70<br>74       |

|         | Sign<br>5.1<br>5.2 | Applications  nal and Image Processing  Optical Mesh and EREW Algorithms  Optimal Geometric Algorithms  5.2.1 Labeling Digitized Images  5.2.2 Convexity Algorithms  5.2.3 Distance Problems | 64<br>65<br>66<br>69<br>70<br>74<br>76 |

| 6 | Nor   | Von !   | Neumann Computations             |     | 83   |

|---|-------|---------|----------------------------------|-----|------|

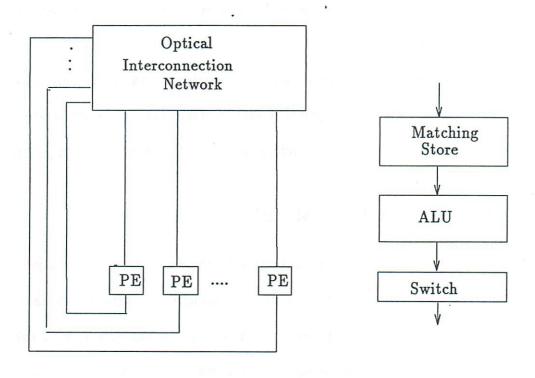

|   | 6.1   | Imple   | mentation of Neural Networks     |     | . 84 |

|   |       | 6.1.1   | Interconnectivity in Neural Nets |     | . 85 |

|   |       | 6.1.2   | Operation                        |     | . 85 |

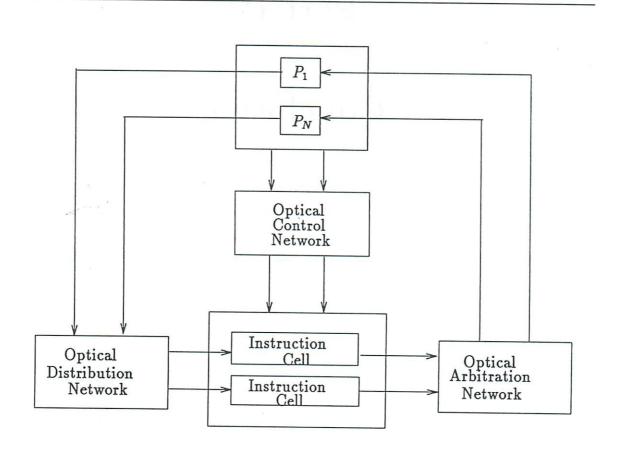

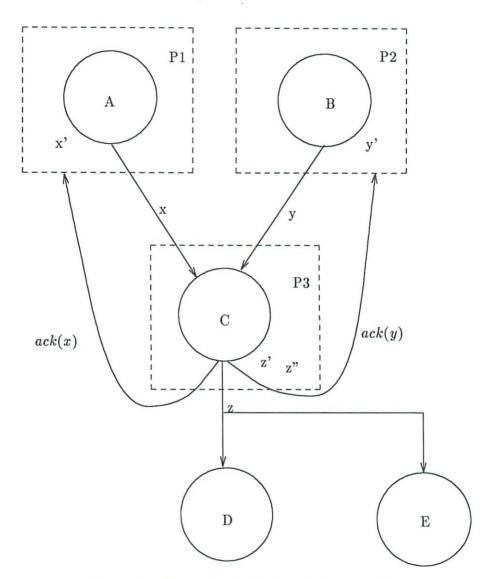

|   | 6.2   | Imple   | mentation of Data Flow Networks  |     | . 87 |

|   |       | 6.2.1   | Irvine Data Flow Machine         |     | . 88 |

|   |       | 6.2.2   | MIT Data Flow Computer           | • • | . 89 |

| r | V (   | Concl   | lusion                           |     | 91   |

| 7 | Cor   | ıclusio | n                                |     | 92   |

| A | .ppe  | ndixe   | es                               |     | 94   |

| В | iblio | ograp   | hy                               |     | 103  |

## List of Figures

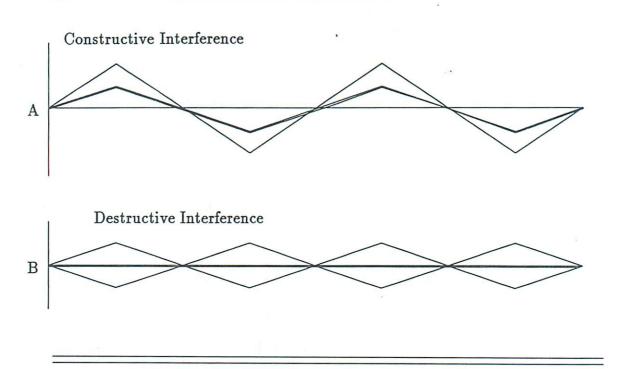

| 2.1 | Interference between two waves                                       | 13 |

|-----|----------------------------------------------------------------------|----|

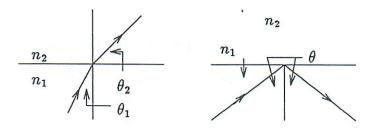

| 2.2 | Refraction of rays                                                   | 17 |

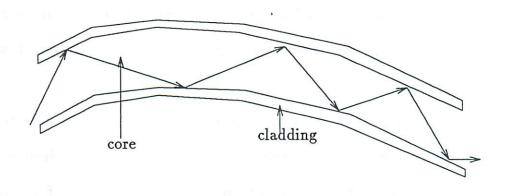

| 2.3 | Light advance within an optical fiber                                | 18 |

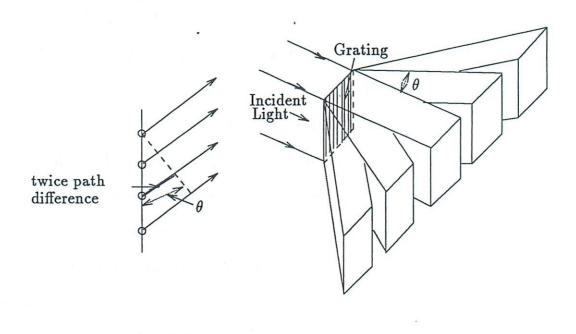

| 2.4 | Bragg Diffraction                                                    | 21 |

| 2.5 | A holographic interconnection element                                | 23 |

| 2.6 | A possible holographic configuration                                 | 24 |

| 3.1 | Optical Model of Computation                                         | 35 |

| 3.2 | 1-way information transfer                                           | 39 |

| 3.3 | The computational parallelepiped P                                   | 40 |

| 3.4 | Environment for computing image convolution                          | 42 |

| 3.5 | (a) The input and output partition for scanline case. (b) A kernel . | 43 |

| 3.6 | An Optical mesh using mirrors                                        | 45 |

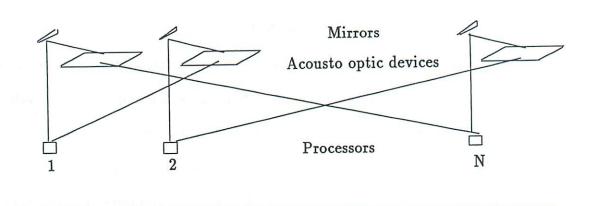

| 3.7 | Reconfiguration using acousto-optic Devices                          | 47 |

| 3.8 | Reconfiguration using an electro optical crossbar                    | 49 |

| 3.9 | A Fault tolerant scheme                                              | 54 |

| 4.1 | Worst input sequence                                                 | 58 |

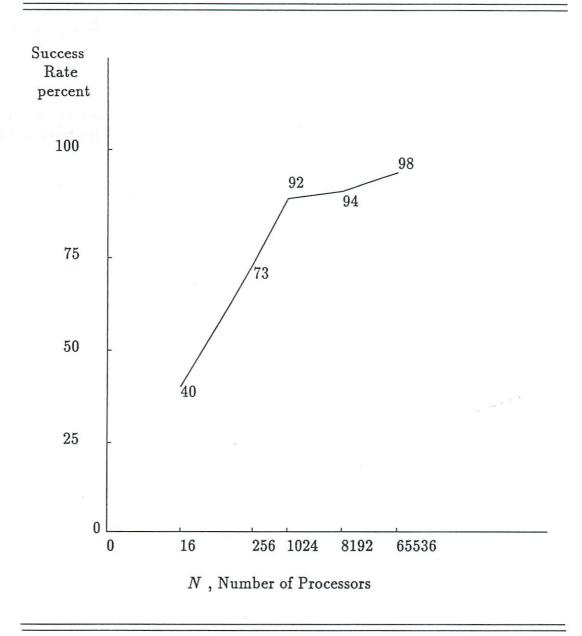

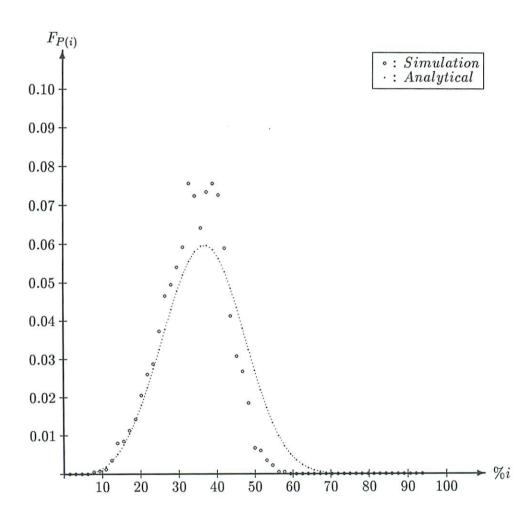

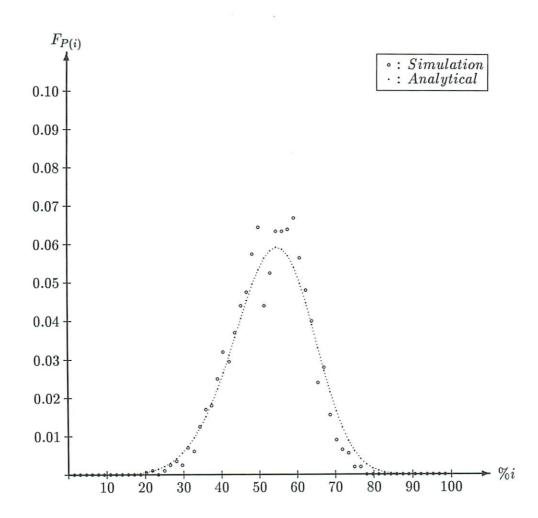

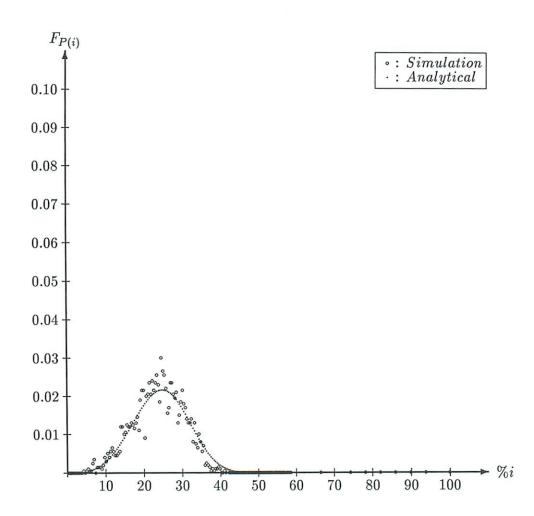

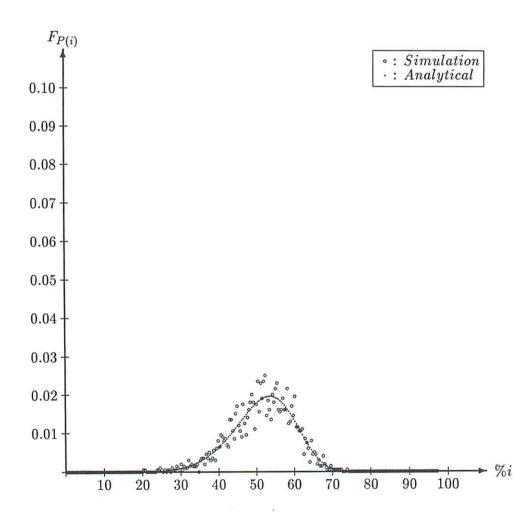

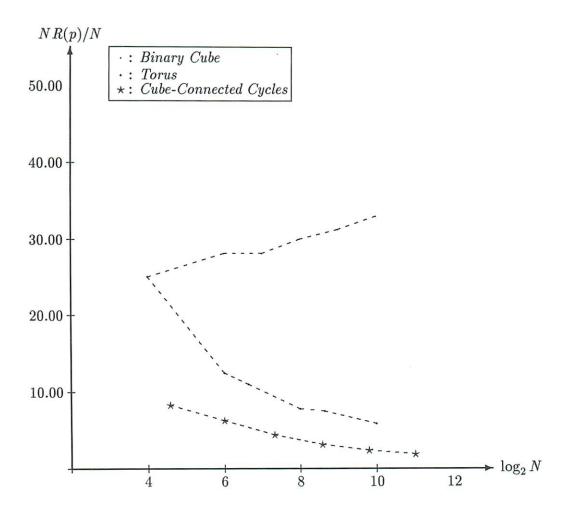

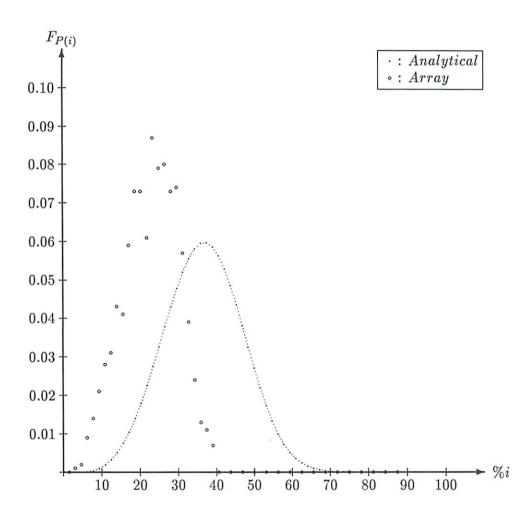

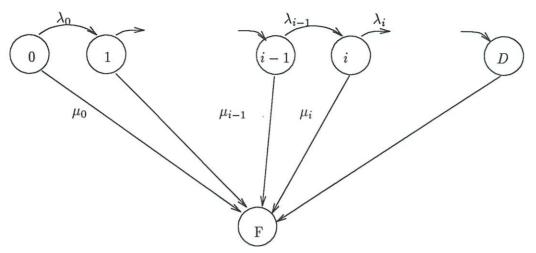

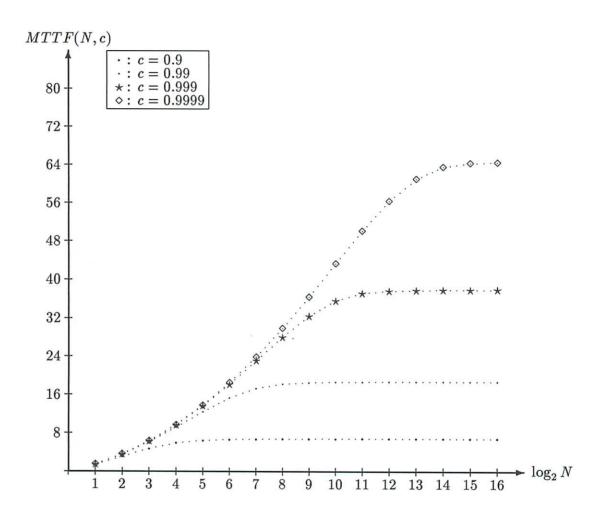

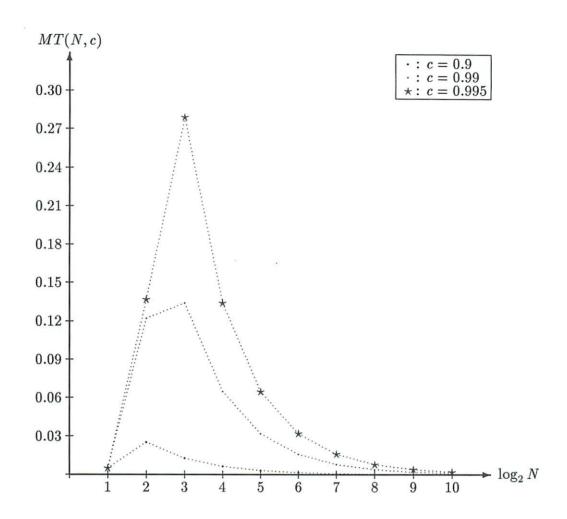

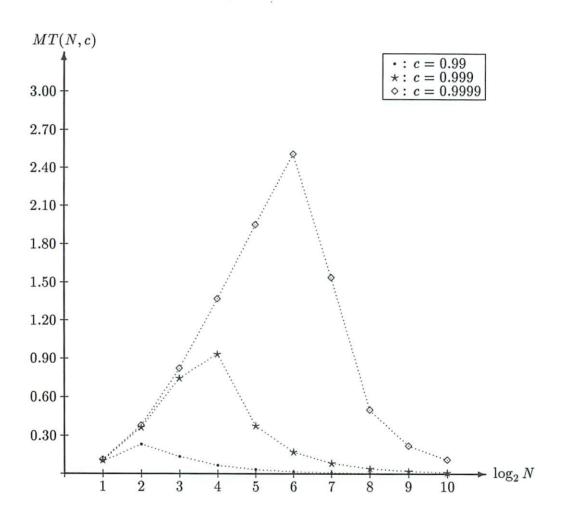

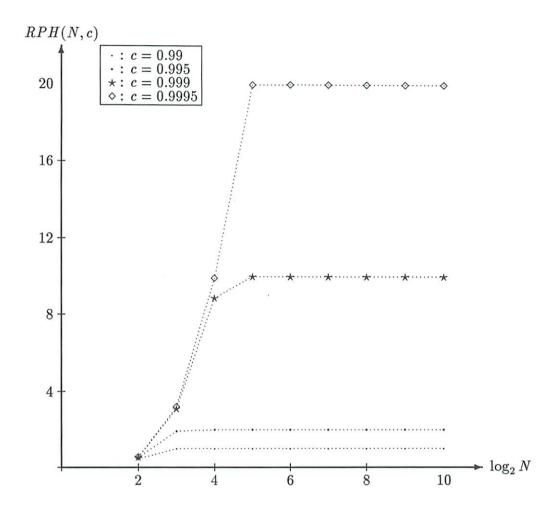

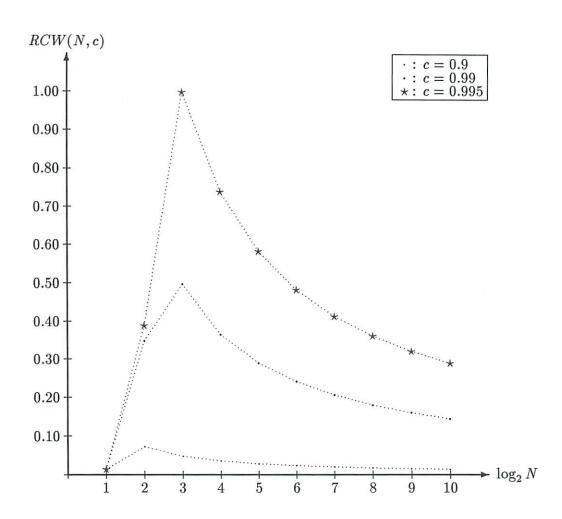

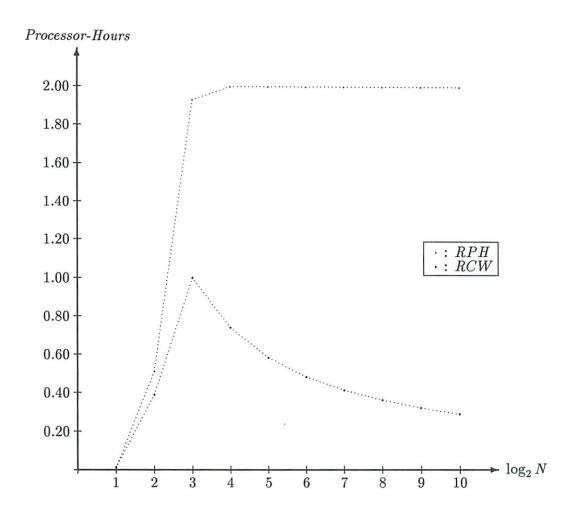

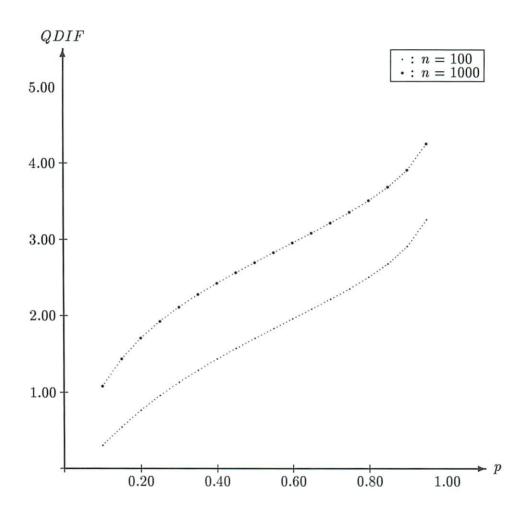

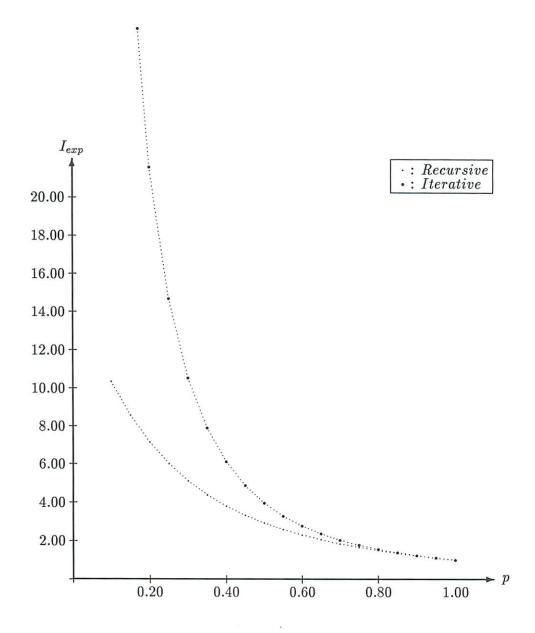

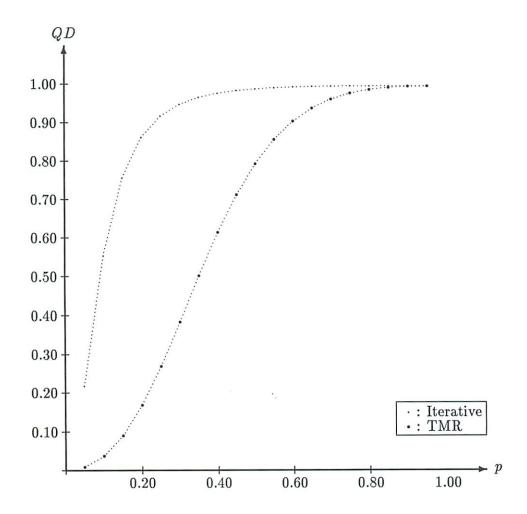

| 4.2 | Simulation results                         | 62 |

|-----|--------------------------------------------|----|

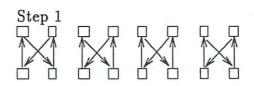

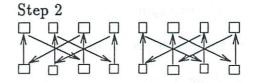

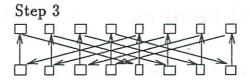

| 5.1 | Matrix transpose                           | 67 |

| 5.2 | Communication pattern for FFT computation  | 68 |

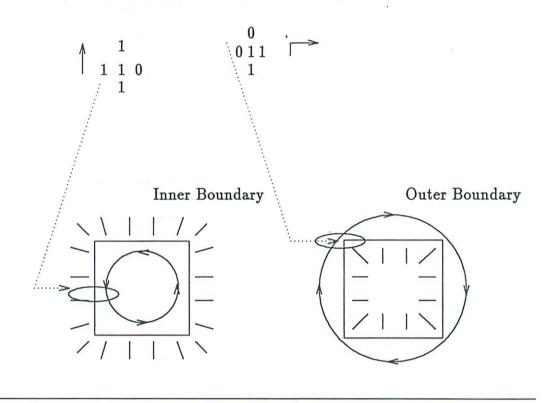

| 5.3 | Boundary rules                             | 71 |

| 5.4 | Pointer jumping                            | 72 |

| 5.5 | Merging of blocks and processor assignment | 73 |

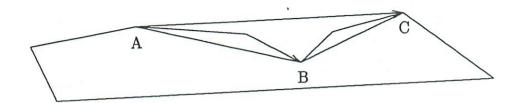

| 5.6 | Proof of correctness                       | 75 |

|     |                                            |    |

| 6.1 | An implementation of a neural network      | 86 |

| 6.2 | An enhanced Irvine data flow machine       | 89 |

| 6.3 | An enhanced MIT data flow machine          | 90 |

## List of Tables

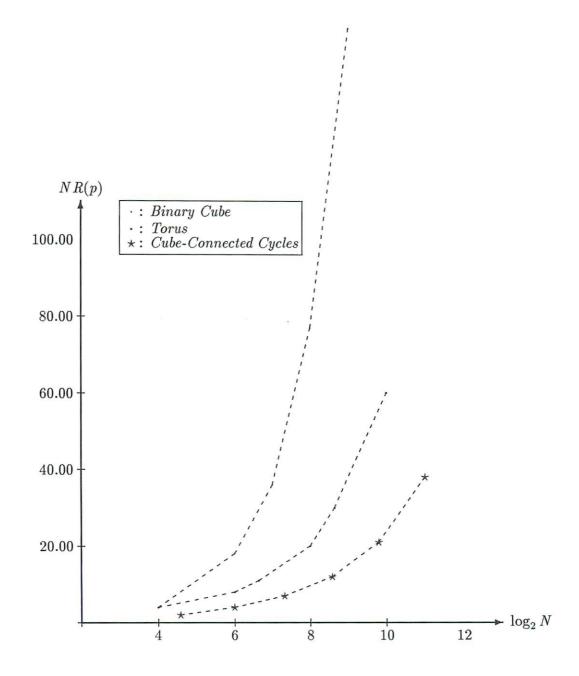

| 5.1 Comparison of computi | ng times   | • • • • • • • • • • • • • • • • • • • • | 82    |

|---------------------------|------------|-----------------------------------------|-------|

|                           |            |                                         |       |

|                           |            | , to the                                |       |

|                           | j. 20 - 30 |                                         |       |

|                           |            |                                         |       |

|                           |            |                                         |       |

|                           |            |                                         |       |

| and to Ohe a following    |            |                                         |       |

|                           |            |                                         |       |

|                           |            |                                         |       |

|                           |            |                                         |       |

|                           |            |                                         | , 201 |

|                           |            |                                         |       |

|                           |            |                                         |       |

|                           |            |                                         |       |

|                           |            |                                         |       |

#### Abstract

Optics has become an appealing alternative to wired interconnection on several levels of communication hierarchy within computing systems. Optical chip interconnections, unlike electrical, are insensitive to mutual interference effects, are free from capacitive loading and planar constraints, and can be reprogrammable. A major goal of this thesis is to understand the computational limits in using optical communication technology in VLSI parallel processing systems. Established methodologies for studying computational complexity are applied to obtain measures that reflect true implementation costs.

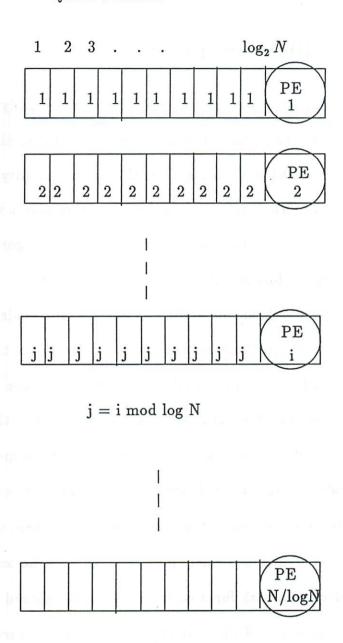

The computational lower bounds derived using the VLSI model of computation indicate that solution to communication-intensive problems requires either a large amount of chip area or time, both of which are costly. The first part of the thesis introduces an Optical Model of Computation (OMC) that uses free space optics as a means of interprocessor communication; thus reducing chip costs. The model allows unit cost communications, and can simulate one step of PRAM with no loss in time when the number of memory locations is equal to the number of processors. Reducing the number of processors by a factor of  $O(\log N)$ , simple algorithms are presented that run in  $O(\log N \log \log N)$  time with a high probability, and in  $O(\log^2 N)$  time deterministically.

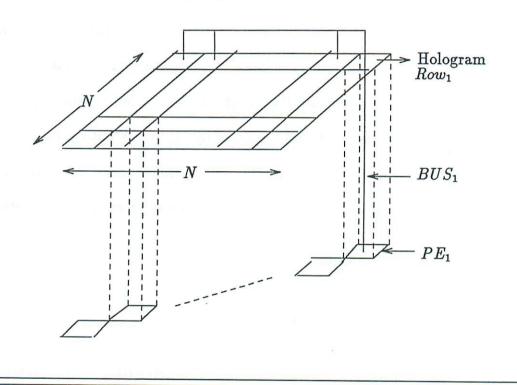

Since OMC uses the space above and around chips for interconnects, OMC can be compared with three dimensional VLSI models in computational complexity. Any computation performed by a three dimensional VLSI organization having N processors with degree d, in time T, and volume V can be performed on OMC in volume v, and time t, where  $dT/N \leq t \leq T$ , and  $Nd \leq v$ . The thesis presents various parallel architectures as possible efficient upper bounds for v. Each one is designed to reflect the capabilities and limitations of the device technologies used for the redirection of optical beams. For example, an acousto-optic device, for which the redirecting capability is usually limited to only one dimension, is used to interconnect a linear array of processors. Holograms are used to realize a unit delay electro-optical crossbar. The crossbar's switching speed is in the order of nano-seconds.

Having developed the computational models, the thesis next focuses on applications in image processing and the implementation of AI problem solving techniques. A set of  $O(\log N)$  pointer based algorithms for finding geometric properties of digitized images on an electro-optical mesh is introduced. The algorithms include optimal solutions for identifying and labeling figures, computing convexity properties, determining distances, etc. Another application is in the implementation of neural networks using a general purpose electro-optical cross-bar which has the potential to interconnect each of the neurons to all the others. This architecture can be modified to operate asynchronously and to realize the data-flow model.

Part I

Background

## Chapter 1

## Introduction

Speedups due to technological advances in solid state electronic design are reaching theoretical limits. To get around these limits, researchers have considered concurrent processing of data as a promising alternative for achieving speedups proportional to the level of concurrency. During the past decade, many multiprocessor architectures have been proposed to obtain such speedups. However, the desired speedups have not been realized because of a limited understanding of issues in designing efficient parallel algorithms and in designing interconnection networks and their interactions. Recently, many parallel algorithms have been designed based on a theoretical shared memory model, the Parallel Random Access Machine (PRAM) [124], in which a unit-delay interconnection network is assumed.

In practice, interconnection networks introduce a delay factor in the implementation of parallel algorithms. The main issues in the design of such interconnection networks have been routing delay, communication bandwidth, hardware cost, and ease of control. Traditionally electronic interconnects have been used. However, with advances in optical technology, it is likely that photonics will play an important role in parallel computation. This thesis focuses on possible realizations of unit-time interconnection network using free space optics.

## 1.1 VLSI Interconnection topologies

Research in the design of interconnection networks can be divided into two topological classes: static and dynamic[34]. In a static network, links between any two processors are passive and direct connections cannot be reconfigured between processors. In a dynamic network, links can be reconfigured by setting the switching elements in the network. Among many static topologies, those having small diameter are most attractive since the diameter of an architecture represents a lower bound on worst case communication delay between any two processors. A fully connected network has unit diameter. However, when implemented in electronic technology such as VLSI, its diameter becomes  $\Omega(\log N)$  due to pinout limitations of processors. Also, the VLSI layout area becomes too large to be practically implemented. Therefore, an appropriate alternative is to consider area efficient architectures which have  $O(\log N)$  communication delay. Pyramid and Mesh of Trees are examples of such architectures [84, 71, 74]. Because of communication bandwidth constraints, simulation of some PRAM algorithms on

<sup>&</sup>lt;sup>2</sup>A function f(n) is said to be  $\Omega(g(n))$  if there exist positive constants  $n_0$  and c such that  $f(n) \geq c \cdot g(n)$ , for all  $n > n_0$ .

<sup>&</sup>lt;sup>3</sup>A function f(n) is said to be O(g(n)) if there exist positive constants c and  $n_0$  such that for all  $n \ge n_0$ ,  $f(n) \le c \cdot g(n)$ .

these two architectures can lead to significant loss in time performance.

Dynamic networks are categorized in three topological classes: single-stage, multistage, and crossbar[34]. The switches in an  $N \times N$  crossbar can be set in  $O(\log N)$  time so that every input port can be connected to a free output port. However, an N input crossbar requires  $\Omega(N^2)$  VLSI area, using the usual two dimensional VLSI model [113]. Several N input N output multistage networks are known which require  $O(N \log N)$  switching elements; significantly fewer than a crossbar network [107]. Multistage networks can be divided into two major classes: rearrangeable and non-rearrangeable [10]. Non-rearrangeable networks can realize only a proper subset of all permutations. A Butterfly network is a widely used non-rearrangeable network. It has been shown that an arbitrary permutation can be realized by the butterfly network in  $O(\log N)$  time, with a high probability [118].

Rearrangeable networks support any arbitrary permutation using appropriate switch settings. However, finding a switch setting to realize a permutation on a rearrangeable network can be time consuming; for example it can take as much as  $O(\log^4 N)$  time using cube connected computer or a perfect shuffle computer with N processors [79]. Also, their layout area in the two-dimensional VLSI model, is not significantly superior compared to the area requirement of the N input crossbar. In fact, the well known omega network which is a non-rearrangeble multistage network and has  $O(N \log N)$  switching elements, requires  $\Omega(N^2/\log^2 N)$  VLSI area [71]. Therefore, realizing multistage interconnection networks in  $O(N \log N)$  area does not seem possible unless one assumes that wires do not occupy any area, or if free space optical beams are used as a means

of interconnection.

In this thesis, we study parallel architectures that use free space optics as a means of interprocessor communications. Replacing electrical interconnects with optical beams has a significant impact on the performance of VLSI architectures [19, 47]. This fact arises from the following two important properties of free space optics. First, free space optical beams can cross each other without any interference. Secondly, the connections need not be fixed and can be redirected [12]. Therefore, using optical interconnects, one can design bounded degree VLSI architectures that can simulate a unit delay interconnection network.

## 1.2 Optical Interconnection Networks

A considerable amount of research has been done on replacing wires with optical waveguides on a VLSI chip [36, 48]. Since such an approach does not change the computational power of the classical VLSI model, it is outside the focus of our thesis. However, it is worthwhile to know that these techniques can be used in a finer level of integration, such as in the design of processing elements. Some of engineering merits of this approach are discussed in the following chapter.

Unique qualities of the optical medium are its abilities to be directed for propagation in free space and to have two optical channels cross in space with out interaction. These properties allow optical interconnects to utilize all three dimensions of space. The ultimate goal of reconfigurable interconnects is to be able to change the interconnect matrix as quickly and as freely as needd. Such a capability will allow optical interconnection to improve upon many of

the functions presently implemented on a limited scale with electronics, such as routing data between processing elements based on data dependent decisions, and multiplexing and demultiplexing information.

One of the first attempts in using free space optics as a means of datacommunications was [43]. In their hybrid GaAs/Si approach to data communication, a GaAs chip with optical sources was connected in a hybrid fashion

(with conventional wire bond techniques) to a Si chip such that light was generated only along the edges of the Si chip. The sources were of the edge-emitting

or surface emitting type. The optical signals were routed to the appropriate locations on the Si chip using conventional and or holographic optical elements. The

Si chip contained detectors to receive the optical data streams generated by the

sources. Since the detector-amplifier combinations were fabricated in Si, every

computational component on the Si chip was capable of receiving data.

To explore this promising concept, it was extended to support efficient interconnection networks for massively parallel computing. One of the most recent contributions was [101]. In that, Sawchuck et al. described several possible bulk optical systems for implementing crossbar networks. Unlike the electrical crossbar, these crossbars provided unit time interconnectivity and had a slow switching rate. In this thesis, we propose a class of free space interconnection networks with unit time delay. The proposed crossbar has a switching time in an order of nanoseconds and is implementable with current technology.

## 1.3 Summary of Results

Part II concentrates on the proposed computational models. In chapter 3, an Optical Model of Computation (OMC) is presented along with its computational lower bounds for solving problems. This model uses the space above and around chips for interconnects, which makes it comparable to three dimensional VLSI models. Any computation performed by a three dimensional VLSI organization having N processors with degree d, in time T, and volume V can be performed on OMC in volume v, and time t, where  $dT/N \leq t \leq T$ , and  $Nd \leq v$ . Various parallel architectures are presented as possible efficient upper bounds for v. Each one is designed to reflect the capabilities and limitations of the device technologies used for the redirection of optical beams. A direct implementation of OMC is possible with an optical mesh using mirrors. A faster architecture will be found in an optical array using acoustic optic devices with broadcasting capability. A considerably less expensive and currently implementable design is the electro optical crossbar, which has a reconfiguration time in the order of nanoseconds.

The relationships to shared memory models and simulation algorithms are shown in chapter 4. A model of parallel computation motivated by the properties of free space optical interconnects is studied. In this model unit cost communication is possible, however there is a bottleneck in accessing memory modules. We will present a simple deterministic algorithm for efficient accessing of these memory modules. This algorithm simulates one step of an N processor EREW PRAM in  $O(\log^2 N)$  time, and its probabilistic version has  $O(\log N \log \log N)$  expected running time. The loosely synchronized point based techniques presented

can act as general subroutines in simulating PRAM algorithms.

The proposed model can be used to implement parallel solutions to a variety of problems in signal and image processing and non numerical problems arising in AI. Some examples are given in part III. In chapter 5, a set of optimal algorithms for finding geometric properties of digitized images is derived for fine grain electro-optical arrays. An efficient electro optical implementation of iterative solutions to sparse linear systems using holographic interconnects is also shown.

Another application of the proposed model is in providing efficient communication for non-Von Neumann types of computations. Implementation of non-Von Neuman computations such as the data flow mode of computation, and neural computing is the topic of chapter 6. Implementation of neural networks using a general purpose electro-optical crossbar which has the potential to interconnect each of the neurons to all the others will be shown. We will also show that similar architecture can be modified to operate asynchronously for realization of a data flow model. Our results substantiate the preference of optical interconnections over an electronic medium as a means of interprocessor communication.

## Chapter 2

## Optics and VLSI

Initial research on integrated optical devices and circuits was stimulated because of a perceived need for compact, rugged, and economical fiber-optic repeaters which are insensitive to external thermal and mechanical variations, and immune to electromagnetic interference from surrounding electric fields [8]. It was predicted that significantly higher usable bandwidths could be achieved by using optical frequencies for all data transmission functions. Batch fabrication technology would provide high reliability and small size. These advantages clearly define the great potential of integrated optics.

Since the early experimental attempts at integration of optical devices for data transmission, in late 1960's, the field has evolved slowly, with a few niche applications in higher speed data processing. Today, optically simple and functionally complex circuits are being manufactured for signal processing applications. These circuits usually offer the system designer a compact, economical, high-bandwidth

device for Fourier transform and correlation operations that would normally require complex electronic circuits ranging in size from several circuit boards to main frame computers.

In this chapter, we first review some of the fundamentals of integrated optics. We then continue with a discussion of merits and components of optical interconnections in VLSI.

#### 2.1 Preliminaries

The physics of light is a very interesting subject. Even people with no background in physics have probably heard about the dual nature of light: on one hand it is composed of elementary particle-like quanta, called photons, and on the other it may be regarded as a wave [32]. For our purposes it will suffice to resolve the ambiguity by considering each photon to be a small wave packet. The light wave is then the sum of many photons. In the context of optical computers, we are usually interested only in the wave-like properties of light. The fact that this wave is the sum of many photons is usually irrelevant. We therefore turn to a discussion of the properties of waves in general, and electro-magnetic waves in particular [31].

Frequency is the most basic property of a wave. Frequency is the number of cycles a wave completes in one second. Electro magnetic waves come in a wide range of frequencies. Visible light occupies a rather narrow band between 10<sup>14</sup> cps (red ) and 10<sup>15</sup> cps (violet). The reason both nature and optical computers

use this range is that many materials transmit and absorb radiation in these frequencies better than in other frequencies, through means of interactions between photons of radiation and the electrons in the material.

Another parameter of interest when talking about light is its wave length. This is the distance the light propagates during one cycle. Therefore the wavelength for a given frequency depends upon the speed of propagation. Speed in turn depends upon the medium through which the radiation is propagating. The index of refraction is a characteristic of the medium that governs the speed of light as it passes through. The refractive index of the vacuum is 1, and the speed of the light through it is approximately 300,000 Km per second. Other materials have a higher refractive index, and the speed of light in them is proportionately lower. When light passes from one medium to another, its change of speed causes a change of direction, called refraction. Lenses and other optical devices use this phenomenon to change the direction of rays of light. Such devices are actually just specially shaped transparent objects with refractive indexes that are different from their surroundings.

Two additional parameters are needed in order to describe a wave. The first is its amplitude, which is the height of the wave. The square of the amplitude is called the intensity of the wave, and conveys the number of photons in the wave. Since each photon is a quantum of energy, the light intensity also indicates how much energy is propagating with the wave. The second parameter is the wave's phase, which stands for the part of the cycle that the wave is in. Absolute phases are of no interest; only the phase of one wave relative to another is of consequence. When we describe a wave by harmonic functions, e.g. sinusoid, the

cycle is  $2\pi$ . A phase difference of  $\pi/2$  between two waves then means that one of them lags behind the other by one quarter of a cycle.

When two waves combine, they are said to interfere. If the waves have the same frequency, the result depends on their relative amplitudes and phases. If the crests in one wave coincide with the crests in the other, each wave cancels out the other This is called constructive interference. If the crests in one match the troughs in the other, the waves tend to cancel out. This is destructive interference (Figure 2.1).

The photons in Figure 2.1-b (constructive interference) are in phase with each other. Therefore their sum is a wave that can be described by a harmonic function such as  $\sin(x)$ . We call such waves coherent light. In many situations the phase of the photons, and thus of the light wave, changes in a random manner. When this happens, we say the light is incoherent.

#### 2.2 Photonic Fundamentals

The properties of the photons explained in the previous section are key design issues in optical computing. The ultimate limit on optical computing speed is the velocity of light in the material, which may be on the order of 10<sup>10</sup> per second. Photons may or may not interfere depending on the coherence properties of the photons in the individual beams. Two light beams can intersect in free space or in a dielectric waveguide with no interference occurring. At the same time, photons from coherent sources can interfere constructively or destructively when combined after traveling different paths. Both constructive and destructive

Figure 2.1: Interference between two waves

behaviors are advantageous in optical computing and signal processing devices. In contrast, electrons interact with each other through their electric fields and repel or attract other charged particles.

A third fundamental property of the photon used extensively in optical devices is that the energy of the photon is related to its frequency through Planck's constant. This energy for the photon is generated by the transition of an electron or molecule between energy states in a material which has been excited. Thus, the designer can select the frequency of the photon by choosing the proper material (e.g., semiconductor materials).

Transmission of information via photons requires no conducting materials and relies solely on low-loss dielectrics or free space. Over short distances (< 1 meter),

the bandwidth of either the optical waveguide or the free space path is limited only by optical modulator technology, whereas the bandwidth of an electronic system is limited by the inductance and capacitance of the metallic transmission path. Although this bandwidth advantage may be exciting, there is a price to pay in larger device dimensions. Waveguide dimensions will be on the order of an optical wavelength (1 micron), and most devices are a factor of 10 or more larger. Aside from the above factors, meaningful size and speed comparisons between electronic circuits and integrated optical circuits must be made on the basis of functional operations (i.e., correlation, convolution, etc.) rather than on individual circuit elements. The speed and parallelism of optical components may lead to smaller packaged circuits even though individual components are larger than submicron VLSI devices.

Finally, photons can be refracted by a lens or diffracted by a slit or pinhole. They may also be scattered by impurity particles and absorbed or refracted by certain materials. The fact that some of these properties can be explained by electromagnetic wave theory, while others cannot, led to the field of quantum mechanics and, in particular, to quantum optics. While more detailed discussion of the properties of photons is beyond the scope of this thesis, it is sufficient to point out that photons exhibit a number of properties different from electrons and provide many new and entirely different possibilities for optical computing. Thus, photon computing should not be viewed simply as another method for duplicating existing computer architectures and operations. It should be looked upon as a unique technology with new potential for computing.

## 2.3 Why Optics in VLSI

It has been demonstrated that optical techniques provide a much higher density for a given bandwidth than electronic techniques. Using free space or wavelength propagation, it is possible to take advantage of the high density bandwidth product available in the optical domain. In addition, using integration of opto-electronic devices, it is possible to communicate with the interior of the chip rather than confining the I/Os to the chip boundary. Following are some of the main limitations of electrical interconnects which are absent from optical integrated links [19, 67].

Several characteristics of present hardware techniques limit the density of electrical interconnects. One limitation is that the edge of the chip is reserved for I/O functions. Another is that electrical interconnects are confined to pseudoplanar structures (e.g., printed wiring boards, backplanes). The phenomenon of crosstalk is a Fundamental limitation on spacing between individual interconnects. This density issue is aggravated with increases in speed in individual devices. As speeds increase, sensitivity to crosstalk through the electrical interconnect also increases and the required distance between devices decreases to ensure that the signal propagation time is less than the clock period.

Obviously, as density increases, the spacing between lines decreases and it is necessary to reduce the cross-sectional area of the conductors in order to place more interconnections in a given volume. Since the dc series resistance of a conductor is directly proportional to its cross-sectional area, this scaling down will result in a larger voltage drop across the interconnect and an increase in

the power required to drive the line. This problem is compounded at higher frequencies because the skin effect reduces the effective conductor area even further. Therefore, as the bandwidth, density, and length of the lines increase, the amount of available power becomes a limiting factor in system performance.

## 2.4 Transmitting Channels

There are two approaches to defining the optical interconnect transmission medium: guided-wave interconnect and free space coupling. In guided wave interconnect the optical data are transmitted and distributed via a medium that localizes the optical energy and distributes it to the required destination points. Examples are optical fibers, light pipes, and planar waveguides. Free space coupling involves point to point or broadcast transmission of the optical energy through space. Both guided wave and free space coupling have trade offs that will affect the design of the system interconnect topology.

Several design methods have been investigated. All promise use of the space above and around chips for interconnects. With this added space and the high density potential of optical interconnects, it is possible to increase the number and bandwidth of interconnects within a computing architecture, resulting in faster systems.

#### 2.4.1 Fiber Optics

An optical fiber is a conductor, or waveguide, for light. The propagation of light in (bent) optical fibers is explained by the phenomenon of total internal reflection

Figure 2.2: Refraction of rays

(see Figure 2.2). The fiber's cross-section has two parts: a core and a cladding. The difference between them is that the core has a larger index of refraction. We denote these indices by  $n_1$  (core) and  $n_2$  (cladding). A beam of light that hits the core/cladding interface at an angle  $\theta_1$  ( from the core side ) is refracted, and emerges at an angle  $\theta_2$  ( on the cladding side ). These angles satisfy the relation

$$n_1\sin\theta_1=n_2\sin\theta_2$$

Since n1 > n2, the  $\theta_1 > \theta_2$  (all angles are in the first quadrant). If  $\theta_1$  is larger than the critical value of  $\arcsin(n2/n1)$ , the formula cannot be valid, because it would require that  $\sin \theta_2 > 1$ . Indeed, for these angles the beam is not refracted. Instead it is reflected back into the core. When a beam of light propagates along an optical fiber, it actually follows the zig-zag path that results from internal reflection each time it hits the core/cladding interface (see Figure 2.3)[66].

The fiber medium is a low loss, low dispersion channel. Over the short links discussed here (inches or less), the channel is virtually bandwidth unlimited. The transport of baseband information over a fiber can be accurately thought of as

Figure 2.3: Light advance within an optical fiber

the modulation of a carrier oscillating at approximately  $2 \times 10^{14}~\mathrm{Hz}$ .

Fiber optic transmission techniques are now well developed and provide a medium for high bandwidth, long haul data transmission [48, 47]. Crosstalk and electrical interference problems, which are expected to increase with circuit densities and speeds of future digital circuits are absent with optical fibers. The loss and drive power are independent of the length of the fiber for distances of interest. The optical approach does not require high speed ground planes, can make circuit layout more flexible, and should be less sensitive to reflection.

Although fiber optics is one important subset of the set of photonic solutions, it is by no means the only (or necessarily the best) solution.

#### 2.4.2 Free Space Interconnects

Guided waves have handicaps that severely limit their use, in particular, high attenuation, high bending loss, and constraint to a plane if fabricated in an integrated optics form. A unique quality of the optical medium is its ability to be directed for propagation in free space and to have two optical channels cross in space without interaction. These properties allow optical interconnects to utilize all three dimensions of space.

The ultimate goal of reconfigurable interconnects is to be able to change the interconnect matrix as quickly and as freely as needed. Such a capability will allow optical interconnection to improve upon many of the functions presently implemented on a limited scale with electronics, such as routing data between processing elements based on data dependent decisions, and multiplexing and demultiplexing information. Potential applications for reconfigurable holographic optical elements are so compelling that investigation of alternatives for programmable interconnections will be of great interest in the future.

This thesis presents various programmable interconnection networks. Programmable interconnection networks are not yet developed enough to form an integrated environment. Alternatively, bulk realization of reconfigurable free space optical interconnects have been studied [101]. What is common to both integrated and bulk implementations is the use of gratings. In current integrated circuits the gratings are fixed and cannot be reconfigured. In bulk systems design, they can be reconfigured using various available spatial light modulators.

## 2.5 Grating

A (thin) grating is a set of fine, straight parallel lines on a transparency [63]. Like mirrors, gratings may be used to change the direction of a beam of light.

However with a grating, the beam is also split into a number of beams that go in different directions. In each of the beams, the exact change in direction depends on the wavelength of the light. Thus a grating may be used to obtain spectral analysis of polychromatic light.

When a coherent beam of light impinges upon a grating, it can be considered as equivalent to a set of coherent, long, linear light sources. The light from these sources interferes. In certain directions, on the path differences for light coming from adjacent sources (i.e. adjacent lines) is an integer multiple of the wavelength, and constructive interference occurs. These are the directions in which we get beams of light. In other directions destructive interference occurs, and the waves tend to cancel out. Generally, the directions in which constructive interference takes place must satisfy (see figure 2.4).

$$d\sin\theta = n\lambda$$

(Bragg's Law)

where d is the grating spacing,  $\lambda$  is the wavelength, n is an integer, called the diffraction order.

Note that this assumes the incident light beam is perpendicular to the grating so that all the lines oscillate in phase.

If the grating is thick, i.e. it is a set of parallel plane surfaces, the situation is slightly different. A light beam impinging on such a grating is reflected by each surface individually. If the angle between the beam and the surfaces is just right, constructive interference will occur between the reflections. The result will be a very strong diffraction. At other angles the diffraction will be very weak. The angle at which strong diffraction occurs is called the Bragg angle, and it satisfies

Figure 2.4: Bragg Diffraction

$\sin \theta = (n\lambda/2d)$ . This phenomenon is of major importance in volume holography and some acousto-optical devices, as well as in the diffraction of x-rays from crystals.

#### 2.5.1 Acousto-Optical Elements

Gratings need not be stable and tangible like most other devices; in fact it is quite common to use an acoustic wave as a grating. An acoustic wave propagating in a crystal causes a periodic deformation of the crystal. This deformation usually results in a periodic change of the refractive index of the crystal. The velocity of the acoustic wave is always much lower than that of light waves. Therefore we may say that to a good approximation a light wave passing through the crystal

feels a standing periodic change of the medium- that is, a grating. This grating causes diffraction of the light, just like any other grating would. Such phenomena in which light is scattered by interaction with acoustic waves are called Brillouin scattering.

#### 2.5.2 Holographic Optical Elements

Holograms can be written on silicon in the following way. The photographic film hologram is contact printed onto a layer of photoresist on a silicon substrate. The photoresist is developed and the silicon is etched by chemical means. After removal of the remaining photoresist, a reflective surface-relief hologram is present in the surface of the silicon. Diffraction efficiencies of 18 to 20 silicon surface-relief holograms is possible.

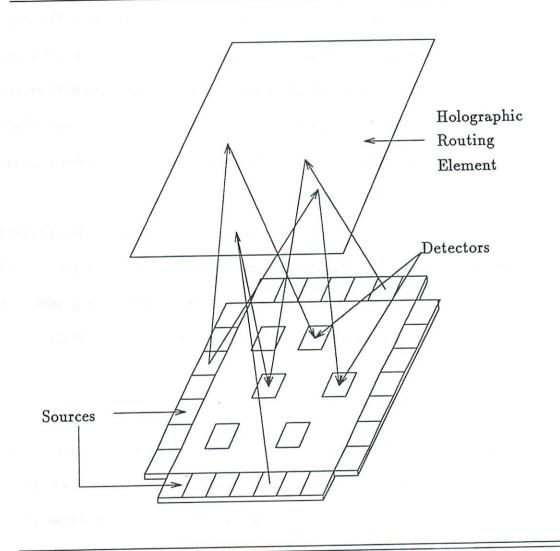

Assume a single source of light. A simple hologram, similar to a diffraction grating, can deflect its light in any desired direction (depending on the orientation of grating), and focus it on a sink. A more complicated hologram can create multiple images of the source, each on a different sink. In the general case we have a set of sources, a set of sinks, and an arbitrary mapping of sources to sinks. In order to implement this mapping, the hologram can be divided into subholograms, one for each source [103, 59, 58]. Each sub-hologram is illuminated by one source only, and it images that source on the appropriate sinks. (see figure 2.5).

Free space interconnections utilize three-dimensional space [12]. There are various ways in which to set up the sources, sinks and hologram [43]. The most compact scheme is to have the sources and sinks arranged in a plane, with a

Figure 2.5: A holographic interconnection element

reflection hologram suspended above them (see figure 2.6). Other schemes use transmission holograms instead of reflection ones, and then redirect the light with mirrors. If the hologram is implemented by an Spatial Light Modulator (SLM), rather than being fixed, the interconnection pattern may be changed dynamically [69, 43].

Optical noise in the interconnections will arise from two aspects of the Holograms. First, to whatever extent the hologram is not perfectly efficient, the undiffracted light produces a diffuse unfocused background light level at the detectors. Second, all holograms produce some amount of stray light, resulting from stochastic effects in the recording process and, in the case of computer generated holograms, from quantization effects in the encoding. To maximize the signal reaching the detectors and to minimize optical effects on surrounding circuitry, the spot size should closely match the size of the detectors, i.e. about 10 by 10

Figure 2.6: A possible holographic configuration

#### 2.6 Sources

The properties of an optical system depend to a large degree upon the source of the light that is being used. Today, two sources dominate: LEDs and LASERs. Their operations, depend on certain changes in the energy states of the electrons in the light-source material. Specifically, electrons in high-energy (so called "excited") states go down to their ground states. In doing so they release an energy quantum in the form of a photon.

A LASER (Light Amplification by Stimulated Emission of Radiation) outputs an intense, monochromatic (having a single frequency), coherent and very directional beam of light [104]. A LED (Light Emitting Diode) can provide narrow band (having relatively small range of frequency), incoherent light [11, 77].

#### 2.6.1 Laser Diodes

Light sources are required to convert electrical signals to optical form. Laser based optical interconnects represent the most obvious choice of links. The compact size and low electric power requirements of laser diodes will ease the problems associated with the assembly and integration. One significant advantage of the laser diode is its potential for high modulation frequency, which has been demonstrated as high as 18 GHz.

With direct drive, the laser diode can be full on/off modulated at multi-Gb/s rates. Small signal modulation has been reported beyond 10 GHz. The total

average current required to drive the laser diode ranges from 15 mA to 45 mA. Total average power dissipation for a laser diode, then will range from 40 mW to 180 mW. Typical dimensions of a laser diode is 200 by 200 by 75  $\mu m$  [48, 47].

## 2.6.2 Light Emitting Diodes

LEDs are highly reliable devices with no threshold requirements, are relatively simple to fabricate, and can be easily fabricated as edge or surface emitters. Performance limitations include low quantum efficiency, a high drive power requirement and low speed [48, 47]. Semiconductor laser diodes although similar in structure to LEDs are highly efficient. When they are operated above threshold the internal quantum efficiency approaches 100% for the most efficient class of laser sources developed.

# 2.7 Detectors

Unlike a light wave telecommunications receiver, an optical interconnect receiver is basically a high speed opto-electronic transducer. For optical interconnect applications, the main object is to receive the incoming optical data stream, transform it to electronics, amplify ( and filter ) it, and redigitize it.

The diameter of a detector is approximately  $40\mu m$ . GaAs detectors with rise times on the order of 30 to 40 ps have been made [67]. There are several alternatives for GaAs detectors: the p-i-n diode, the avalanche photodetector (APF), and the Schottky barrier photodiode.

# 2.8 Semiconductor Integration

Monolithically integrated opto-electronic circuits that incorporate electronic and optical devices on the sam substrate have potentially important advantages over conventional hybrid circuits. The monolithic integration eliminates the excess capacitance and inductance associated with bonding pads and wires. The resulting circuit operates faster than its hybrid counterpart, with lower noise and less power. Integration also eliminates the need for broad band impedance matches. It is expected that integrated lasers and detectors can be realized in high density form with dimensions of 50 to 200  $\mu m$  for laser cavities and photodetectors. Current monolithic implementations of optical interconnect technology involve either sources and detectors integrated with electronic circuits on GaAs or GaAs grown on Si. Both of these approaches are difficult to implement at present [36, 18].

### 2.8.1 Silicon Substrate

Silicon based integrated optics are nearly monolithic: only the source is in GaAs, and all the rest is in Si. Silicon offers a stable base for electronic circuitry; silicon VLSI technology is well established and has a large established industry [36]. State of art MOS circuits are quite fast, with cycle times up to 3 GHz reported in the literature. Long wavelength optics require epitaxial techniques on either silicon or gallium arsenide. Where is desirable to interface directly with long distance optical fibers (such as in telecommunication environment which operates at long wavelengths), this means that the processing required to build monolithically integrated optical components is as difficult in GaAs as in silicon.

Finally, silicon provides a lower-cost substrate for components that do not need extreme speed. These components form the vast majority of most systems.

#### 2.8.2 Gallium Arsenide

Monolithic Gallium-Arsenide (or rather various alloys of GaAl-As) is probably on its way to becoming the preferred choice. The reason is that this is the only system of materials that enables all the necessary active devices-lasers, modulators, switches and detectors- to be fabricated together. In particular, the most efficient and useful light source today for fiber optics and integrated optics is the GaAs double heterostructure injection laser [110, 99]. However differences in the detailed requirements for the laser versus the waveguide applications remain to be resolved before a true monolithic technology emerges.

GaAs ICs and GaAs opto-electronic devices, such as diode lasers and photodiode detectors are needed to construct multigigahertz optical transmitters, receivers, transceiver, repeater, and switches.

## 2.8.3 Hybrid Integration

Eventually, the sources must be brought onto the electronic chip either through fabrication of the electronics on GaAs or by fabrication of GaAs sources on Si substrates [18]. The best waveguide active devices, eg. modulators and switches, are those fabricated on Lithium Niobate substrates. However the sources used are usually based on GaAs, while the detectors employ Si. Hence the hybrid nature of this system, as an example.

# 2.9 Limitations

Whereas in VLSI the minimal feature size is determined by the technology and by the microscopic characteristic of the materials, in optics the minimal feature size corresponds to the wavelength of the light [68]. The size of optical elements must be at least a few wavelengths: light simply cannot be confined to a cross section of much less than a wavelength, i.e. approximately 1  $\mu m$ . At the moment it so happens that VLSI technology produces features that are about of this size too, however it is already obvious that it will be impossible to miniaturize optical devices to the same degree that is possible in electronics, as it is expected that electronic devices will be reduced by at least another order of magnitude before reaching their limit [106].

# Part II

**Computational Models**

# Chapter 3

# Optical Models of Computation

The relation between the speed and size of VLSI circuits was explored using the methodology of complexity theory in [113]. As the first step of this methodology, an accurate and precisely-defined model of a VLSI chip was devised. This model captures the two-dimensionality of VLSI, in that transistors are laid out on the surface of a piece of silicon, and there are only a few layers of metal available for interconnections. The fundamental result that clearly defines the limits of VLSI is due to the fact that the amount of time (T) required to solve a problem on a VLSI chip is at least equal to the number of cycles required to pass the minimum required information (I) over the available bandwidth across the mid line of a VLSI design having area (A). This leads to  $AT^2 = \Omega(I^2)$ . In this chapter, we introduce an abstract optical model of computation to explore speed size relationship in using free space optical beams, as opposed to wires, for means of intercommunications. This model accurately represents currently implementable

optical network of processors. Hence, the derived lower bounds on its computational efficiency gives us a tool to analyze the optimality of various physical implementations of OMC, in solving problems. In the first section lower bounds for computation power are derived, and in the following section three architectures representing upper bounds on the volume requirements of the model are shown.

#### 3.1 Lower bounds

In this section, we define an Optical model of computation which is an abstraction of currently implementable optical and electro-optical computers. Similar to the VLSI model of computation [115], this model can be used to understand the limits on computational efficiency in using optical technology. We show that minimum volume requirement of an optical model of computation is same as the minimum VLSI area in the VLSI model. Using information transfer argument, we also show a methodology to determine the minimum volume requirement of an electro-optical system for solving a problem.

#### 3.1.1 An Optical Model

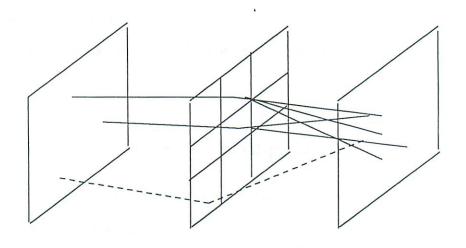

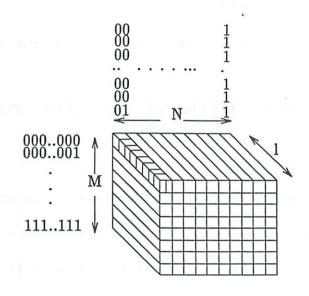

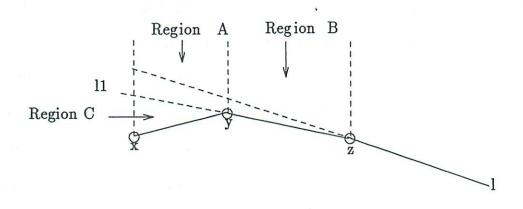

An optical model is shown in Figure 3.1. More formally this model is defined as follows:

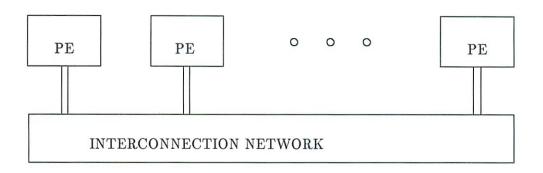

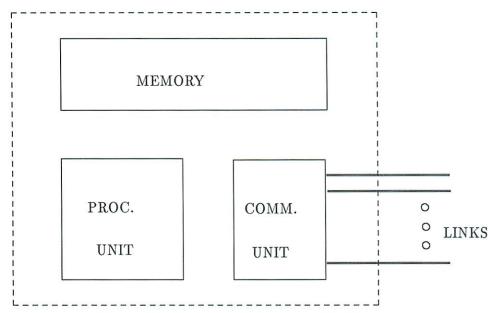

**Definition 1** An optical model of computation represents a network of N processors each associated with a memory module, and a deflecting unit capable of establishing direct optical connection to another processor. The interprocessor communication is performed satisfying the following rules similar to [4]:

1. At any time a processor can send at most one message. Its destination is another processor.

2. The message will succeed in reaching the processor if it is the only message with that processor as its destination, at that time step.

3. All messages succeed or fail (and thus are discarded) in unit time.

To insure that every processor knows when its message succeeds we assume that the OMC is run in two phases. In the first phase, read/write messages are sent, and in the second, values are returned to successful readers and acknowledgements are returned to successful writers. We assume that the operation mode is synchronous, and all processors are connected to a central control unit. The above definition is supplemented with the following set of assumptions for accurate analysis.

- 1. Processors are embedded in the Euclidean plane. This is referred to as the processing layer.

- 2. Each of the processing/memory elements occupies unit area.

- 3. Deflectors are embedded in the Euclidean plane. This is referred to as the deflecting layer.

- 4. Each deflecting unit occupies at least one unit area.

- 5. The deflecting layer is collinear to the processing layer.

- 6. I/O is performed at I/O pads. Each I/O pad occupies unit area.

- 7. The total volume is the sum of the volume occupied by the processing layer, the deflecting layer, and the space for optical beams.

- 8. The intercommunication is done through free space optical beams.

- 9. Time is measured in terms of number of units of clock cycles.

- 10. An optical beam carries a constant amount of information in one unit of time, independent of the distance to be covered.

- 11. A deflector is capable of redirecting an incident beam in one unit of time.

- 12. A processor can perform a simple arithmetic/logic operation in one unit of time.

- 13. The time, T for computation is the time between the arrival of the first input to the departure of the last output.

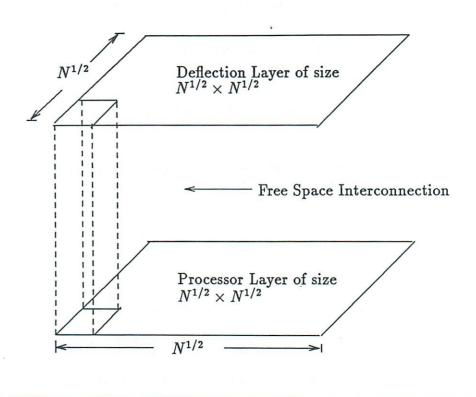

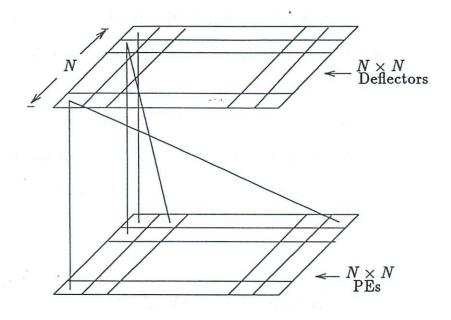

To be able to compare our results with those on VLSI model of computation [113], without loss of generality, assume that there are N processors placed on a  $N^{1/2} \times N^{1/2}$  grid called the processing layer. Similarly, there are N deflecting modules on a layer above the processing layer, called the deflection layer. The interconnection beams are established in the free space between these two layers, as shown in Figure 3.1. Hence, the amount of data that can be exchanged in a cycle between two sets of processors (two way information transfer rate) is N. The time (T) required to solve a problem is the number of cycles required to exchange the minimum required information (I). This leads to:

$$AT = \Omega(I)$$

where A is the area occupied by the processing layer.

A related model is VLSIO [7], which is a three dimensional generalization of the wire model of the two dimensional VLSI with optical beams replacing the wires as communication channels. Compared to the three dimensional VLSI model of computation [95], our model is more resource efficient. The simulation of many parallel organizations using the OMC requires considerably less amount

Figure 3.1: Optical Model of Computation

of volume than their layout in the three dimensional VLSI model. For example, the layout volume of a N processor hypercube can be reduced from  $O(N^{3/2})$  to  $O(N \log N)$  when using OMC with mirrors as deflectors. The following result can be stated:

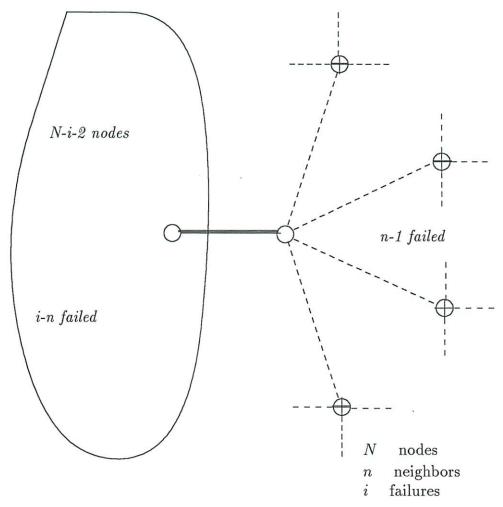

Proposition 1 Any computation performed by a three dimensional VLSI organization having N processors with degree d, in time T, and volume V can be performed on OMC in volume v, and time t, where  $dT/N \le t \le T$ , and  $Nd \le v$ .

The upper bound on t is obvious. Its lower bound also can be simply obtained by multiplying T by d/N which is the maximum speed up factor that can be obtained due to its unit time interconnection medium. The lower bound on v is obtained by the minimum area requirement for having d deflectors for each of the processing elements. In the next sections three different parallel architectures are presented as possible efficient upper bounds for v.

# 3.1.2 Optical Volume, VLSI Area and 1-way Information Transfer

The minimum VLSI area requirement for computing a problem is related to the lower bound on the 1-way information transfer [126, 82]. In this section, we briefly discuss the 1-way information transfer for computing single output function and then extend the argument to multiple output functions. We also relate this 1-way information transfer to the Optical volume requirement of an electro-optical implementation of OMC to solve a problem.

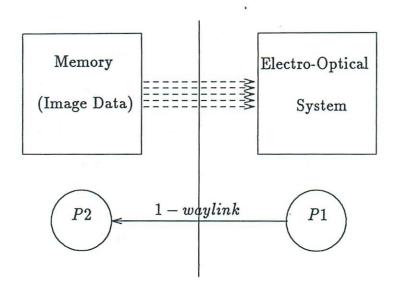

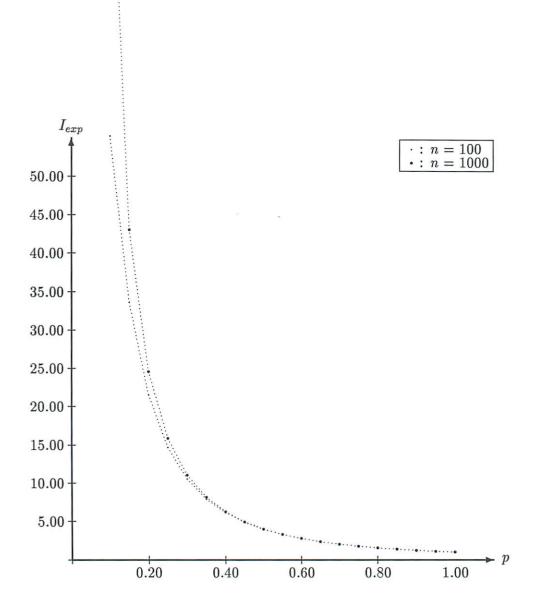

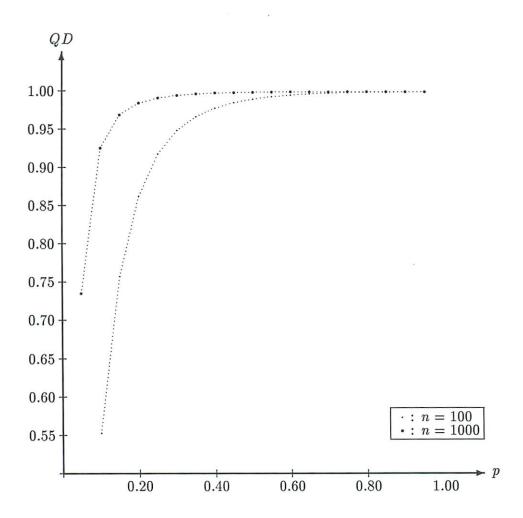

The following abstract setting has been shown to be useful in estimating the minimum VLSI chip area [82, 112]. Two sets of processors P1 and P2 each receive  $\frac{n}{2}$  bits of an n input function f to be computed. The input partition can be denoted by  $(\pi_1^i, \pi_2^i)$  where  $\pi_1^i(\pi_2^i)$  are the inputs known to P1(P2) and  $\pi_1^i \cap \pi_2^i = \phi$ . Also  $|\pi_1^i| = |\pi_2^i| = \frac{n}{2}$ . The rectangle corresponding to this partition is defined as  $M \times N$  where M(N) =set of all values known to P1(P2). It is clear that  $|M| = |N| = 2^{\frac{n}{2}}$ . In the 1-way information transfer model, P2 computes f and outputs the result. Hence, given an input partition, some information based on the input bits of  $\pi_1^i$  are transferred to P2 in order to complete the computation. The minimum information transfer from P1 to P2 to compute f over all possible input partitions is denoted by  $I_1(f)$  and is defined as follows:

$$I_1(f) = egin{array}{c} Min \ input \ partition \end{array} \left\{ egin{array}{c} worst \ case \ information \ transfer \ from \ P1 \ to \ P2 \end{array}

ight\}$$

Two rows  $i_1, i_2 \in M$  in the computational rectangle are said to be distinct if  $\exists$  a  $j \in N$  such that  $f(i_1, j) \neq f(i_2, j)$ . If d(f) is the minimum number of such distinct rows over all possible input partitions, then  $I_1(f)$  is equal to  $\log d(f)$  [125]. The area requirement A of any chip computing f is  $\Omega(I_1(f))$  [126, 82].

The above 1-way protocol for single output function can be easily extended to multiple output functions by introducing a suitable output partition over the output functions. Let  $F = \{f_1, f_2, \dots, f_l\}$  be the set of output functions. The output partition, similar to the input partition, can be denoted by  $(\pi_1^o, \pi_2^o)$ . The output partition satisfies the conditions  $\pi_1^o \cap \pi_2^o = \phi$  and  $\pi_1^o \cup \pi_2^o = \{f_1, f_2, \dots, f_l\}$ . Both processors P1 and P2 are allowed to compute the output functions belonging to their respective subsets. Before proceeding further, we state some definitions and restate some earlier results.

Since the 1-way communication link is from P1 to P2, it is not possible to transfer data from P2 to P1 to compute a function belonging to  $\pi_1^o$ . Hence, an output partition requiring transfer of data from P2 to P1 is not feasible. This leads to the following definition of a feasible output partition:

**Definition 2** An output partition is feasible iff on any input partition, all functions in  $\pi_1^{\circ}$  can be computed at P1 using only the input bits of  $\pi_1^{i}$ .

The 1-way information transfer for multiple output functions can depend on the output partition. Hence,  $I_1(F)$ , the 1-way complexity of computing a set of

<sup>&</sup>lt;sup>3</sup>All logarithms in this thesis are to base 2.

output functions is defined as follows:

The relationship between  $I_1$  and the minimum area requirement A of a chip stated earlier for single output function holds good for multiple output functions too.

**Theorem 1** The volume  $V_o$  of any electro-optical system computing F satisfies  $V_o = \Omega(I_1(F))$ .

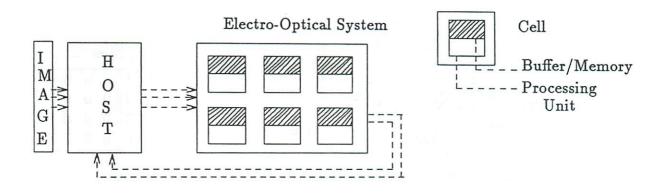

Proof: Consider an electro-optical system as shown in figure 3.2. P1 can be viewed as the electro-optical system and P2 as the memory. Consider the state of the system after reading  $\frac{n}{2}$  input bits. These bits can be looked upon as bits belonging to  $\pi_1^i$ . Based on this input, the system would have computed some set of output functions. Denote these functions as  $\pi_1^o$ . If the volume of the system is  $V_o$ , then the system would not have memorized more than  $V_o$  bits of information. It is easy to design a 1-way protocol with  $V_o$  bits of information transfer from P1 to P2 to compute the rest of the output functions. Hence, the system should have at least  $I_1(F)$  memory elements. Thus, the volume of the system must be  $\Omega(I_1(F))$ .

The computation of F over an input and output partition can be represented in the form of a computational parallelepiped P as shown in figure 3.3. M(N) are the set of possible values of the input bits known to P1(P2). For a fixed value of input bits, the output functions in set F are represented by a vector of length l

Figure 3.2: 1-way information transfer

in the third dimension of P. Given an input partition, the output functions can be divided into the following subsets:

- $F_{11}$  The subset of the output functions which can be computed at P1 (on every input) using the input bits of  $\pi_1^i$  only

- $F_{22}$  The subset of the output functions which can be computed at P2 (on every input) using the input bits of  $\pi_2^i$  only

- $F_{12}$  The rest of the output functions.

The computation of the output functions belonging to the subsets  $F_{12}$  and  $F_{22}$  require data from  $\pi_2^i$ . According to the definition of a feasible output partition, these functions can not be computed at P1 and, hence, to be computed at P2. Therefore, for a given input partition  $(\pi_1^i, \pi_2^i)$ , the output partition is feasible iff

Figure 3.3: The computational parallelepiped P

$F_{12} \subseteq \pi_2^o$  and  $F_{22} \subseteq \pi_2^o$ .

Since the output functions  $F_{11}$  and  $F_{22}$  are computed at P1 and P2 respectively using exclusively the input bits assigned to them, there is no information transfer associated with these computations. The computation of  $F_{12}$  only requires information transfer from P1 to P2. This information transfer  $I_1(F)$  is determined from the number of distinct planes in P.

**Definition 3** Two planes  $i_1, i_2 \in M$  in P are distinct iff there exists a  $j \in N$  and a function  $f_k \in F$  such that  $f_k(i_1, j) \neq f_k(i_2, j)$ .

Based on the above definition of distinct planes,  $I_1(F)$  can be estimated in a similar spirit as in  $I_1(f)$  [125]. This leads to:

**Proposition 2** For a fixed input partition  $(\pi_1^i, \pi_2^i)$  and a fixed output partition  $(\pi_1^o, \pi_2^o)$ , the minimum number of bits of information transfer from P1 to P2 to compute F is  $\log d(F)$ , where d(F) is the number of distinct planes in P. Also,

the 1-way complexity  $I_1(F)$  is equal to log d, where d is the minimum d(F) over all possible input and feasible output partitions.

In the following section, we use image convolution to illustrate our ideas.

# 3.1.3 Lower bounds On Optical Volume For Image Convolution

The techniques of last section can be used to obtain lower bound on the optical volume, for image convolution under several input formats. For a  $n \times n$  image, the convolution operation produces  $O(n^2)$  output. The information transfer  $I_1(F)$ , for such operation can be analyzed based on the multiple output function model discussed above.

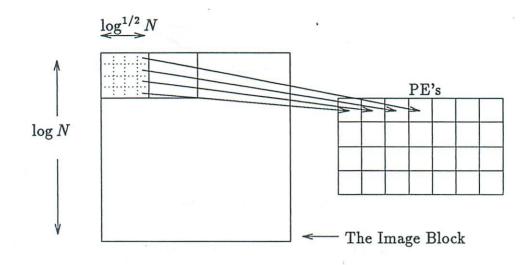

Due to the computationally intensive nature of the convolution operation, most of the designs in the literature perform several computations per input pixel fetch to achieve high throughput and reduced memory bandwidth. Figure 3.4 shows the computing environment to carry out convolution using an Electro-optical system.

The input to the system is a  $n \times n$  image and a  $w \times w$  kernel. The electrooptical system must be able to compute the image convolution on any input  $n \times n$ image and any  $w \times w$  kernel. The host is responsible for acquiring the input data

and feeding it to the system which contains processing units for computation and

memory elements for storing intermediate results. Though, most of the practical

designs organize cells to input the image pixels from the host in a rasterscan

i.e. scanline fashion, designs are possible to input data in arbitrary sequence of

rows/columns or arbitrary pixel manner.

Figure 3.4: Environment for computing image convolution

#### Scanline Input Case

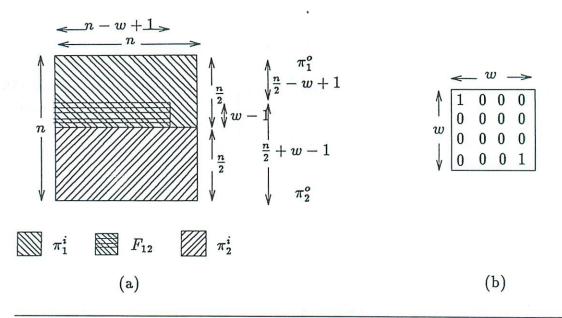

In this case, the input partition corresponds to P1 receiving the upper half of the image and P2 receiving the lower half as shown in figure 3.5 (a). Let the kernel K of size  $w \times w$  be as shown in figure 3.5 (b). All kernel weights are zero except for K(1,1) and K(w,w) entries. With the given kernel K, the output C(i,j) of the convolution becomes:

$$C(i,j) = I(i,j) + I(i+w-1,j+w-1)$$

for  $1 \le i,j \le n-w+1$ .

**Lemma 1** [24] The volume  $V_o$  of any electro-optical design using scanline input format for image convolution satisfies  $V_o = \Omega(nw)$ .

#### The General Input Case

In this case, we consider designs, where the input is received by the electro-optical system from the host in arbitrary sequence of pixels. We first determine a bound

Figure 3.5: (a) The input and output partition for scanline case. (b) A kernel for a special case of this, where the input is restricted to arbitrary row(column) major sequence. Later we derive the bound for the general case by reducing it to the arbitrary row(column) major input format.

Theorem 2 [24] The volume  $V_o$  of any electro-optical design for convolving a  $w \times w$  kernel with a  $n \times n$  image satisfies  $V_o = \Omega(nw)$ .

# 3.2 Upper bounds

In this section, we present a class of optical interconnection networks as a realization of the OMC presented in the previous section. Each of the proposed designs uses a different optical device technology for redirection of the optical beams to establish a new topology at any clock cycle, and represents an upper bound on the volume requirement of OMC.

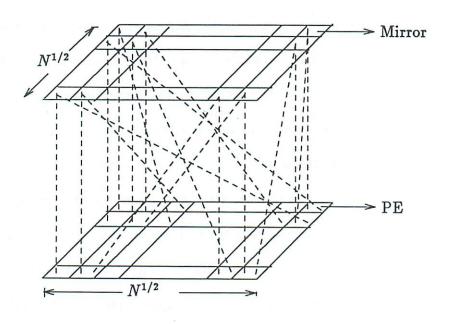

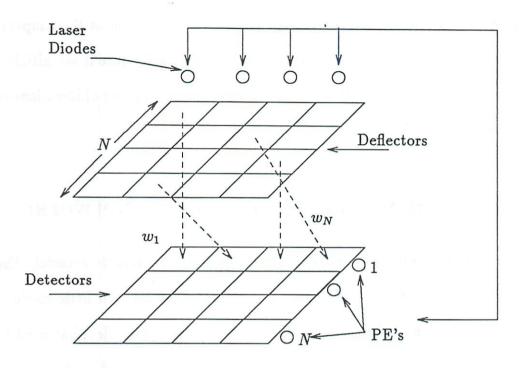

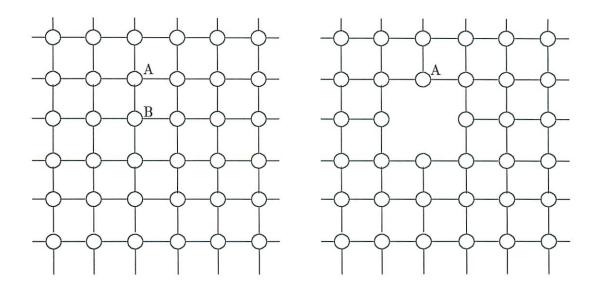

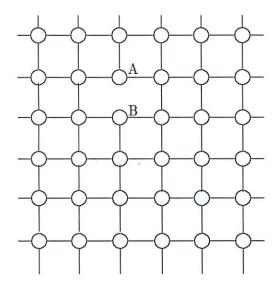

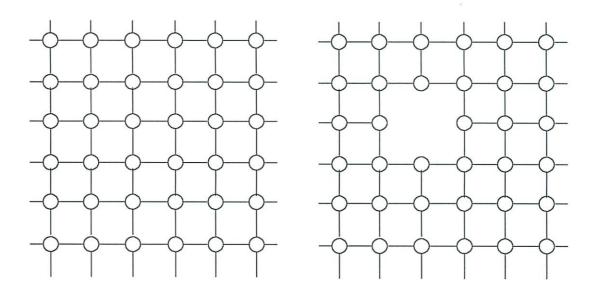

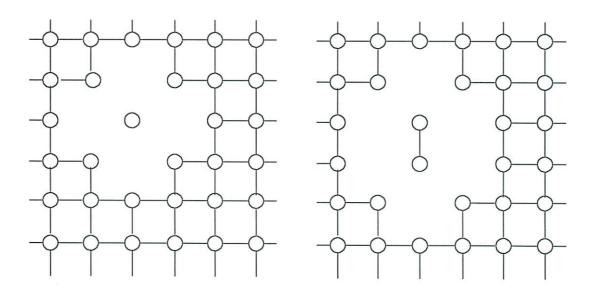

# 3.2.1 Optical Mesh Using Mirrors

In this design, there are N processors on the processing layer of area N. Similarly, the deflecting layer has area N and holds N mirrors. These layers are aligned so that each of the mirrors is located directly above its associated processor (see Figure 3.6). Each processor has two lasers. One of these is directed up towards the arithmetic unit of the mirror and the other is directed towards the mirror's surface. A connection phase would consist of two cycles. In the first cycle, each processor sends the address of its desired destination processor to the arithmetic unit of its associated mirror using its dedicated laser. The arithmetic unit of the mirror computes a rotation degree such that both the origin and destination processors have equal angle with the line perpendicular to the surface of the mirror in the plane formed by the mirror, the source processor, and the destination processor. Once the angle is computed, the mirror is rotated to point to the desired destination. In the second cycle, connection is established by the laser beam carrying the data from the source to the mirror and from the mirror being reflected towards the destination. Since the connection is done through a mechanical movement of the mirror, with the current technology this leads to an order of milli-second reconfiguration time. Therefore this architecture is suitable for applications where the interconnection topology does not have to be changed frequently. In [70], the design of various topologies have been studied to minimize the time complexity of several problems for fixed period of computation.

The space requirement of this architecture is O(N) under the following assumption. Each mirror is attached to a simple electro-mechanical device which

takes one unit of space and can rotate to any position in one unit of time. With current technological advancements, the above assumption may not be the most accurate one but we do not see any technological limitations preventing us from making our assumptions. In fact, our assumptions are as valid as those in VLSI; the constant propagation delay assumption regardless of wire's length. Other assumptions can also be made based on the following arguments. Many mirrors have a reconfiguration delay proportional to their rotation angle, O(N). More complex mirrors on the other hand, can rotate faster for a larger angle (unit time rotation delay) but their size can grow proportional to the number of angles they can realize (O(N)).

Figure 3.6: An Optical mesh using mirrors

# 3.2.2 Reconfiguration Using Acousto-Optic Devices