# Design of Hierarchically Testable and Maintainable Systems

Jung-Cheun Lien

CEng Technical Report 91-19

A Dissertation Presented to the FACULTY OF THE GRADUATE SCHOOL UNIVERSITY OF SOUTHERN CA'LIFORNIA In Partial Fulfillment of the Requirements for the Degree DOCTOR OF PHILOSOPriy (Computer Engineering)

(Copyright August 1991)

Electrical Engineering Systems University of Southern California Los Angeles, CA. 90089-2562

# DESIGN OF HIERARCHICALLY TESTABLE AND MAINTAINABLE SYSTEMS

by

Jung-Cheun Lien

# A Dissertation Presented to the FACULTY OF THE GRADUATE SCHOOL UNIVERSITY OF SOUTHERN CALIFORNIA

In Partial Fulfillment of the Requirements for the Degree DOCTOR OF PHILOSOPHY

(Computer Engineering)

August 1991

Copyright 1991 Jung-Cheun Lien

# UNIVERSITY OF SOUTHERN CALIFORNIA THE GRADUATE SCHOOL UNIVERSITY PARK LOS ANGELES, CALIFORNIA 90007

| This dissertation, written by                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JUNG-CHEUN LIEN                                                                                                                                                                                         |

| under the direction of h.is Dissertation Committee, and approved by all its members has been presented to and accepted by The Graduate School, in partial fulfillment of requirements for the degree of |

| DOCTOR OF PHILOSOPHY                                                                                                                                                                                    |

| Pallaca Solomon  Dean of Graduate Studies                                                                                                                                                               |

| Date July 18, 1991                                                                                                                                                                                      |

| DISSERTATION COMMITTEE                                                                                                                                                                                  |

| Mila ABresu Chairperson                                                                                                                                                                                 |

| Lauli Charles Lauli                                                                                                                                                                                     |

### Dedication

$$\operatorname{To}$$  My wife Jung-Yu and our parents

#### Acknowledgements

I am very grateful to Prof. Melvin Breuer for his encouragement, guidance and support during my dissertation work. I consider it my privilege to have worked with him.

I would also like to thank Prof. Irving Reed and Prof. Charles Lanski for serving on my dissertation committee.

During my years at USC, I benefited greatly from interacting with many colleagues and friends. In particular I would like to mention Kuen-Jong Lee, Dr. Rajesh Gupta, Rajagopalan Srinivasan, Amitava Majumdar, Sing-Ban Tien, Dr. Rajiv Gupta and Dr. Charles Njinda.

I would like to acknowledge the financial support provided by the Defense Advanced Research Projects Agency through Contract No. N00014-87-K-0861, monitored by the Office of Naval Research, and No. JFBI90092, monitored by the Federal Bureau of Investigation.

Finally, I would like to thank my wife Jung-Yu for her endless love and support. This dissertation would never have been completed without her.

## Contents

| D                                | edica | tion   |                               | i    |

|----------------------------------|-------|--------|-------------------------------|------|

| Å                                | ckno  | wledge | ements                        | iii  |

| A                                | bstra | ıct    |                               | xiii |

| 1                                | Intr  | oducti | ion                           | 1    |

|                                  | 1.1   | Backg  | round                         | 1    |

|                                  | 1.2   | Previo | ous Work                      | 3    |

|                                  |       | 1.2.1  | System Architecture           | 3    |

|                                  |       | 1.2.2  | Testability Bus               | 4    |

|                                  |       | 1.2.3  | Testable Chip Control Model   | 5    |

|                                  |       | 1.2.4  | Testable Chip Design          | 6    |

|                                  |       | 1.2.5  | Testable Module Design        | 7    |

|                                  |       | 1.2.6  | Interconnect Test Generation  | 7    |

|                                  |       | 1.2.7  | Test Scheduling               | 9    |

|                                  | 1.3   | The D  | Design Approach               | 10   |

|                                  | 1.4   | The H  | lierarchical Test Methodology | 10   |

|                                  | 1.5   | Test C | Controllers for a Circuit     | 13   |

|                                  | 1.6   | Thesis | Outline                       | 15   |

| 2 Controllers for Testable Chips |       |        | s for Testable Chips          | 17   |

|                                  | 2.1   | The M  | Iodel                         | 17   |

|   |     | 2.1.1    | Boundary Scan Archite    | cture                                   | 17 |

|---|-----|----------|--------------------------|-----------------------------------------|----|

|   | 2.2 | Bus-I    | ependent BIT Controller  | s                                       | 23 |

|   |     | 2.2.1    | BIT Controller for a LS  | SD Kernel                               | 26 |

|   |     | 2.2.2    | BIT Controller for a BI  | LBO Kernel                              | 27 |

|   |     | 2.2.3    | BIT Controller for a Co  | mplex Kernel                            | 29 |

|   |     | 2.2.4    | A Mapping Algorithm      | * * * * * * * * * * * * * * * * * * * * | 33 |

|   | 2.3 | Autor    | omous BIT Controller .   |                                         | 38 |

|   |     | 2.3.1    | Serial BIT Controllers   | ******                                  | 38 |

|   |     |          | 2.3.1.1 A Hard-Wired     | Serial BIT Controller                   | 38 |

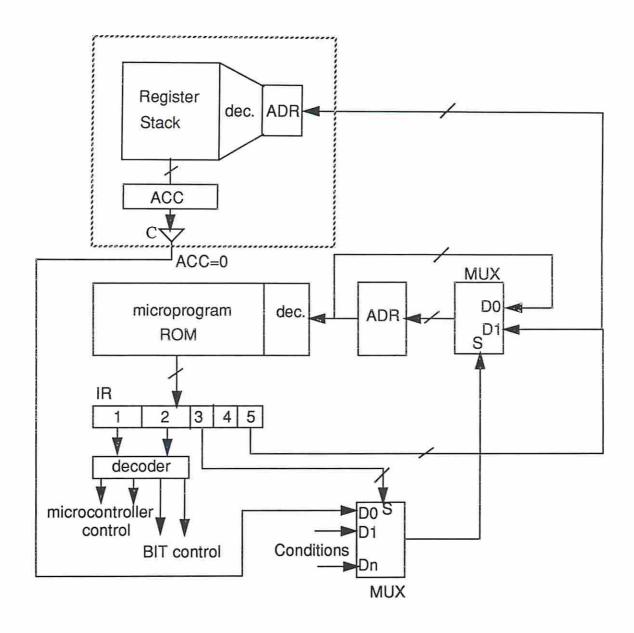

|   |     |          | 2.3.1.2 A Microprogra    | mmed Serial BIT Controller              | 40 |

|   |     | 2.3.2    | Parallel BIT Controllers |                                         | 43 |

|   |     |          | 2.3.2.1 Interleaved FS   | M Controller                            | 44 |

|   |     |          | 2.3.2.2 Tree of Counter  | ers Design                              | 48 |

|   |     |          | 2.3.2.3 Counter Sharin   | ng Design                               | 53 |

|   |     |          | 2.3.2.4 Comparison of    | Three Designs                           | 55 |

| 3 | Con | itrollei | for Testable Modules     | )                                       | 60 |

|   | 3.1 | Requi    | ements for an MMC        |                                         | 61 |

|   | 3.2 | MMC      | Architecture             |                                         | 62 |

|   |     | 3.2.1    | Test Channel Design .    |                                         | 63 |

|   |     | 3.2.2    | Bus Driver/Receiver .    |                                         | 73 |

|   |     | 3.2.3    | Functional Bus Interface |                                         | 74 |

|   |     | 3.2.4    | Testability Register     |                                         | 74 |

|   |     | 3.2.5    | Analog Test Interface .  |                                         | 75 |

|   |     | 3.2.6    | L1-Slave                 |                                         | 75 |

|   |     | 3.2.7    | Processor                |                                         | 75 |

|   |     | 3.2.8    | Memory                   |                                         | 80 |

|   |     | 3.2.9    | Stand-Alone MMC          |                                         | 81 |

|   | 3 3 | MMC      | Self Test                |                                         | Q1 |

|   | 9 4  | D:     | SAMOD:                                             |     |

|---|------|--------|----------------------------------------------------|-----|

|   | 3.4  |        | ssion of MMC Design                                | 8   |

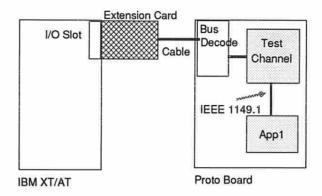

|   | 3.5  |        | MC Prototype                                       | 8   |

|   |      | 3.5.1  | Test Channel                                       | 88  |

|   |      | 3.5.2  | Processor and Memory                               | 86  |

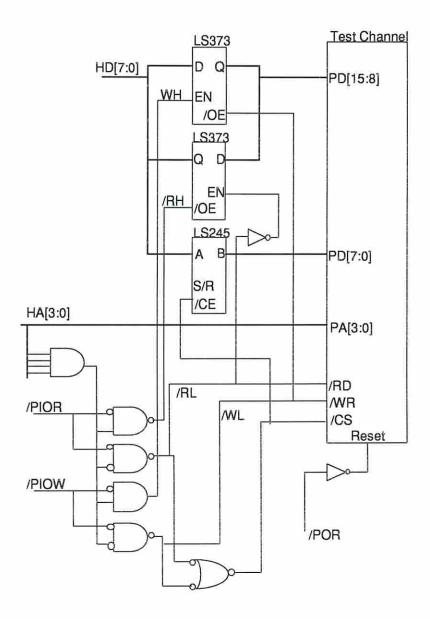

|   |      | 3.5.3  | Processor and Test Channel Interface               | 86  |

|   |      | 3.5.4  | Discussion                                         | 89  |

|   | 3.6  | Testin | g a Kernel Using MMC and CMC                       | 90  |

| 4 | Test | t Prog | ram Synthesis                                      | 93  |

|   | 4.1  | Langu  | ages                                               | 95  |

|   |      | 4.1.1  | CTL - The Chip Test Language                       | 95  |

|   |      |        | 4.1.1.1 Formal Definition of the CTL               | 103 |

|   |      | 4.1.2  | MTL - The Module Test Language                     | 104 |

|   |      |        | 4.1.2.1 Formal Definition of the MTL Syntax        | 109 |

|   | 4.2  | Synthe |                                                    | 111 |

|   |      | 4.2.1  | C2C Synthesizer                                    | 111 |

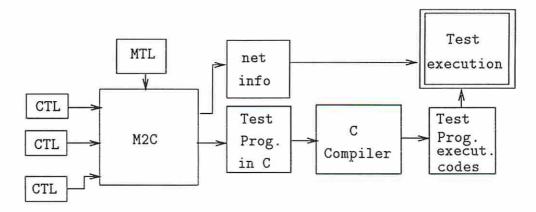

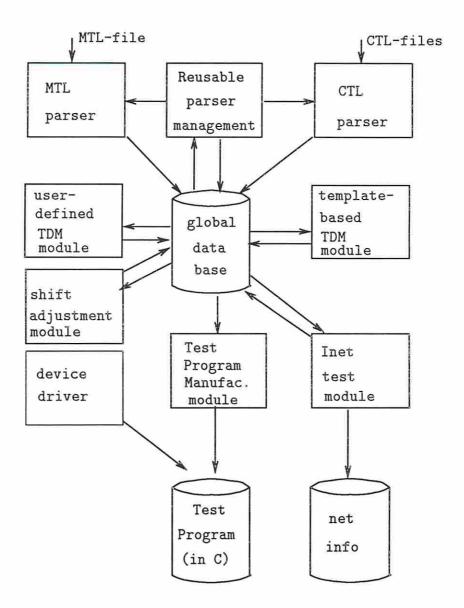

|   |      | 4.2.2  | M2C Synthesizer                                    | 111 |

|   | 4.3  | An Ex  | ample                                              | 121 |

|   |      | 4.3.1  | An MTL-file                                        | 121 |

|   |      | 4.3.2  | CTL-files                                          | 122 |

|   |      | 4.3.3  | The Interconnect Information                       | 124 |

|   |      | 4.3.4  | Synthesized Test Programs                          | 125 |

|   |      | 4.3.5  | Activities between Processor and Test Channel      | 127 |

|   |      | 4.3.6  | Activities on the Test Bus                         | 128 |

|   | 4.4  | Result | s                                                  | 129 |

| 5 | Glo  | bal Co | ntroller Minimization Using Test Program Synthesis | 132 |

|   | 5.1  | Tradeo | off Curve-Based Minimization                       | 134 |

|   | 5.2  | Algori | thm-Based Minimization                             | 140 |

|   |      | 5.2.1  | One Test Channel                                   | 141 |

|   |      | 5.2.2  | Multiple Test Channels                        |

|---|------|--------|-----------------------------------------------|

|   |      | 5.2.3  | Results                                       |

|   | 5.3  | Discus | ssions                                        |

| 6 | Inte | erconn | ect Test Generation 150                       |

|   | 6.1  | Introd | uction                                        |

|   | 6.2  | Prelin | ninaries                                      |

|   |      | 6.2.1  | Fault Model                                   |

|   |      | 6.2.2  | Notation and Definitions                      |

|   |      | 6.2.3  | Non-Diagnosable Faults                        |

|   |      | 6.2.4  | Diagnostic Resolution                         |

|   |      | 6.2.5  | Previous Results                              |

|   |      | 6.2.6  | Deficiencies in Previous Approaches           |

|   | 6.3  | One-S  | tep Diagnosis                                 |

|   | 6.4  | Two-S  | tep Diagnosis                                 |

|   |      | 6.4.1  | Adaptive Algorithm A1                         |

|   |      | 6.4.2  | Adaptive Algorithm A2                         |

|   |      | 6.4.3  | Comparison with Other Adaptive Algorithms 169 |

|   | 6.5  | Diagno | osis Using Structural Information             |

| 7 | Inte | rconne | ect Test Scheduling 175                       |

|   | 7.1  | Introd | uction                                        |

|   | 7.2  | Testin | g Model                                       |

|   | 7.3  | The P  | roblem                                        |

|   |      | 7.3.1  | The Use of Multiple Scan Chains               |

|   |      | 7.3.2  | Scheduling Problem in Testing Interconnects   |

|   | 7.4  | Optim  | al Test Scheduling Theorems                   |

|   | 7.5  | An Al  | gorithm for Generating Schedules              |

|   | 7.6  | An Ex  | tension to Full Scan                          |

| 8 | Con | clusio  | ns and Future Research  | 202 |

|---|-----|---------|-------------------------|-----|

|   | 8.1 | On-Cl   | nip Test Controller     | 202 |

|   | 8.2 | Modul   | le Test Controller      | 203 |

|   | 8.3 | Test P  | Program Synthesis       | 204 |

|   | 8.4 | Contro  | oller Minimization      | 204 |

|   | 8.5 | Interco | onnect Test Generation  | 205 |

|   | 8.6 | Interco | onnect Test Scheduling  | 206 |

|   | 8.7 | Future  | Research                | 206 |

|   |     | 8.7.1   | On-chip Test Controller | 207 |

|   |     | 8.7.2   | Module Test Controller  | 208 |

|   |     | 8.7.3   | Test Program Synthesis  | 209 |

|   |     | 8.7.4   | Controller Minimization | 210 |

|   |     | 8.7.5   | Interconnect Test       | 211 |

# List Of Tables

| 2.1 | Test schedule for the complex kernel                                 |

|-----|----------------------------------------------------------------------|

| 2.2 | Microinstruction List for Controller                                 |

| 3.1 | Counter usage                                                        |

| 3.2 | Processor instruction set                                            |

| 4.1 | The numbers used in the shifting                                     |

| 4.2 | Synthesis results for some modules                                   |

| 7.1 | Typical results; (a) $N_S$ , (b) saving $SS$ (in %) on test time 199 |

# List Of Figures

| 1.1  | The architecture of a HTM system                         | 12 |

|------|----------------------------------------------------------|----|

| 1.2  | Partitioning the test controller between the CMC and MMC | 13 |

| 2.1  | A typical boundary scan cell                             | 18 |

| 2.2  | A module having a boundary scan path                     | 18 |

| 2.3  | Test bus architecture of a module                        | 19 |

| 2.4  | The model of a chip with boundary scan architecture      | 20 |

| 2.5  | The boundary scan bus state transition diagram.          | 21 |

| 2.6  | Control model for an addressable register                | 22 |

| 2.7  | The control signals during test mode                     | 23 |

| 2.8  | A LSSD kernel; (a) control signals, (b) control graph    | 25 |

| 2.9  | A general model for the bus-dependent BIT controller     | 26 |

| 2.10 | A BILBO kernel: (a) control signals, (b) control graph   | 28 |

| 2.11 | A complex kernel; (a) control signals, (b) control graph | 30 |

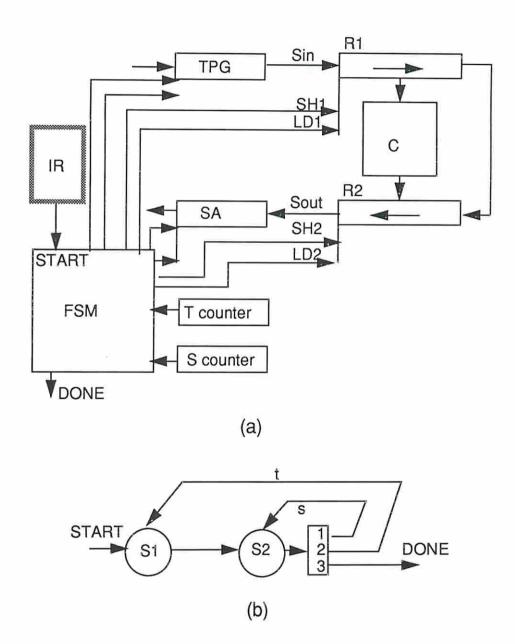

| 2.12 | An autonomous BIT controller for a LSSD kernel           | 39 |

| 2.13 | Testing many kernels in sequence                         | 40 |

| 2.14 | Microprogram controller                                  | 42 |

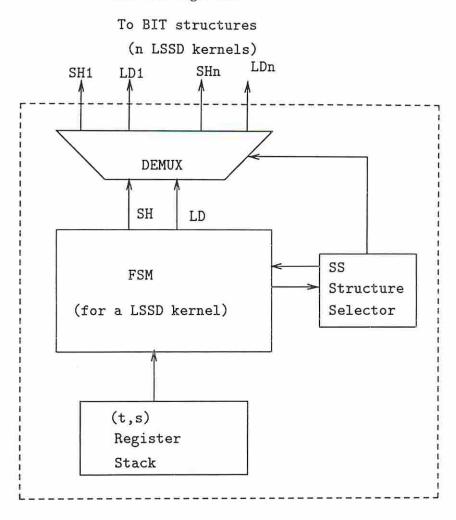

| 2.15 | Interleaved FSM controller                               | 45 |

| 2.16 | A controller for interleaved test execution              | 48 |

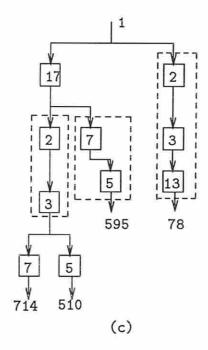

| 2.17 | A Tree-Of-Counter Design                                 | 50 |

| 2.18 | Three Trees-Of-Counters                                  | 52 |

| 2.19 | A counter-Sharing design                                 | 54 |

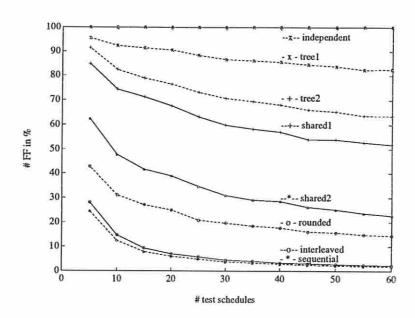

| 2.20 | Hardware complexity for different designs                | 56 |

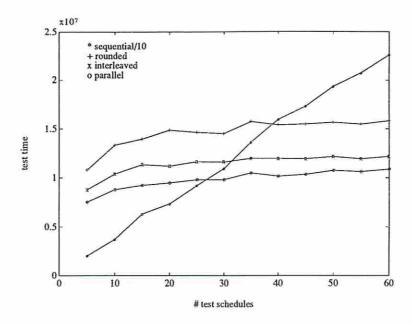

| 2.21 | Time complexity for different designs                          | 58  |

|------|----------------------------------------------------------------|-----|

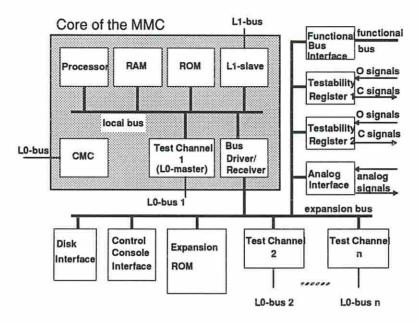

| 3.1  | The architecture of an MMC                                     | 63  |

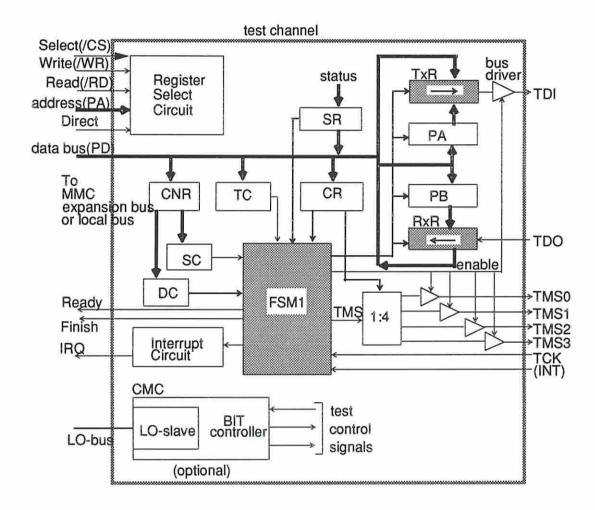

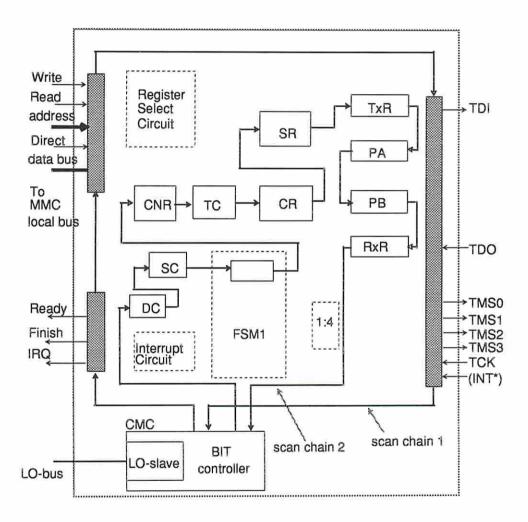

| 3.2  | The architecture of the test channel                           | 65  |

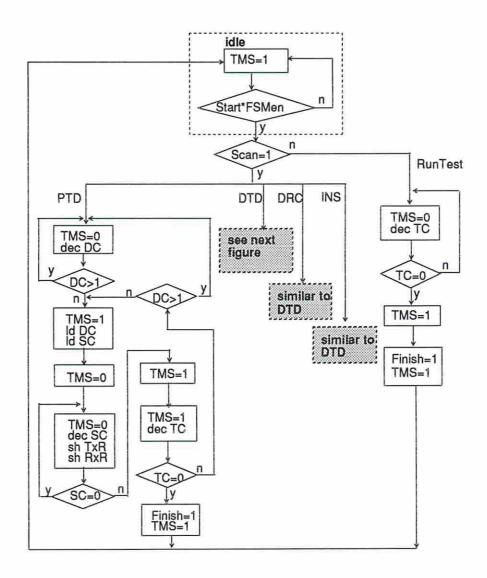

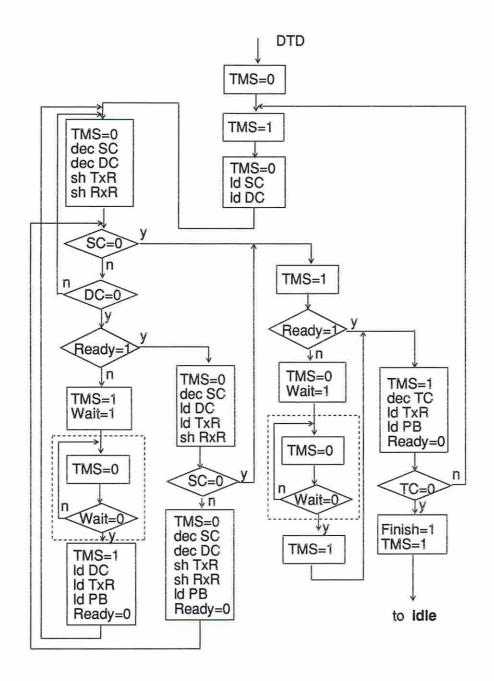

| 3.3  | The state transition diagram for a test channel                | 70  |

| 3.4  | The state transition diagram (cont.)                           | 71  |

| 3.5  | The Bus Driver/Receiver                                        | 74  |

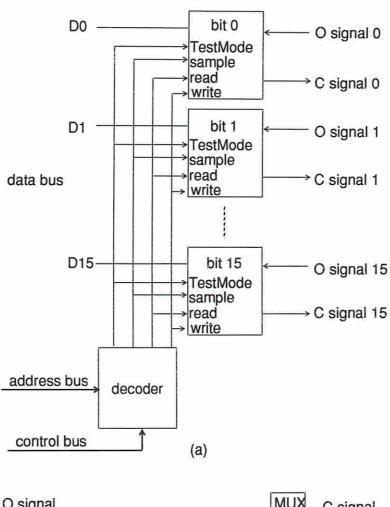

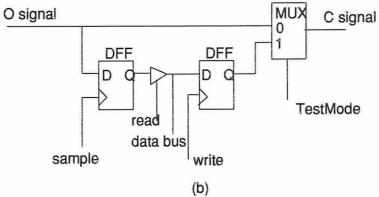

| 3.6  | A Testability Register; (a) block diagram (b) circuit of bit i | 76  |

| 3.7  | Analog Test Interface                                          | 77  |

| 3.8  | Control signals for MR and MRMW instructions                   | 79  |

| 3.9  | Testable design features for a test channel                    | 82  |

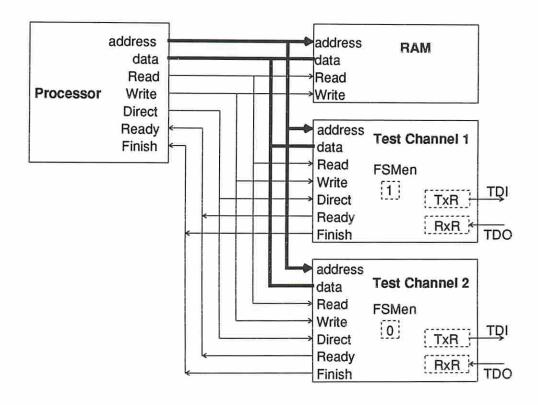

| 3.10 | Physical configuration of the MMC prototype                    | 86  |

| 3.11 | The data bus adaptor                                           | 88  |

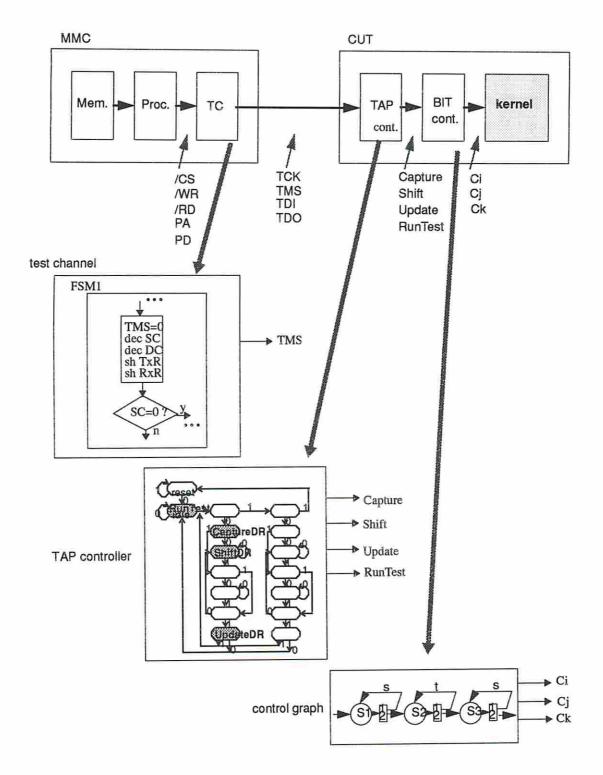

| 3.12 | Overview of the test control                                   | 91  |

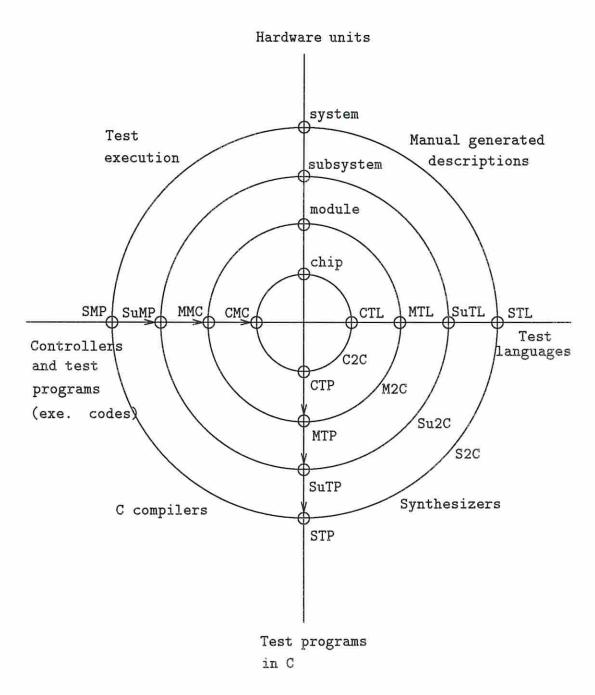

| 4.1  | Overview of the test hardware/software hierarchy               | 04  |

| 4.2  |                                                                | 94  |

| 4.3  | Test control model used in CTL                                 | 97  |

| 4.4  | Test control model used in MTL                                 | 105 |

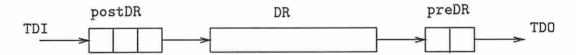

| 4.5  | Scanning a data register in a ring                             | 108 |

| 4.6  | Generating test programs for a module                          | 112 |

|      | The structure of the M2C.                                      | 113 |

| 4.7  | Model for calculating the number of shifting                   | 116 |

| 5.1  | Possible partitions of test resources                          | 135 |

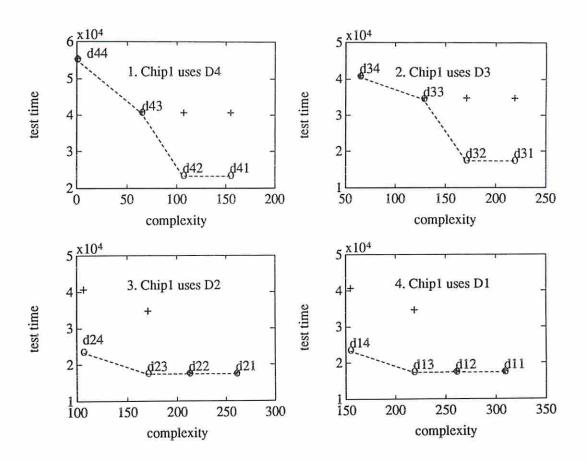

| 5.2  | Test time versus controller complexity                         | 137 |

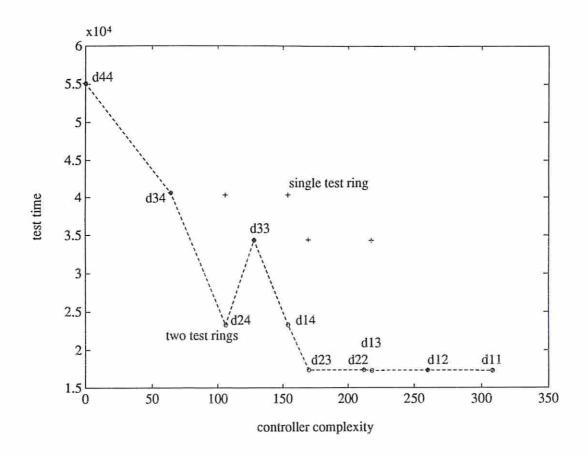

| 5.3  | Tradeoff curve: Test time versus controller complexity         | 139 |

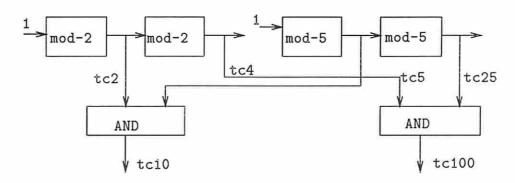

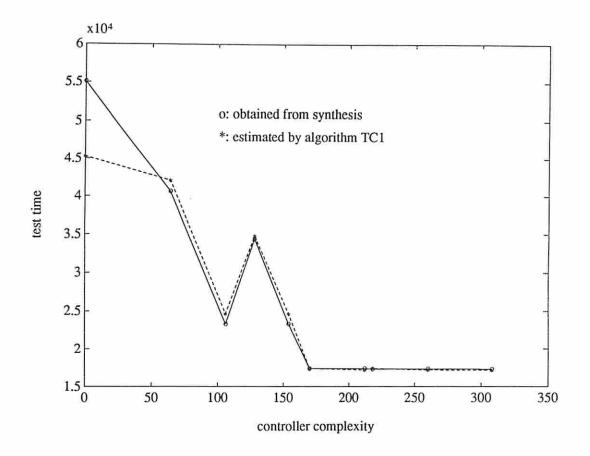

| 5.4  | Test time estimated by algorithm TC1                           | 144 |

| 6.1  | A soft stuck-at 1 case                                         | 153 |

| 6.2  | A short to an opened net                                       | 153 |

|      | An open that is non-diagnosable                                | 155 |

| 6.4  | A short that is non-diagnosable                                                        | 156  |

|------|----------------------------------------------------------------------------------------|------|

| 6.5  | A short that cannot be identified by a diagonally independent sequence.                | .159 |

| 6.6  | An open that cannot be identified by a diagonally independent sequence                 | 159  |

| 6.7  | A short that cannot be identified by an independent test set                           | 160  |

| 6.8  | Achieving maximal diagnosis using a set-cover independent sequence.                    | 164  |

| 6.9  | A deficiency in the W-Test Algorithm.                                                  | 170  |

| 6.10 | A deficiency in the C-Test Algorithm                                                   | 171  |

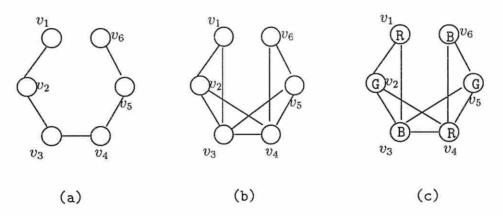

| 6.11 | Example 6-2: (a) the NG, (b) the ANG, (c) the colored graph                            | 173  |

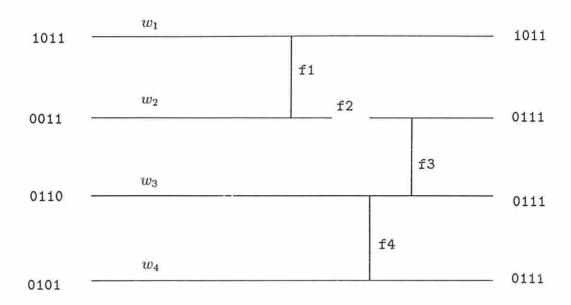

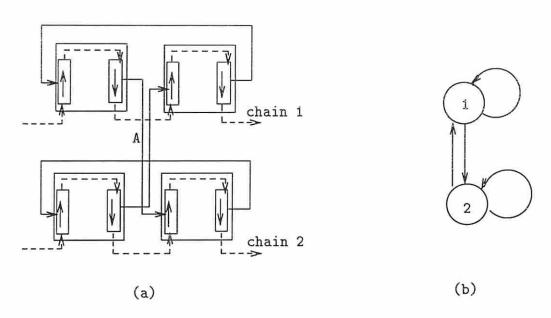

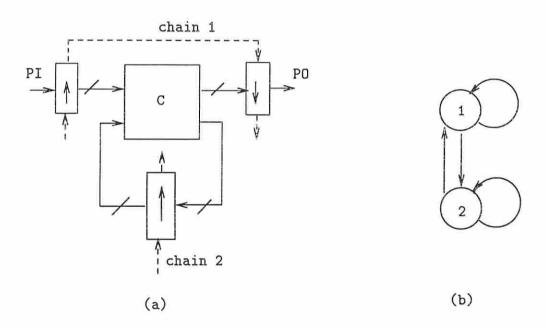

| 7.1  | Test interconnect via two boundary scan chains; (a) block diagram, (b) graph model     | 178  |

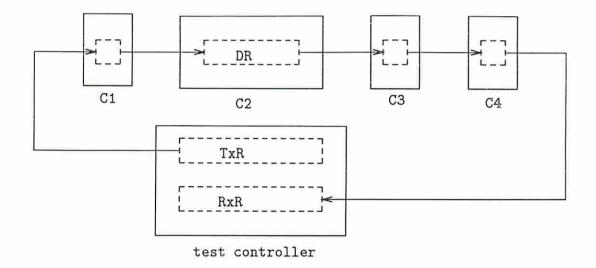

| 7.2  | The test controller model                                                              | 179  |

| 7.3  | Different classes of interconnect                                                      | 181  |

| 7.4  | Two schemes for testing interconnect; (a) distributed control, (b) centralized control | 182  |

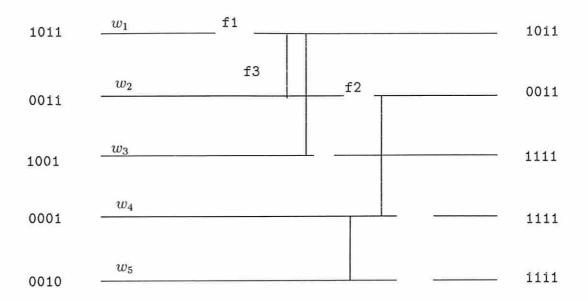

| 7.5  | Deriving test schedules for several examples                                           | 184  |

| 7.6  | Example: Deriving an optimal schedule                                                  | 193  |

| 7.7  | Testing a circuit via two scan chains; (a) block diagram, (b) graph model.             | 201  |

#### Abstract

The cost associated with the test and maintenance of a complex system, which includes test generation, and detection, location and repair of faulty components, represents a significant portion of the overall life-cycle cost. This cost can be drastically reduced if testability and maintainability techniques are properly incorporated in the system design. Despite its importance, most systems are built with insufficient or no concern for testability and maintainability. This is mainly due to costs related to design-for-test structures, in designing test controllers, and the development of test programs.

This thesis presents a tool called BOLD that assists in the design of a system with extremely high degree of testability and maintainability. A system designed using BOLD is testable and maintainable at every level of the design hierarchy, i.e., chips, modules, subsystems and the system, since test controllers are employed in the hierarchy. Test busses are used to allow communication between test controllers. Methods for designing various test controllers are also presented along with some example designs. To describe the test aspects of various hardware units, a set of high-level languages are provided. These languages can be used by designers with little or no knowledge of testability. Tools are provided to synthesize test programs from these descriptions. These test programs are then compiled and executed by controllers so that hardware units can be tested. These test programs include test for the interconnect between chips. The test synthesis approach also provides the capability of predicting test time before the controllers are actually built. Given a bound on system test time and a requirement on system testability and maintainability, BOLD can quickly search the whole design space to provide the designer with the best solution satisfying the requirements of test time and hardware overhead.

#### Chapter 1

#### Introduction

#### 1.1 Background

The increased complexity of modern digital systems has significantly increased the costs associated with the activities of test generation, detecting, locating and repairing faulty components. These activities are referred to as the test and maintenance of a system. For a complex system, these costs constitute a significant portion of its overall life-cycle costs.

Current approaches to system test and maintenance often employ a three level maintenance scheme. System self-test is initiated by personnel with little training. If a faulty field replaceable unit is found, it is replaced with a working spare. The faulty unit is then sent to a shop, where a technician uses sophisticated equipment to isolate the fault to a shop replaceable unit. The faulty unit is then discarded or sent back to a depot, where a well trained technician can locate a faulty component down to a minimum replaceable unit, such as a chip, and repair the unit.

This form of testing often encounters several problems such as those listed next: (1) the unreliability of the tester; (2) the increased time and skill required of maintenance personnel; (3) the loss of system capability when the tester failed; (4) the cost and quality in developing test software; and (5) the so-called Cannot Duplicate (CND) and Retest Okay (RTOK) problems. The problem of Cannot

Duplicate refers to the situation where one level of test and maintenance indicates a failure in a unit, while the next level cannot detect a fault in the unit. This is in part due to intermittent faults and/or differences in test procedures used at various level of testing. The problem of Retest Okay refers to the situation where the fault isolation capability is insufficient. Therefore, instead of sending the faulty unit to the next level of test, a good unit is sent. Thus no fault can be identified at the next level. It has been pointed out in [49] that the false alarm, which is the major factor in lowering the system readiness and availability, is closely related to both Cannot Duplicate and Retest Okay.

The major causes of these problems, which have been identified in [11], are (1) mode of operation dependency, referring to test procedures which can be executed at one level of the system hierarchy but not at other levels; (2) environmental dependency, which means that a failure is caused by such conditions as temperature or vibration; (3) false alarms due to design error or transient faults; (4) inadequate fault isolation; (5) incompatibility of tests and test tolerances, which is caused by the inconsistent testability and maintainability techniques used in different levels of testing; (6) system parameters which are out of specification; (7) faults in Built-In Test (BIT) hardware; (8) test data unaccessible; and (9) other causes which we have no knowledge about.

To reduce the cost of test and maintenance, one needs to design a system so that the above mentioned problems and their causes can be eliminated or at least reduced. Such a system would then have a high degree of testability and maintainability. In addition, the system should be able to perform self-test with a high degree of fault coverage. This leads to a two level maintenance scheme, where the shop level is eliminated, resulting a tremendous reduction in test and maintenance cost.

In summary, the ideal system should be able to (1) improve fault isolation capability; (2) eliminate the mode of operation dependency; (3) unify test and test tolerance among different levels of testing; and (4) detect faults in BIT hardware. Various issues related to the design of such a system are addressed in this work.

#### 1.2 Previous Work

Previous work provides partial solutions for the problem of designing a system with a high degree of testability and maintainability. Work has been done in the areas of system architecture, testability busses, testable chip design, testable module design, interconnect test and test scheduling. However, a complete solution that deals with both the hardware and software aspects of the problem is not available. The BOLD system presented in this thesis can provide such a complete solution. Previous work that addresses various aspects of the problem is briefly described below.

#### 1.2.1 System Architecture

Several system architectures to support system level design for testability and maintainability have been proposed. These architectures share features such as hierarchical design and component built-in self-test (BIST) capability.

Haedtke et al. [27] proposed a multilevel self-test architecture. Each level of integration of the system is assumed to have BIST capability and is controlled by a maintenance processor. A standardized test bus and a standardized BIST control protocol are required to enable simultaneous self-test of all chips. These same standardized interfaces and protocols are used by the maintenance processor in both the factory and field test. The lower level tests remains valid at each higher level of integration. Using this architecture, the system test and maintenance cost can be greatly reduced. The system self-test is carried out by the maintenance processor, which must be first tested by an external tester. It is not clear how the maintenance processor will be tested if no external tester is available. Thus the capability of system self-test is not assured.

IBM's Common Signal Processor architecture [19] is designed with built-in test and maintenance capability. Each chip has an on-chip monitor to control the chip's BIST circuitry. Each functional module is associated with an element supervisor unit and an element control bus. The former can access the on-chip monitor through an element maintenance bus. A subsystem manager controls all the element supervisor units via a pi-bus. The Common Signal Processor architecture incorporates the test and maintenance hierarchy in accordance with the system functional hierarchy.

TRW employs a hierarchical architecture for the system test and maintenance nance [48]. A system maintenance node controls several functional maintenance nodes via a subsystem maintenance bus. A functional maintenance node controls several module maintenance nodes via a module test bus. A module maintenance node controls several device maintenance nodes via a device test bus.

The TEA system [62] also employs a hierarchical test methodology. Each board is made testable by inserting a *Test Switch* between every pair of *Ambiguity Groups*. An Ambiguity Group is the basic unit of circuitry to be tested. The test process of the board is controlled by a maintenance node, which is controlled by a subsystem test control unit, which is in turn controlled by a system test control unit.

#### 1.2.2 Testability Bus

A great amount of effort has recently been focused on the interoperatability among products from different vendors. Interoperatability can be assured by using a standard test bus. Some major initiatives for the standardization of test busses are listed below.

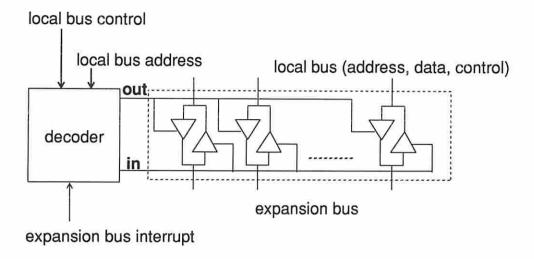

TM/ETM initiatives [20, 60] A VHSIC subcommittee consisting of IBM, Honeywell and TRW proposed the TM/ETM test busses. The Element Test and Maintenance (ETM) bus [20] was to be the standard testability bus for VHSIC chips. It consists of 6 signal lines, namely CLK, DI, DO, Mode, Control, and Interrupt. Recently the ETM bus protocol has been modified to be compatible with the IEEE Std. 1149.1, which combines the Mode and Control into a single line (TMS) to reduce the overhead of pin count.

The Test and Maintenance (TM) bus [60] was proposed to be used as the backplane test bus. It consists of four lines, namely Clock, Control, MD and SD.

The bus configuration uses a multi-drop architecture, so that the addition/removal of other modules to/from a backplane will not affect the testability operation of other modules.

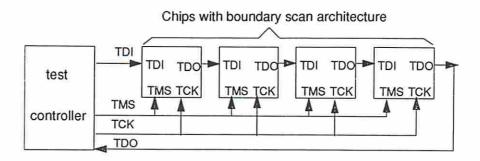

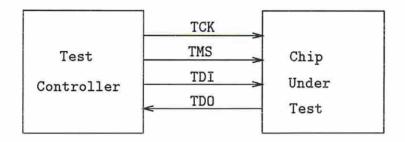

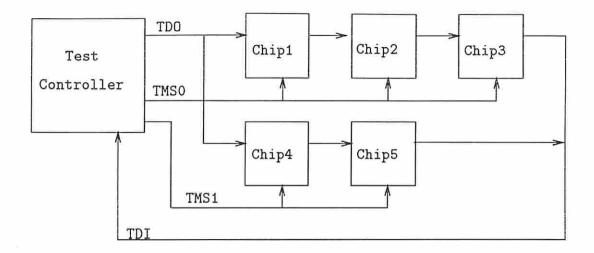

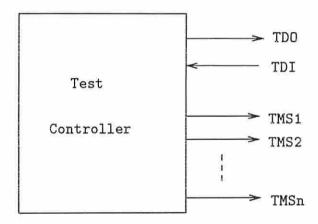

IEEE Std. 1149.1 [33] The Joint Test Action Group (JTAG) proposed a standard test architecture, which became the IEEE Std. 1149.1. The bus consist of four signal lines, namely TCK, TMS, TDI and TDO. The TCK is the test clock line; the TDI is the serial data input line; the TDO is the serial data output line; and the TMS is the control line which controls the state of a Test Access Port (TAP) that resides on each chip. One of the main objectives of the IEEE Std. 1149.1 was to minimize both pin count and area overhead associated with the test bus.

IEEE P1149.x initiatives [61] The IEEE P1149 Testability Bus Standardization Committee was formed in an effort to standardize one or more testability busses [33, 61]. The P1149.x (x=2,3,4) proposal includes four subsets that could be used individually or in any combination. These subsets are the P1149.2 Extended Serial Digital Subset, the P1149.3 Real Time Digital Subset and the P1149.4 Real Time Analog Subset. These initiatives, once approved, will become the IEEE standard 1149.

#### 1.2.3 Testable Chip Control Model

Craig et al. [18] proposed a hierarchical test control scheme. In this scheme, a piece of automatic test equipment (ATE) controls a level 2 supervisor, which controls several level 1 supervisors which in turn controls the Test Control Logic in self-testable units, which are the basic unit for test scheduling and test application. In addition to the Test Control Logic, each self-testable unit contains several test resources and a circuit block under test. A problem occurs when a test resource, such as a signature analyzer (SA), is shared among several units. Each Test Control Logic in these units must provide a set of control signals to the test resource. Since the test resource can only be controlled by a single set of control signals, control signals provided by different Test Control Logic blocks must be combined (either

wired ORed or ANDed). This not only increases area overhead but also slows down the functional operation.

Beausang and Albicki [7] proposed a model for self-testable chips. Their model describes test resources, the test distribution network, the test controller and the test procedure in mathematical form. Necessary and sufficient conditions for a test controller to implement a test procedure are also derived. The problem of interfacing this model to a standard test bus is not treated. Thus, it is not clear how to incorporate their work with an external test controller, such as an MMC.

#### 1.2.4 Testable Chip Design

Avra [5] proposed a design for an ETM-BUS compatible on-chip test and maintenance controller (TMC). The controller, under the control of an ETM-BUS, can direct the chip under test to perform five different operations, namely functional, debug, reset, serial scan and built-in self-test. The controller consists of control logic, command decode logic, parity logic and three registers, namely transfer register, Command Register and Status Register. The Transfer register and the Status register are converted into a test pattern generator (TPG) and a parallel signature analyzer (PSA) during built-in self-test mode. The overhead of a TMC is 6 I/O pins and about 500 gates. The problem of synchronizing the system functional clocks and the the test bus clock is not considered.

Whetsel [33, 65] proposed a design for the Test Access Port used in the boundary scan architecture. In this design, edge-triggered flip-flops are used as the basic storage elements. Clock inputs of flip-flops are allowed to be gated. The total gate count for this design is about 80 and the pin count is 4. Compared to the design of the controller proposed by Avra, the overhead of this design is small. This design is suitable for most chips. Whetsel also did not address the problem of synchronizing functional and test clocks.

LeBlanc [41] reported on a built-in self-test technique, called LOCST, for chips designed at IBM using level sensitive scan design (LSSD). LOCST utilizes onchip pseudorandom pattern generation, on-chip signature analysis, boundary scan and an on-chip monitor as the test controller. The monitor includes a standard maintenance interface with seven dedicated signal lines. The major functions of an monitor are scan string control, error monitoring and reporting, chip configuration control, clock event control, run/stop single cycle and stop on error. The boundary scan chain can be used to test external logic, which cannot be tested by the monitor. The advantages of this technique are low area overhead (< 2%), design independent implementation and effective static testing. The key drawback of using a monitor is the high I/O pin count overhead.

#### 1.2.5 Testable Module Design

Budde [15] presented a board test controller called Testprocessor. Testprocessor can control the test process of a chip through a dedicated test bus. Since a Testprocessor is designed for use on either a printed circuit board or a VLSI chip, its functionality is limited by area constraints. The only data processing unit in a Testprocessor is a fault-secure comparator. Due to its limited data processing capability, diagnostic programs cannot run on a Testprocessor.

The TEA [62] system employs a Maintenance Node to make a board testable. Test Switches are added to a board to increase its testability and controllability. Ambiguity groups are first identified. A Test Switch is then inserted between every pair of Ambiguity Groups. The Maintenance Node uses 10 signal lines to control all the maintenance activities of the board.

Babiak et al. [48] reported on a module BIST scheme using Module Maintenance Nodes, one of which is embedded in every module and is controlled by a Maintenance And Diagnostic System that contains a processor to run both test and diagnosis programs.

#### 1.2.6 Interconnect Test Generation

The IEEE Std. 1149.1 requires that every chip be built with the boundary scan architecture, where each I/O pin is associated with a scan cell. By shifting data

along a chain consisting of these scan cells, the interconnect between chips can be easily tested. This helps subdivide the test problem and leads to increased fault isolation capability.

Kautz [37] derived a minimal test set for detecting opens and shorts in a wiring network. The number of test required is  $p-1+\lceil log_2q\rceil$ , where p is the number of terminals in the largest interconnect net in the network, and q is the total number of nets. This result has become the foundation of later work on interconnect testing.

Wagner [64] presented a method for testing interconnections using boundary scan registers. Both stuck-at faults and shorts are considered. Stuck-at faults are tested for free while testing for shorts. By complementing the test vector set, faults can be located. For n 2-point nets,  $2 \times log_2 \lceil (n+2) \rceil$  tests are required. The order of the I/O pins in the boundary scan chain must be given. If tristate pins and bi-directional pins are included, additional tests are required.

Hassan et al. [29, 30] extended the minimal test set for interconnect test developed by Wagner [64] to a generalized test set, where information on the order of the I/O pins is not required. He also presented several BIST schemes for interconnect test using the boundary scan architecture. Walking ones and zeroes sequences are proposed as efficient test patterns. Several in-place diagnosis schemes are also presented, including a modifier sequence for area efficient built-in diagnosis.

Jarwala and Yau [34] have developed a comprehensive framework for dealing with the test and diagnosis of interconnect. In addition, a diagonally independent property is identified. They also proposed the C-Test algorithm which can generate a minimal test set for identifying all shorts and opens in a network. Their results are valid only if a net is not involved in both opens and shorts at the same time.

Cheng et al. [16] researched the self-diagnosis property. Constant weight codes are proposed to achieve self-diagnosis. In addition, several optimal adaptive algorithms are proposed for deriving test sets that achieve the self-diagnosis property.

All these results are based on the assumption that a net cannot be involved in both open and short faults. When this assumption is removed, these results are invalid.

#### 1.2.7 Test Scheduling

Abadir and Breuer [3] solved the problem of optimizing the execution schedule of a test plan for a single test block. A resource conflict graph is used to indicate the sharing of a resource at different steps of a test plan. They showed that the lower bound on the time delay (D) between the initiation of two tests is equal to the chromatic number of the conflict graph. No-operation steps (no-ops) are inserted into a test plan to get an optimal test schedule. The problem of scheduling multiple test blocks was not addressed.

Craig, Kime and Saluja [18] addressed the problem of scheduling multiple test blocks. Unlike Abadir and Breuer's work, they assumed that all test blocks have their D values equal to one. Assuming all test blocks have the same test length, they constructed an algorithm to minimize the number of concurrent test sets, which are defined as a set of tests that can be executed in the same test session. The same algorithm is then extended to solve the scheduling problem for test blocks with unequal test lengths. The problem of test blocks with D value greater than 1 was not dealt with.

Sayah and Kime [58] dealt with the problem of scheduling multiple test blocks with a complex test plan. Unlike previous work, which considers only a single aspect of test parallelism, a broader consideration including both time and space parallelism is taken. Based on a resource allocation graph and a so-called delta graph, they found a good heuristic algorithm for the scheduling of tests.

The work discussed above does not take into consideration the control structure that implements the scheduling process. Also, the problem of scheduling test at the module and subsystem level has not yet been addressed.

#### 1.3 The Design Approach

A systematic design technique, called the hierarchically testable and maintainable (HTM) design methodology, is addressed in this work. Adopting the HTM methodology at all levels of the physical hierarchy of a design, i.e. chip, module, subsystem and system, will increase system availability and significantly lower hardware life cycle costs. A system designed with such a methodology is called an HTM system.

A design-for-test tool called BOLD is presented in this work. BOLD is a tool that supports both the hardware and software design of an HTM system. In the hardware support, a set of test controllers to execute the test process of different testable units are provided. In the software counterpart, a set of high level languages to describe the test aspects of these units are provided. Tools are also provided such that these descriptions can be translated into executable code for the test controller. BOLD also provide the necessary tool for automatically testing interconnects among different units.

In designing an HTM system, there exists tradeoffs between the test time and the hardware complexity of test controllers. From a designer's point of view, the goals are to reduce both the test time and hardware overhead. These are two conflicting requirements since in general more hardware has to be added to the test controllers to reduce test time. Using the capability of automatic synthesis of test programs provided by BOLD, the overall test time of an HTM system can be quickly predicted. Hence the whole design space is quickly explored in choosing a feasible solution.

#### 1.4 The Hierarchical Test Methodology

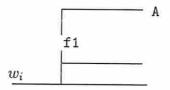

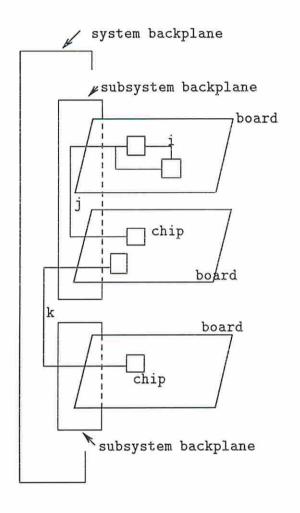

A hierarchy of test controllers is employed in a system designed with the hierarchical test methodology. These controllers are distributed among each level of the physical hierarchy. In such a system, which is referred to as an HTM system, each VLSI chip has an on-chip test and maintenance controller (CMC); each module (or board) has a module test and maintenance controller (MMC); each subsystem has a subsystem

test and maintenance controller (SuMP); and each system has a system test and maintenance controller (SMP). These controllers participate in all system test and maintenance activities, and communicate via test busses.

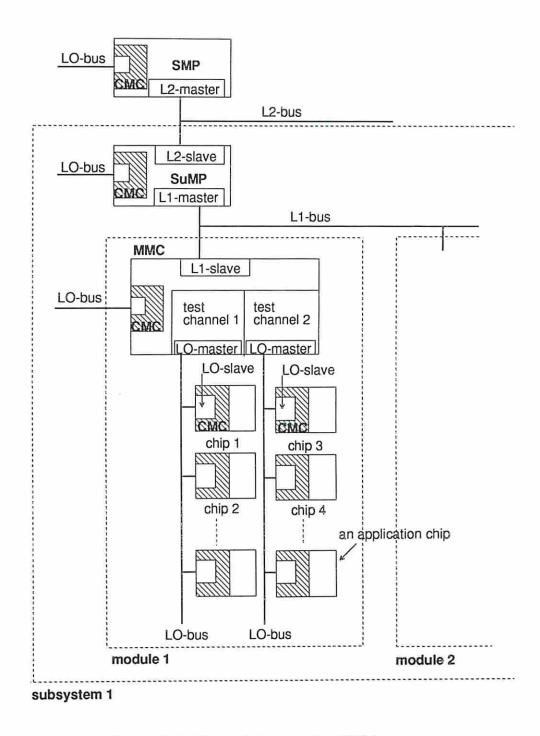

Figure 1.1 shows part of the test hierarchy for four levels of test hierarchy. Different busses may be used for communication between different levels. The SMP communicates with SuMPs through a Level 2 bus (L2-bus); a SuMP communicates with MMCs through a Level 1 bus (L1-bus); and an MMC communicates with CMCs through a Level 0 bus (L0-bus). The IEEE 1149.1 [33] boundary scan bus is used as the L0-bus throughout this work.

**Pros and cons** Advantages of the hierarchical test methodology include the following:

- 1. Lower level tests remain valid at higher levels of the design hierarchy.

- 2. Interoperatability at each level of subassembly due to standardized interfaces.

- 3. Increased fault isolation capability provided by boundary scan.

- 4. Reduced testability and maintainability (T&M) design time.

- 5. Reduced maintenance time due to consistent T&M techniques.

- 6. Increased system availability due to reduced maintenance time.

- 7. Increased reliability due to increased test effectiveness.

- 8. Reduced overall test and maintenance cost.

The disadvantages of such a hierarchical test methodology are the controller hardware overhead and also that components with standardized interface are required.

The following example shows how a circuit can be tested when the HTM methodology is used.

Figure 1.1: The architecture of a HTM system.

#### 1.5 Test Controllers for a Circuit

There are numerous testable design methodologies (TDMs) that can be used to make a circuit testable. In selecting a TDM, criteria such as total test time, area overhead, and circuit performance degradation must be considered. Tradeoffs often need to be made so that design constraints and goals are satisfied. It is possible to automate such a selecting process by employing an expert system [2, 69]. Once a TDM for a circuit is selected, the associated BIT structure and test plan can be derived.

To execute such a test plan a test controller is required. The test controller configures the circuit for testing and controls the execution of the test. In addition, it may also generate test data and analyze test results. Not all aspects of the controller need be on-chip. Some of the possible tradeoffs are considered in this example.

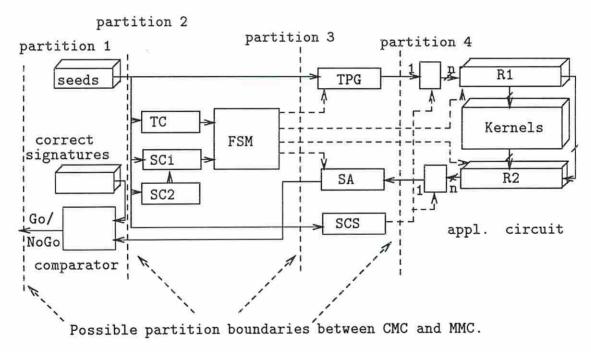

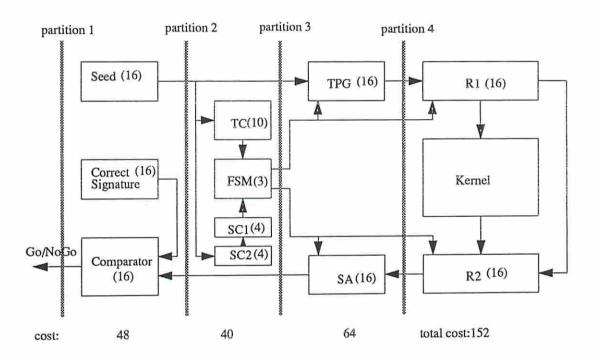

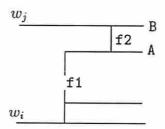

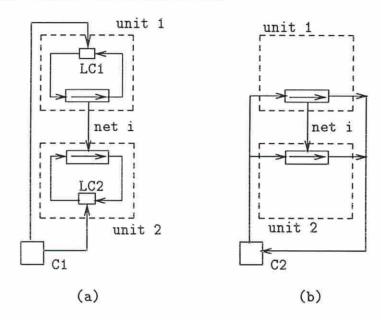

Figure 1.2: Partitioning the test controller between the CMC and MMC.

Partitioning the test controller: Suppose the BIT structure of an application circuit consists of one or more scan loops (see Figure 1.2). The test plan for a loop is as follows: (1) shift in a test vector; (2) latch the response data into the scan

register; and (3) shift the test results out of the loop while shifting in a new test vector. This process is repeated t times, where t is the number of test vectors.

Assume test vectors are to be generated by a serial test pattern generator (TPG) and the results compressed by a serial signature analyzer (SA). A complete test controller must have the following hardware facilities (or test resources) to carry out this test process: a TPG to provide the test vectors, a SA to compress the test results, a counter TC to keep track of number of the test vectors, one counter SC1 and a register SC2 to keep track of the number of shifts for each vector, seeds vectors for various registers such as the TPG and SA, a stack containing correct signatures, a signature comparator, a register SCS for scan chain selection, and a finite state machine to control the test process.

Several different configurations for these test resources are possible. Figure 1.2 shows four possible partitions of these resources between on-chip and off-chip controllers, i.e., CMC and MMC. Once partitioned along some boundary, an interface or bus is required to connect the two partitions. For example, a boundary scan bus is used for an MMC to communicate with a CMC. The CMC must have a slave interface and the MMC must have a master interface.

Partition 1 puts all resources into the CMC. Such a CMC is capable of executing a test process completely on its own, once initiated by the MMC. After t test vectors have been applied to the kernel, the signature is compared with the correct one. The CMC then reports only the Go/NoGo status to the MMC through the boundary scan bus.

Partition 2 incorporates the seeds, correct signatures and the comparator into the MMC while leaving the rest of the resources in the CMC. The MMC first loads the seeds into the TPG, SA, SCS, TC, SC1 and SC2 registers in the CMC via the boundary scan bus. The CMC then generates and applies test vectors to the test kernel and the test results are compressed in the SA. After t test vectors have been applied, the CMC requests that the MMC read the signature in the SA via the boundary scan bus. The MMC then compares the signature with the correct one and determines the health status of the kernel by generating a Go/NoGo indication.

Partition 3 keeps the TPG and the SA in the CMC while putting the rest of the test resources in the MMC. The MMC must provide control signals for the BIT structures, the TPG and the SA. All control signals must be derived from the test bus directly during the test process. The MMC keeps track of the number of shifts for each test vector and the total number of the test vectors that have been applied to the kernel. After t vectors have been applied, the MMC then reads the signature out of the CMC. A comparison is made against the correct signature to determine the health status of the kernel.

Partition 4 puts all the before mentioned test resources into the MMC. The CMC is simply a boundary scan bus slave interface. The complexity for this MMC is maximal and corresponds to the concept of a test channel, which will be described later. The MMC must provide test vectors and collect test results through the test bus. Control signals for the on-chip BIT structures are also provided by the MMC through the boundary scan bus.

An MMC can control several CMCs through a bus. The hardware partitions may be any of the four mentioned above. In fact they can be different for each chip. To be able to control any CMC, the MMC must not only have the resources dictated by partition 4, but even additional capabilities in order to control BIT configuration other than just scan chains using random data. Test resources in the MMC can be shared by the CMCs, while resources in a CMC cannot be shared by other CMCs. Obviously, the more test resources in the CMC the higher degree of test execution parallelism that can be achieved, thus leading to a reduction in total test time.

#### 1.6 Thesis Outline

This thesis is organized as follows. The designs of test controllers are presented first. On-chip test controllers are described in chapter 2, followed in chapter 3 by a test controller for testable modules. The generation of test programs is described in chapter 4, where test description languages are presented along with various synthesis tools. The results of test program synthesis for several examples are also

shown. Chapter 5 deals with how the synthesis technique facilitates the minimization of test controller complexity. The issue of testing interconnect among different hardware units is described in chapters 6 and 7. In chapter 6, a new fault model is presented along with theorems and algorithms for deriving test sets to identify all faults. In chapter 7, the problem of actually applying a test set to test interconnect is investigated. Theorems and algorithms are provided so that a schedule can be constructed to achieve minimal test time. Conclusions and future work are given in chapter 8.

#### Chapter 2

#### Controllers for Testable Chips

#### 2.1 The Model

In this chapter the design of one or more on-chip test controllers (CMC) for testable chips are presented. A testable chip is assumed to have some DFT or BIST features which can be controlled through a boundary scan bus. It consists of a CMC and an application circuit. The CMC in turn contains a bus interface, called L0-slave, and a Built-In Test (BIT) controller. The IEEE Std. 1149.1 boundary scan bus is used as the test bus in this work. A detailed description of this standard can be found in [33]. For convenience, a brief introduction of the boundary scan architecture is given below.

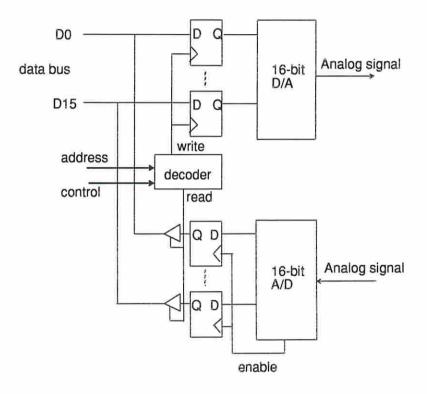

#### 2.1.1 Boundary Scan Architecture

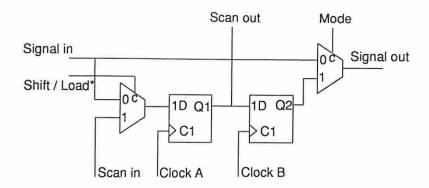

The boundary scan technique requires the inclusion of a scan cell for each I/O pin of a chip. A typical boundary scan cell is shown in Figure 2.1. A boundary scan register is formed by cascading all the boundary scan cells. During normal operation, the scan cells are transparent to the operation of the chip except that a multiplexer delay is added to each I/O pin. During test operation, the logic values of these I/O pins can be captured into the first flip-flop (Q1) and then shifted out for observation; meanwhile, new values can be shifted in and transferred to the output

Figure 2.1: A typical boundary scan cell.

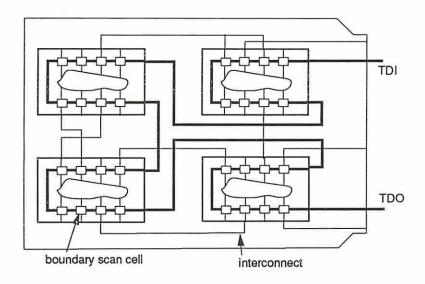

of these cells. A boundary scan module contains chips that have this boundary scan architecture. A scan path can be formed by cascading all the boundary scan registers (see Figure 2.2). This scan path can be used in two ways: (1) to allow the interconnects between the various chips to be tested, and (2) to allow the chip on the module to be tested.

Figure 2.2: A module having a boundary scan path.

The boundary scan bus consists of at least four signal lines, namely TDI, TDO, TMS, and TCK. A fifth signal line TRST\*, which is not shown here, is optional. The TCK line provides the clock for the test logic in the LO-slave. The logic value

Figure 2.3: Test bus architecture of a module.

of the TMS line is decoded by an on-chip test controller to control test operations. The TDI line provides serial instruction and data to be received by the test logic of the chip. The TDO line is the serial output for test instruction and data from the test logic of the chip. One test bus architecture is shown in Figure 2.3.

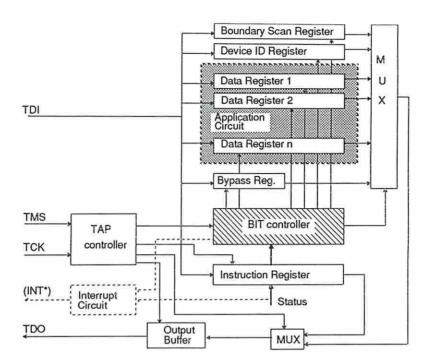

The boundary scan architecture of a chip is shown in Figure 2.4. The shaded area labeled as application circuit is the circuit designed with a predefined BIT methodology. During the test mode, many scan registers are formed in the application circuit. These scan registers can be used to control the test process of the circuit. The unshaded area consists of the Test Access Port (TAP), which can also be referred to as the L0-bus slave, and is required in a chip with the boundary scan architecture. The TAP consists of a TAP controller, an instruction register (IR), a boundary scan register, a one-bit bypass register, an optional device identification register (ID), and multiplexers. The hatched area labeled as the BIT controller contains additional (optional) test facilities for controlling the test process of the application circuit. The CMC consists of the TAP and the BIT controller.

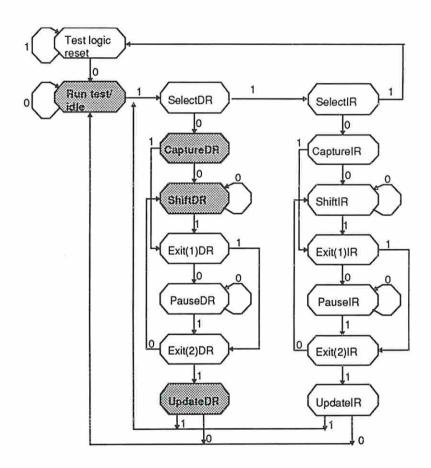

The state transition diagram of the TAP controller is shown in Figure 2.5. The states are represented by the values of the flip-flops used in the TAP controller. The state transition is controlled by the logic value of the TMS line. Each state has two possible next states, designated by the two outgoing directed edges. The state transition follows the edge with label 1 if the current value of the TMS line is 1, otherwise the edge with label 0 is followed. The Reset state is entered whenever

Figure 2.4: The model of a chip with boundary scan architecture.

the TAP controller is reset, which can occur when the system power-on-reset is activated or the TMS line is held high for more than 5 consecutive TCK clock cycles. The Run-Test-Idle state is entered when executing the self-test activities, or when the chip is in test mode with no ongoing test activity.

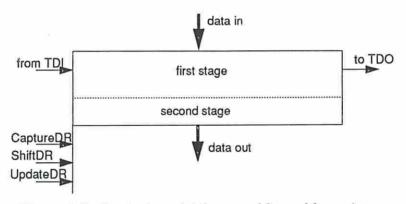

Two major branches are used to transmit instructions and data. When transmitting instructions, the number of activations of the state ShiftIR equals the number of instruction bits sent. A new instruction is loaded into the IR register when the UpdateIR state is activated. The contents of the IR determines the operation of the on-chip test controller. One major function of the data in the IR is to select a data register for scanning. When transmitting data, both the CaptureDR and UpdateDR states are activated exactly once for each transmission. The number of activations of the ShiftDR state equals the number of data bits sent to the selected DR. By properly driving a TAP controller, a module level test controller can send/receive both instructions and data to/form a chip. This information controls the test execution of the chip.

Figure 2.5: The boundary scan bus state transition diagram.

During the test mode, all test control signals are controlled by the BIT controller, which in turn is controlled by the contents of the IR and the current state of the TAP controller. Signals generated from the TAP controller include RunTest, Capture, Shift and Update, and are active during the state Run-Test-Idle, CaptureDR, ShiftDR, and UpdateDR, respectively. Only one of these four signals can be active at a time. Also, the sequence of activation of these signals must be consistent with the state transition diagram described previously.

When a register is selected for scan, the control signals must be designed in such a way that the logic values of the inputs to this register are captured when the TAP state is in CaptureDR. The selected register is shifted whenever the TAP state is in ShiftDR. Throughout this work it is assumed that the output of an addressable register is updated only when the TAP state is ShiftDR, i.e., an implicit HOLD mode is assumed for all addressable registers. Figure 2.6 shows a general model for an addressable register.

Figure 2.6: Control model for an addressable register.

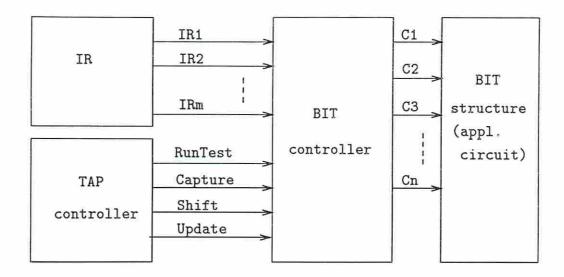

The control signals of a testable chip during the test mode are shown in Figure 2.7. The signals C1, C2, ..., Cn control the test execution of the application circuit, which has been built using some BIT methodologies. The signals IR1, IR2, ..., IRm are the output of the IR. Registers in the application circuit must hold their data when the TAP controller is in certain states, such as Exit(1)DR, PauseDR, SelectDR. This can be done using an explicit hold control signal or by disabling the clock.

Figure 2.7: The control signals during test mode.

Based on the dependence of the test bus, BIT controllers can be grouped into two categories; bus-dependent and autonomous BIT controllers. During the testing of the application circuit, a bus-dependent BIT controller uses the lines Capture, Shift, Update and RunTest; while an autonomous BIT controller uses only the RunTest line. In the other words the operation of a bus-dependent BIT controller depends on the state transitions of the test bus during the entire test execution process. The operation of an autonomous BIT controller is independent of the bus state transitions once it has been properly initiated. In general, an autonomous controller has a higher hardware complexity than a bus-dependent controller.

# 2.2 Bus-Dependent BIT Controllers

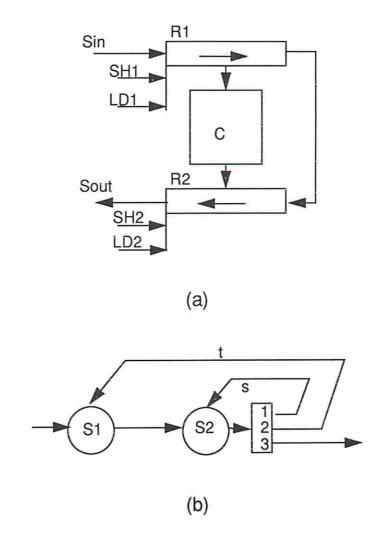

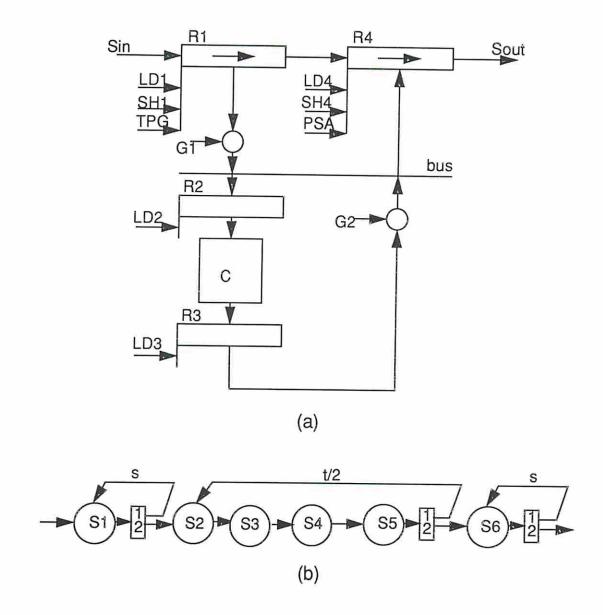

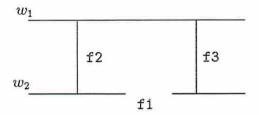

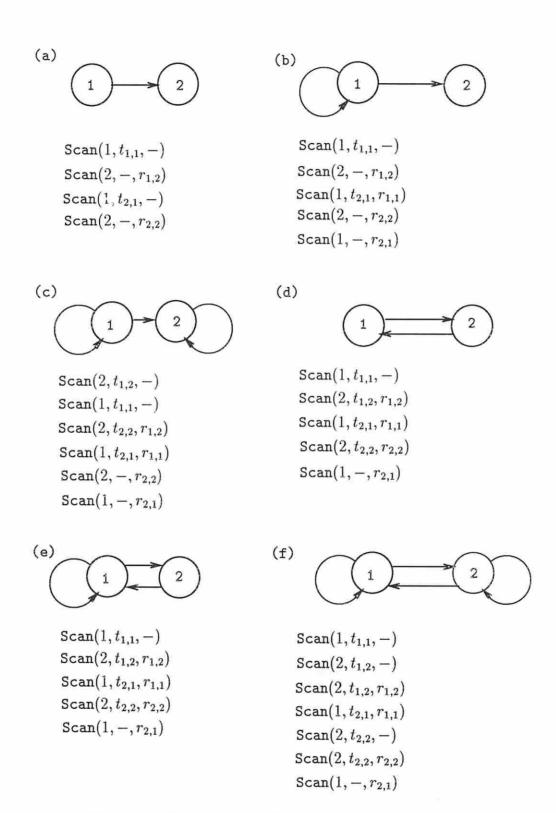

In this section, the design of BIT controllers for various test structures are presented. These controllers use the state of the TAP controller as a source of the control signals. When testing a kernel, the state transitions of the BIT controller must follows the control graph of the kernel. A control graph that can be used to test a LSSD kernel [21] is shown in Figure 2.8(b).

In a control graph, a node Si represents a control state of a BIT controller, which is associated with a signal FSi (not shown in the graph) that is active in

this state; an arc represents a state transition; and the label of an arc represents the number of iterations associated with that transition. A rectangle decision box determines the state transitions. The arc with label 1 in the box is taken when this box is first entered. The arc with the next highest number will be taken only when a sufficient number of iterations has been taken in the currently selected arc. For example, in Figure 2.8(b), once state S2 is entered, the second arc (to state S1) is taken after the first arc (self-loop) has been taken s times. Similarly, the third arc (to exit) is taken after the second arc has been taken t times. For those states that have only one possible next state, no decision box is needed. Thus the decision box corresponds to a nested loop of the form

```

do once

do for j=1,...,t

do for i=1,...,s.

```

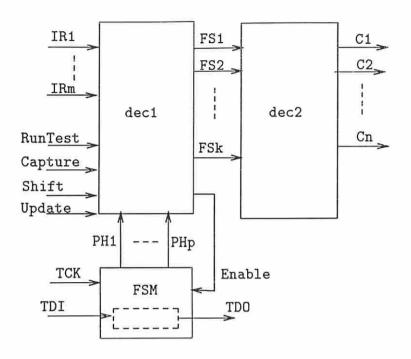

The control signals C1,..., Cn are decoded from the signals FSi, i=1,...,k. Thus the implementation of a bus-dependent BIT controller deals with the activation of the signals FS1,...,FSk, in the sequence as described by the control graph. A general model of the bus-dependent BIT controller is shown in Figure 2.9. The BIT controller consists of two combinational decoders and an optional finite state machine FSM. The decoder dec2, which generates control signals C1,...,Cn from the signals FS1,...,FSk, consists of a set of OR gates. The decoder dec1 generates the signals FS1,...,FSk from three sources, namely the contents of the IR, the TAP controller state signals and the output PH1,...,PHp of the finite state machine FSM. Note that the finite state machine is not needed if the controller can be implemented using a combinational circuit.

The finite state machine is implemented as a programmable counter, which, when enabled, can count from 1 to c ( $c \le p$ ) repeatedly. The signal PHi is active only when the counter value is i, where  $1 \le i \le c$ . Thus the signals on PH1,...,PHc form a one-hot code, and these values are generated repeatedly as long as the FSM is enabled. When the finite state machine is disabled, the value of the counter is 0 and the outputs of the machine are all disabled. The value c is determined by a register in the machine which can be modified by shifting a new value into it.

Figure 2.8: A LSSD kernel; (a) control signals, (b) control graph.

Figure 2.9: A general model for the bus-dependent BIT controller.

Note that this register can be part of the instruction register or an addressable data register.

## 2.2.1 BIT Controller for a LSSD Kernel

If a kernel is made testable using the LSSD technique [21], the BIT structure consists of two registers (R1, R2) and a combinational circuit C (see Figure 2.8(a)). (The registers R1 and R2 can be combined into a single register). These two registers form a scan register that is selected if the contents of the IR is 011 (denoted as [IR=011]). During the test mode, the control signals of the LSSD kernel are LD1, LD2, SH1, SH2. The signals LD1, LD2, which control the parallel loading of new data into registers R1, R2, respectively, are activated while in state S1. The signals SH1, SH2, which control the shifting of data along registers R1 and R2, are activated in state S2. When none of these signals are active, both registers R1 and R2 retain their values, i.e., remain in the HOLD mode. To test the LSSD kernel properly, the control signals should be activated according to the control graph shown in Figure 2.8(b).

To test the LSSD kernel properly, it is necessary to derive the control signals as follows.

```

C1 = LD1 = LD2 = FS1;

C2 = SH1 = SH2 = FS2.

```

From the model described in Figure 2.7, it is clear that a circuit that implements the following functions can be used as a BIT controller.

```

FS1 = Capture * [IR=011];

FS2 = Shift * [IR=011].

```

When such a BIT controller is used, an external controller can test the LSSD kernel by first loading the IR with the proper value (011 in this case) and driving the TAP to the states CaptureDR and ShiftDR, which in turn activate FS1 and FS2 according to the control graph. Therefore, the control signals LD1, LD2, SH1 and SH2 are properly activated and the LSSD kernel is tested. Note that the external controller must have at least two counters to keep track of the values of t and s required in the control graph.

The mapping between the TAP controller states and the test control of the application circuit may not be obvious in some cases. An algorithm that facilitates this mapping properly will be given later in this chapter.

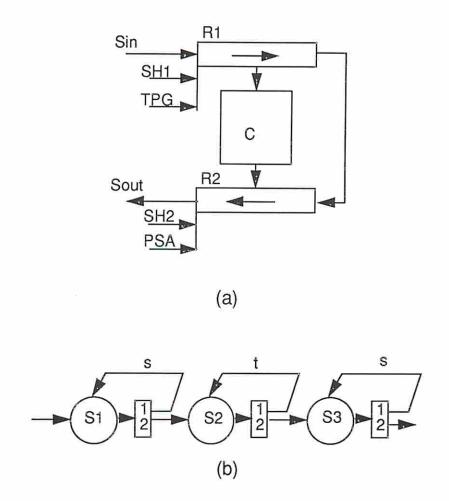

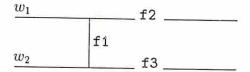

## 2.2.2 BIT Controller for a BILBO Kernel

In the case of a BILBO kernel [38] (see Figure 2.10(a)), the BIT structure consists of two BILBO registers (R1, R2). During the test mode, the control signals of R1 are TPG and SH1, while those of register R2 are PSA and SH2. These two registers form a scan register that can be selected when the value in the instruction register is 101, that is [IR=101]. To test a BILBO kernel properly, the control signals must be activated as illustrated in the control graph in Figure 2.10(b). The signals SH1 and SH2, which control the shift operation in registers R1 and R2, respectively, are both active in states S1 and S3. When the signal TPG is active,

Figure 2.10: A BILBO kernel: (a) control signals, (b) control graph.

register R1 acts as a test pattern generator. When the signal PSA is active, register R2 functions as a parallel signature analyzer. Both TPG and PSA are active in state S2. Note that to correctly execute a test according to the control graph, different instructions must be used in states S1 and S2. One reason for this is that in going from the Reset state to the ShiftIR state in the TAP control, one enters the RunTest state for at least one clock cycle. According to the control graph, it is clear that the decoder dec2 should be implemented as follows.

```

C1 = TPG = PSA = FS2;

C2 = SH1 = SH2 = FS1 + FS3.

```

Using the control model shown in Figure 2.7, it is clear that the decoder dec1 should be implemented as follows.

```

FS2 = RunTest * [IR=011];

FS1 = FS3 = Shift * [IR=101].

```

Note that in the above two examples, the BIT controller is simply a combinational circuit consists of two decoders. This is because the mapping mechanism is simple. If the mapping scheme is very complex, the algorithm presented in section 2.2.4 can be used to construct a BIT controller.

# 2.2.3 BIT Controller for a Complex Kernel

Consider the complex kernel in Figure 2.11(a), where the BIT structure consists of four registers (R1, R2, R3, R4), a combinational circuit C and a bus with its associated controls. During the test mode, the control signals are: LD1, SH1, TPG1, LD2, LD3, LD4, SH4, PSA, G1 and G2. A test vector is generated when the TPG signal is active. The test vector is transferred to the register R2 and then applied to C by activating both signals G1 and LD2. The results are then transferred to register R3 by activating the signal LD3. Finally, the results can be compressed in the register R4 if both the signals G2 and PSA are activated. This process is repeated t times, where t is the number of vectors required to test C.

Figure 2.11: A complex kernel; (a) control signals, (b) control graph.

To reduce the test time, a new test vector can be applied before the completion of the previous vector. However, resource conflicts must be avoided. For example, to avoid any conflict on the bus, the signals G1 and G2 cannot be activated in the same clock phase.

A minimal time test schedule for this kernel is shown in Table 2.1, where nine steps are required to apply four vectors (v1, v2, v3, v4). Each table entry represents a set of control signals that should be active at each time step for applying a test vector.

| time | v1      | v2      | v3      | v4      |

|------|---------|---------|---------|---------|

| 1    | TPG     |         |         |         |

| 2    | LD2, G1 | TPG     |         |         |

| 3    | LD3     | LD2, G1 |         |         |

| 4    | PSA, G2 | LD3     |         |         |

| 5    |         | PSA, G2 | TPG     |         |

| 6    |         |         | LD2, G1 | TPG     |

| 7    |         |         | LD3     | LD2, G1 |

| 8    |         |         | PSA, G2 | LD3     |

| 9    |         |         |         | PSA, G2 |

Table 2.1: Test schedule for the complex kernel.

From the table, one can conclude that the activation of control signals can be classified into four phases. In the first phase, the activated control signals are TPG, G2 and PSA. In the second phase, the activated signals are TPG, LD2 and G1. In the third phase, the activated signals are LD2, G1 and LD3. In the fourth phase, the activated signals are LD3, G2 and PSA. Two vectors are applied for each iteration of these four phases. The control graph that can be used to execute the test schedule is shown in Figure 2.11(b). The BIT controller that implements this control graph can be either a sequential or a combinational circuit. These two approaches are described next.

#### Sequential approach

In this approach, the finite state machine FSM is used to derive the required control signals. The control signals FS1 and FS6 are active when the instruction is

IR=[0010] and the bus signal Shift is active. The control signals FS2, FS3, FS4, FS5 are derived from the signals PH1, PH2, PH3, PH4, respectively. The finite state machine is programmed as a counter that repeatedly counts from 1 to 4, thus activating PH1, PH2, PH3 and PH4 in sequence when the instruction is IR=[0111] and the bus state is RunTest. The counting continues until the signal PH4 has been activated t/2 times. This means that the test bus must stay in the RunTest state for exactly 2t clock cycles. The decoder dec1 is implemented as follows:

```

FS1 = FS6 = Shift * [IR=0010];

FS2 = PH1;

FS3 = PH2;

FS4 = PH3;

FS5 = PH4;

```

The decoder dec2 is implemented as follows:

```

SH1 = SH4 = FS1 + FS6;

TPG = FS2 + FS3;

PSA = G2 = FS2 + FS5;

LD2 = G1 = FS3 + FS4;

LD3 = FS4 + FS5;

```

An external test controller can thus execute the test by driving the bus states according to the control graph. Note that counters are required for the external controller to keep track of the values of s and t. In this example, the required finite state machine is a simple sequencer, which upon activation, repeats a sequence of steps which equals the number of phases in the control graph.

### Combinational Approach

In this case, the BIT controller is implemented using combinational circuits and the FSM part is not used. Each control signal must be generated by using a separate instruction. For example, the control signals FS2, FS3, FS4 and FS5 can be generated using the instructions IR=[0101], [0110], [0111] and [1000], respectively. In this case, the decoder dec1 is implemented as follows.

```

FS1 = FS6 = Shift * [IR=0010];

FS2 = RunTest * [IR = 0101];

FS3 = RunTest * [IR = 0110];

FS4 = RunTest * [IR = 0111];

FS5 = RunTest * [IR = 1000].

```

The decoder dec2 is the same for both the sequential and combinational approaches.

An external controller can thus execute the test by driving the bus state according to the control graph. Again, counters are required for the external controller to keep track of the values of s and t. Note that a new instruction is required for the activation of each new control signal. Therefore, the test execution time is increased dramatically compared to the sequential approach.

From these two approaches, one can conclude that there is a relation between the test time and the complexity of the BIT controller. In general, the more complex the BIT controller is, the shorter the test time.

# 2.2.4 A Mapping Algorithm

When designing a BIT controller for a single kernel, as shown in the above examples, a mapping algorithm is required to ensure the correctness of the BIT controller. During the test mode, the signals C1, C2,..., Cn should be controlled by the BIT controller so that the kernel can be properly tested. The test procedure for the kernel is described in a control graph, which has been previously defined. Each state (or node) of the control graph is associated with a set of control signals, which are the signals that are active in that state. The inputs to the BIT controller is the contents of the IR and the signals directly derived from the bus state, namely Capture, Shift, Update and RunTest (see Figure 2.7). The BIT controller outputs the signals C1, C2,..., Cn.

The input of this algorithm is a control graph, where each state is associated with a set of control signals that should be active in that state. The output of this algorithm is a set of boolean functions along with a set of instructions for the TAP.

All control signals are represented in terms of the bus signals Capture, Shift, Update, RunTest, the contents of the IR, and possibly the output of the FSM. A state signal (FSi) is associated with the state Si. The state signals are used as the intermediate form for generating the control signals C1, C2,..., Cn. Once the state signals are generated, all control signals Ci associated with that state are active when FSi is active. If a control signal Ci is associated with various states (Si, Sj, Sk) then Ci = FSi + FSj + FSk.

The mapping algorithm is used for the design of a bus-dependent BIT controller. Therefore, it is assumed that one of the four bus state signals, namely RunTest, Shift, Update, Capture, must be used to derive any control signal.

### The Mapping Algorithm:

Input: A control graph and a list of control signals associated with each state.

Output: Ci in terms of FSj's, which is a function of the IR contents, the bus state signals and (optionally) the output of the FSM.

- 1. Repeat this step for all shifting states.

- 1.1. Assign a distinct instruction to each scan chain.

- 1.2. For each state Si, FSi=Shift\*[IR=assigned instruction],

and mark this state.

- 2. Repeat this step for all unmarked self-loop states.

- 2.1. Assign a distinct instruction to each self-loop state.

- 2.2. For each state Si, FSi=RunTest\*[IR=assigned instruction], and mark this state.

- 3. If the only next state of an unmarked state (Si) is a shifting state, let FSi=Capture\*[IR=instruction of the shifting state], and mark this state.

- 4. If the only previous state of an unmarked state (Si) is a shifting state, let FSi = Update \* [IR=instruction of the shifting state], and mark this state.

- 5. If all neighboring states of an unmarked state (Si) have been marked, let FSi=RunTest\*[IR=instruction of one of its next states] and mark this state.

- 6. Do this step for all unmarked states.

- 6.1. Partition these unmarked states into groups such that for an unmarked state Si in group j, if the next or previous states of Si are also unmarked then they are also in group j, i.e., no neighboring state of a state in group j is unmarked.

Do step 6.2 for each group.

- 6.2. If the group contains more than one state, go to step 6.3, else assign a new instruction to this state Si, and let FSi=RunTest\*[IR=assigned instruction]. Mark this state.

- 6.3. Sequential Approach: Assign a new instruction to this group.

Let the number of states in this group be c. Program the FSM such that it counts from 1 to c when Enable = RunTest\*[IR=the selected instruction] is active. Assign the FSM state signals PH1,...,PHc to the appropriate FSi's so that all FSi's in this group are properly activated. Mark all states in this group.

- 7. Instruction merging:

The control graph can be reduced to a subgraph for a given set of nodes if all other nodes and their associated arcs are removed. Generate a subgraph for each group of nodes formed in step 6. For all subgraphs that are isomorphic and are associated with the same control signals, an instruction can be used for all these groups. The number of assigned instructions can thus be reduced.

Generate all control signals Ci from the FSj's. If a signal is active in several states, say Si, Sj and Sk, then Ci=FSi+FSj+FSk.

Initially, all states of the control graph are unmarked. After the execution of this algorithm, all states are marked and their associated signals are assigned with a boolean function. Since data must be sent and received when shifting a register in the application circuit, the shifting states in the control graph can only be mapped into the bus state ShiftDR. In step 2, a self-loop state is mapped into the RunTest bus state since this state can be held for many consecutive times without changing the contents of IR. In step 3, 4 and 5, more intermediate signals

are generated without assigning any extra instruction. In step 6, the state signals for all the unmarked states are generated by using RunTest. The BIT controller can either be a combinational circuit or a sequential circuit. If step 6.3 is entered, a sequencer is created, the BIT controller is a sequential circuit; otherwise it is a combinational circuit. After step 6, all the states have been marked (or processed). Instructions that can be shared among different groups formed in step 6 are found in step 7. The total number of instructions assigned is then further reduced. In step 8 all control signals (Ci) are generated from the intermediate state signals (FSi). The correctness of the BIT controller is guaranteed since all control signals Ci are controlled by the contents of IR and the bus states.

Example The Mapping Algorithm is illustrated using the complex kernel shown in Figure 2.11(b). The associated control graph is shown in Figure 2.11(b).

- 1.1. Assign instruction i1 to the only scan register in this example.

- 1.2. There are two shift states S1 and S6, therefore, FS1=FS6=Shift\*[IR=i1]. Mark states S1 and S6.

- 2. This step is skipped since there are no unmarked self-loop nodes.

- 3. Skipped.

- 4. Skipped.

- 5. Skipped.

- 6.1. Only one group consisting of states S2, S3, S4 and S5 is formed.

- **6.2**. Skipped.

- 6.3. (Use Sequential approach) Assign instruction i2 to this group. The FSM is enabled when Enable = RunTest\*[IR=i2] is active. The FSM is programmed to keep counting from 1 to 4 when enabled. Let FS2=PH1, FS3=PH2, FS4=PH3, FS5=PH4.

- 7. No instruction merging can be done. Two instructions are assigned.

- 8. Assign all control signals. TPG = FS2 + FS3, PSA = FS2 + FS5, G2 = FS2 + FS5, LD2 = FS3 + FS4, G1 = FS3 + FS4, LD3 = FS4 + FS5, SH1 = FS1 + FS6, SH4 = FS1 + FS6.

Let the number of scan chains formed by shift registers be  $I_c$ , the number of self-loop states be  $I_s$ , and the number of groups formed in step 6 be  $I_g$ . The total number of instructions assigned in this algorithm is  $I_{seq} = I_c + I_s + I_g$ . Note that the public instructions defined in the standard are not included here.

Lemma 1 The number of instructions assigned by the mapping algorithm is minimal.

#### Proof:

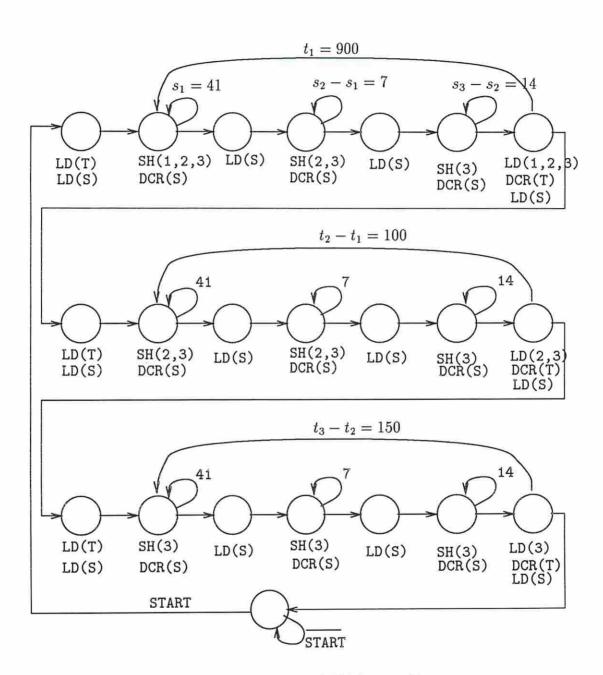

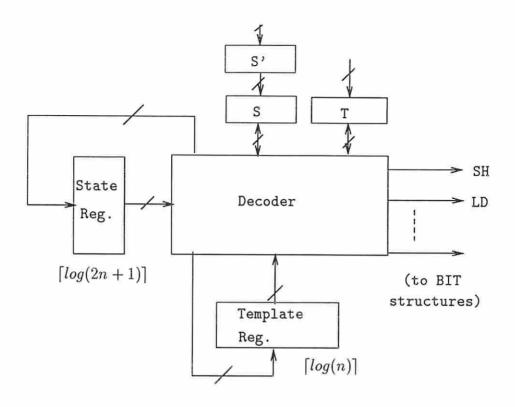

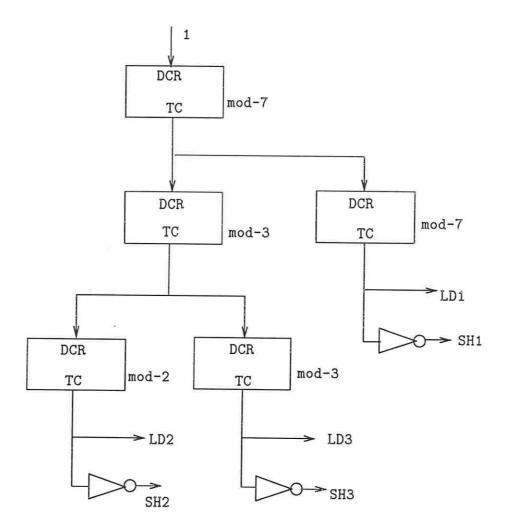

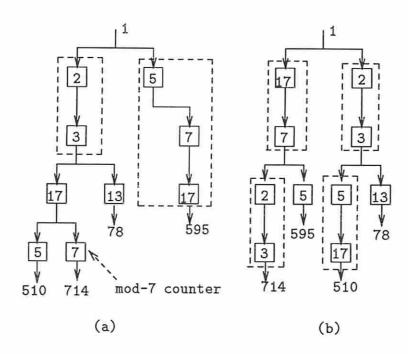

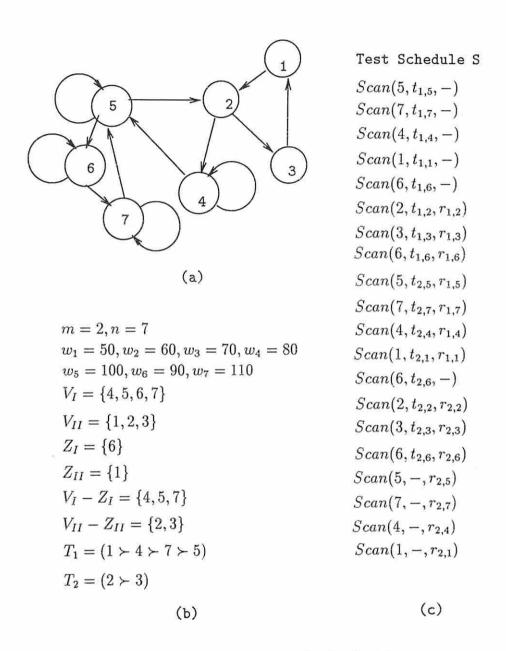

The number of instructions is the sum of  $I_c$ ,  $I_s$ , and  $I_g$ . The first two numbers are defined by the structure of the control graph. The third number  $I_g$  is minimal since the number of groups derived from step 6.1 is minimal. Thus it is clear that the number of instructions  $(I_{seq})$  assigned by the mapping algorithm is minimal.