# Multi-level Logic Synthesis Based on Function Decomposition

Kuo-Rueih Ricky Pan

CENG-96-12

Department of Electrical Engineering - Systems University of Southern Los Angeles, California 90089-2562 (213)740-4458

May 1996

## Multi-level Logic Synthesis Based on Function Decomposition

by

Kuo-Rueih Ricky Pan

A Dissertation Presented to the FACULTY OF THE GRADUATE SCHOOL UNIVERSITY OF SOUTHERN CALIFORNIA

In Partial Fulfillment of the

Requirements for the Degree

DOCTOR OF PHILOSOPHY

(Electrical Engineering)

May 1996

Copyright 1996 Kuo-Rueih Ricky Pan

# To my parents Chao-Ming Charles Pan and Pi-Lee Alice Chen

### Acknowledgments

I am indebted to my advisor Dr. Massoud Pedram for his continuous support, constant encouragement, and guidance. Without his help, this research would have not been possible. I would also like to thank Profs. Viktor K. Prasanna and Doug Ierardi for being on my dissertation and guidance committees, and Profs. Peter A. Beerel and Sandeep Gupta for being on my guidance committee.

I would like to express my thanks to my friend Yung-Te Lai for many fruitful discussions. I have also had the good fortune of meeting many wonderful people at USC. In particular, I would like to thank Chen-Huan Chiang, Chihshun Ding, Cheng-Ta Hsieh, Sasan Iman, Diana Marculescu, Radu Marculescu, Chun-Li Pu and Wei-Li Wang.

The funding for my research was provided by National Science Foundation under contract No. MIP-9111206 and MIP-9211668. I gratefully acknowledge that.

I am grateful to my father and mother who encouraged me to pursue academics.

## Contents

| Li | st Of | Table  | es v                                | ii |

|----|-------|--------|-------------------------------------|----|

| Li | st Of | Figur  | res vi                              | ii |

| 1  | Intr  | oducti | ion                                 | 1  |

|    | 1.1   | CAD    | Systems                             | 1  |

|    | 1.2   | Logic  | Synthesis                           | 2  |

|    | ,9    | 1.2.1  | Logic Restructuring                 | 2  |

|    |       | 1.2.2  | Technology Mapping                  | 4  |

|    | 1.3   | Overv  | iew                                 | 5  |

| 2  | Bac   | kgroui | ad                                  | 6  |

|    | 2.1   | Functi | ion Decomposition                   | 6  |

|    | 2.2   | Order  | ed Binary Decision Diagrams (OBDDs) | 9  |

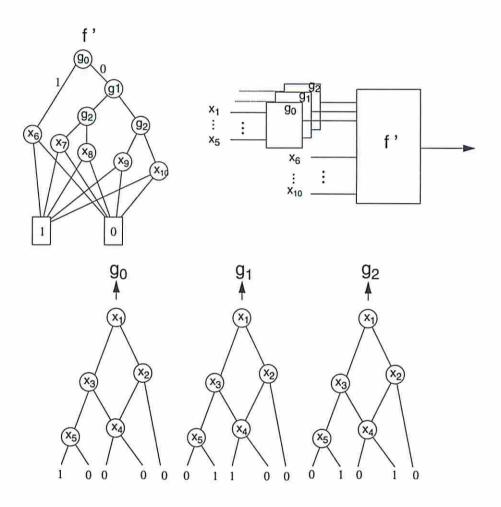

|    | 2.3   | OBDI   | O-based Function Decomposition      | 1  |

|    |       | 2.3.1  | Disjunctive Decomposition           | 14 |

|    |       | 2.3.2  | Nondisjunctive Decomposition        | 15 |

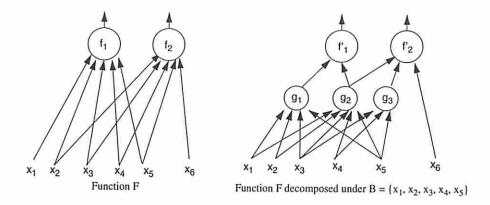

| 3  | Con   | nmon   | Subfunction Extraction 1            | 9  |

|    | 3.1   | Colum  | nn Encoding                         | 19 |

|    |       | 3.1.1  | Output Grouping                     | 26 |

|    | 3.2   | Uni-co | ode Shared Subfunction Encoding     | 28 |

|    |       | 3.2.1  | Permissible G-functions             | 30 |

|   |     | 3.2.2    | Minimum Subfunction Covering Problem                                                        | 33 |

|---|-----|----------|---------------------------------------------------------------------------------------------|----|

|   |     | 3.2.3    | Minimum Support for G-functions                                                             | 35 |

|   | 3.3 | Multi-   | code Shared Subfunction Encoding                                                            | 38 |

|   | 3.4 | Comm     | non Subfunction Extraction for Large Bound Sets                                             | 42 |

|   |     | 3.4.1    | Encoding Complexity                                                                         | 42 |

|   |     | 3.4.2    | An Encoding Scheme for Large Compatible Class Size                                          | 44 |

|   |     | 3.4.3    | Graph-based Encoding Using Multi-code Assignments                                           | 52 |

|   |     | 3.4.4    | Extending Graph-Based Shared Subfunction Encoding $\ \ldots$                                | 55 |

|   |     | 3.4.5    | Output Partitioning for Graph-based Encoding                                                | 56 |

|   | 3.5 | Summ     | ary                                                                                         | 59 |

| 4 | Oth | er Obj   | jective Functions                                                                           | 60 |

|   | 4.1 | Decom    | position for Minimum Delay                                                                  | 60 |

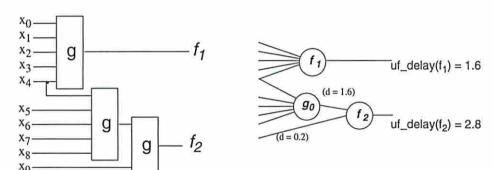

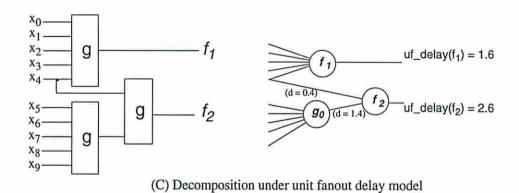

|   |     | 4.1.1    | $\label{thm:minimum_delay} \mbox{Minimum Delay Decomposition Using Unit Delay Model}  .  .$ | 60 |

|   |     | 4.1.2    | Minimum Delay Decomposition Using Unit Fanout Delay                                         |    |

|   |     |          | $\operatorname{Model} \ \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$     | 67 |

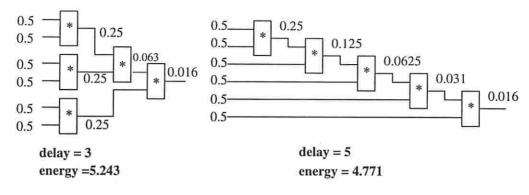

|   | 4.2 | Decom    | nposition for Minimum Energy Dissipation                                                    | 73 |

|   |     | 4.2.1    | Energy Consumption Model                                                                    | 73 |

|   |     | 4.2.2    | Energy Consumption and Function Decomposition                                               | 74 |

|   |     | 4.2.3    | Minimum Energy Decomposition                                                                | 77 |

|   | 4.3 | Energ    | y-Delay Optimum Decomposition                                                               | 81 |

|   | 4.4 | Decon    | aposition into Special Classes of Functions                                                 | 84 |

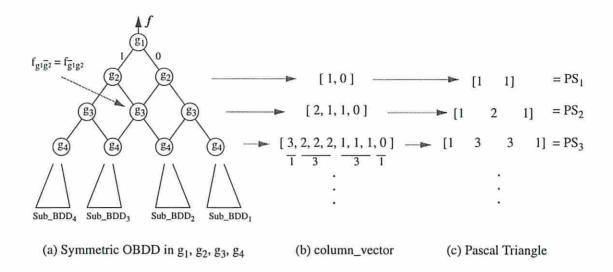

|   |     | 4.4.1    | Decomposition and Symmetric Functions                                                       | 84 |

|   |     | 4.4.2    | Decomposition and Unate Functions                                                           | 88 |

|   | 4.5 | Summ     | ary                                                                                         | 89 |

| 5 | App | olicatio | on to LUT-Based FPGA Synthesis                                                              | 90 |

|   | 5.1 | Field    | Programmable Gate Arrays                                                                    | 90 |

|   | 5.2 | Overv    | iew of FGSvn                                                                                | 92 |

|    |     | 5.2.1  | Node Clustering                           | . 9  | 3 |

|----|-----|--------|-------------------------------------------|------|---|

|    |     | 5.2.2  | Generating the Subject Network            | . 9  | 5 |

|    | 5.3 | Mappi  | ng for XC3000 Device                      | . 9  | 7 |

|    |     | 5.3.1  | Look-up Table Merge                       | . 9  | 8 |

|    | 5.4 | Mappi  | ng for XC4000 Device                      | . 9  | 8 |

|    |     | 5.4.1  | Direct Decomposition                      | . 9  | 9 |

|    |     | 5.4.2  | Two-Layer Decomposition                   | . 10 | 2 |

|    | 5.5 | Mappi  | ng for XC5000 Device                      | . 10 | 7 |

|    |     | 5.5.1  | Mapping Using Fixed Input Size LUTs       | . 10 | 7 |

|    |     | 5.5.2  | Mapping Using Variable Input Size LUTs    | . 10 | 8 |

|    | 5.6 | Summ   | ary                                       | . 10 | 9 |

| 6  | Exp | erimei | ntal Results                              | 11   | 0 |

|    | 6.1 | Descri | ption of Benchmarks                       | . 11 | 0 |

|    | 6.2 | OBDE   | D-based Function Decomposition            | . 11 | 2 |

|    | 6.3 | Other  | Objective Functions Decomposition         | . 11 | 8 |

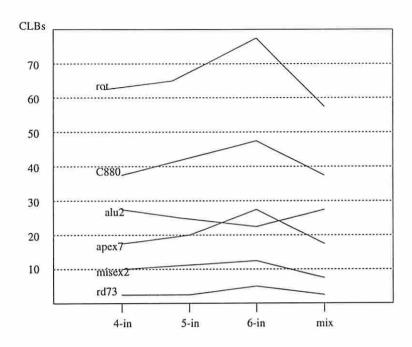

|    | 6.4 | Decom  | aposition for Other Architectures of FPGA | . 12 | 4 |

| 7  | Con | clusio | n and Future Work                         | 13   | 0 |

| Aı | pen | dix A  |                                           |      |   |

|    | FCS | Syn    |                                           | 13   | 2 |

## List Of Tables

| 3.1  | $pg$ -set size versus column_set size $k$                                    |

|------|------------------------------------------------------------------------------|

| 6.1  | Description of benchmark circuits                                            |

| 6.2  | Comparison between cube-based and OBDD-based decompositions . $112$          |

| 6.3  | Experimental results of FGSyn for XC3000 device                              |

| 6.4  | Runtime Comparison of FGSyn for XC3000 device                                |

| 6.5  | Large size benchmarks results for XC3000 device                              |

| 6.6  | Experimental results for XC3000 device                                       |

| 6.7  | Experimental results of FGSyn_d                                              |

| 6.8  | Delay minimum decomposition (unit delay vs. unit fanout delay                |

|      | model)                                                                       |

| 6.9  | Energy comparison between mis-pga(new) and FGSyn_e $\ \ldots \ \ldots \ 120$ |

| 6.10 | Energy-delay product comparison between mis-pga(new) and FGSyn_ed121         |

| 6.11 | Comparison of FGSyn_e and FGSyn_ed                                           |

| 6.12 | Comparison of FGSyn, FGSyn_d, and FGSyn_e                                    |

| 6.13 | Experimental results of FGSyn options for XC4000 device $\ \ldots \ 125$     |

| 6.14 | Experimental results for XC4000 device                                       |

| 6.15 | Experimental results of various bound sets for XC5000 127                    |

| 6.16 | Energy comparison of various bound sets decomposition for XC5000. $128$      |

## List Of Figures

| 2.1  | Function decomposition                                              | 7  |

|------|---------------------------------------------------------------------|----|

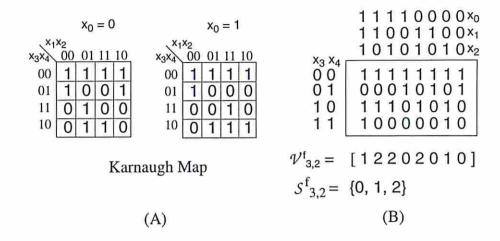

| 2.2  | The Karnaugh map and the decomposition chart                        | 8  |

| 2.3  | Function decomposition                                              | ç  |

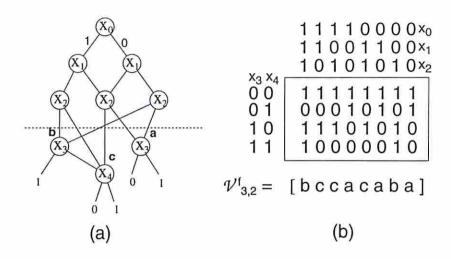

| 2.4  | A function represented in (a) OBDD and (b) decomposition chart      | 12 |

| 2.5  | An example for operator $cut\_vector$ and $cut\_set.$               | 14 |

| 2.6  | OBDD function decompositions, $B = \{x1, x2, x3, x4, x5\}$          | 16 |

| 2.7  | An example of non-disjunctive decomposition                         | 18 |

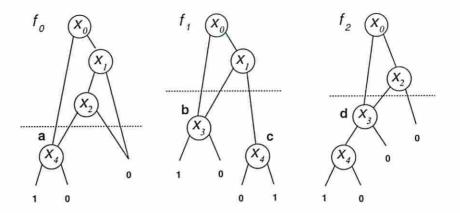

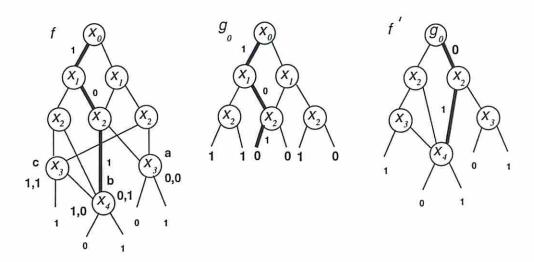

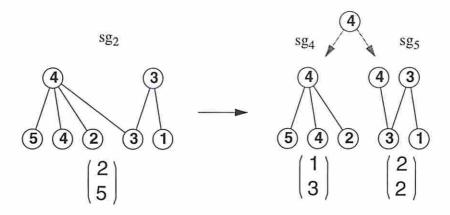

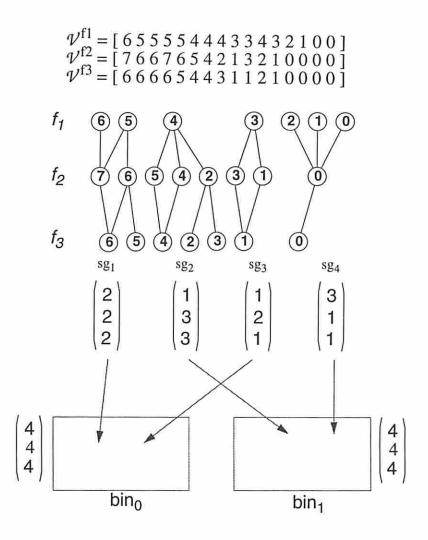

| 3.1  | An example of multiple-output decomposition                         | 21 |

| 3.2  | An example of multiple-output decomposition in OBDD representation. | 25 |

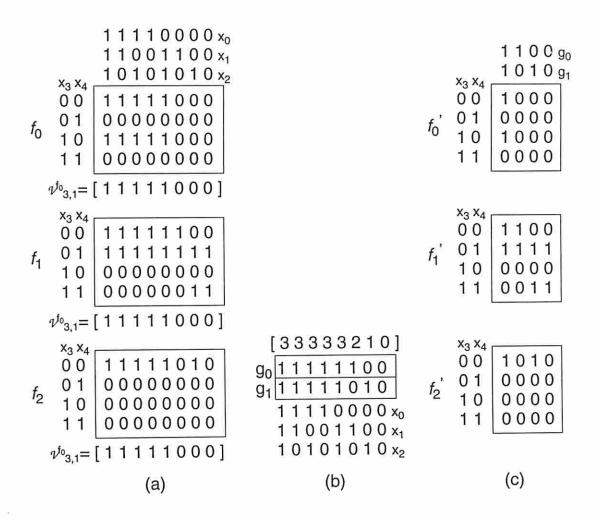

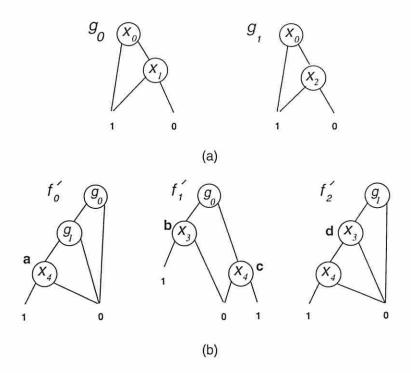

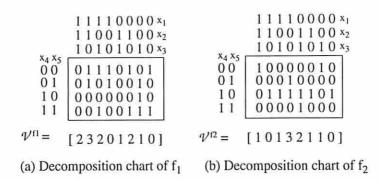

| 3.3  | Decomposition charts of $f_1$ and $f_2$                             | 30 |

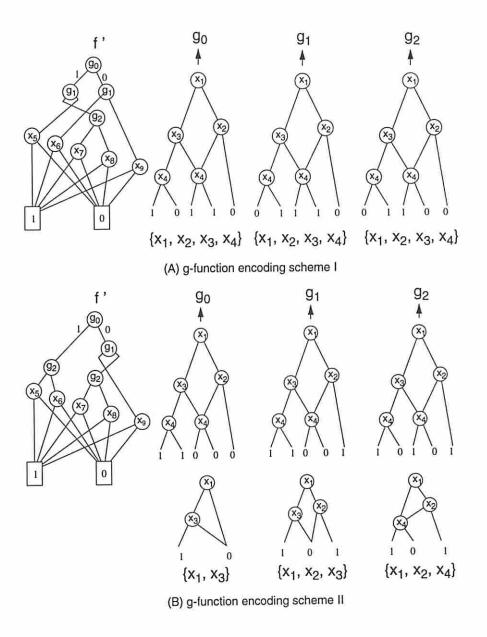

| 3.4  | Resulting g-functions of two encodings                              | 37 |

| 3.5  | (Code) dependency graph                                             | 45 |

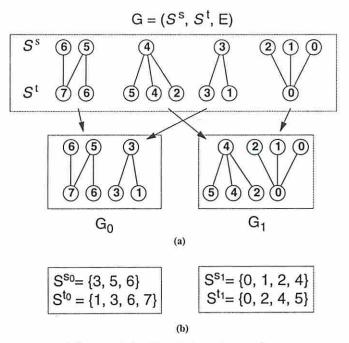

| 3.6  | Partitioned graph                                                   | 47 |

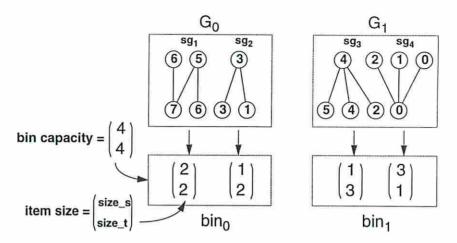

| 3.7  | Conversion to bin packing problem                                   | 48 |

| 3.8  | Dependency graph with large subgraph                                | 53 |

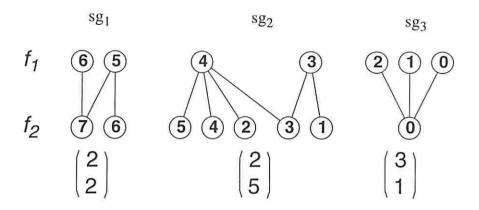

| 3.9  | Divisible item (multi-code assignment)                              | 54 |

| 3.10 | A connected acyclic bipartite graph                                 | 55 |

| 3.11 | N-dimensional bin packing problem (N = 3) $\dots \dots \dots$       | 57 |

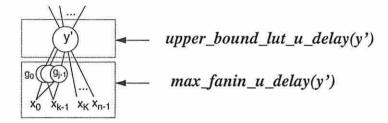

| 4.1  | Upper and lower bound delay estimation                              | 61 |

| 4.2  | Delay estimation                                                    | 63 |

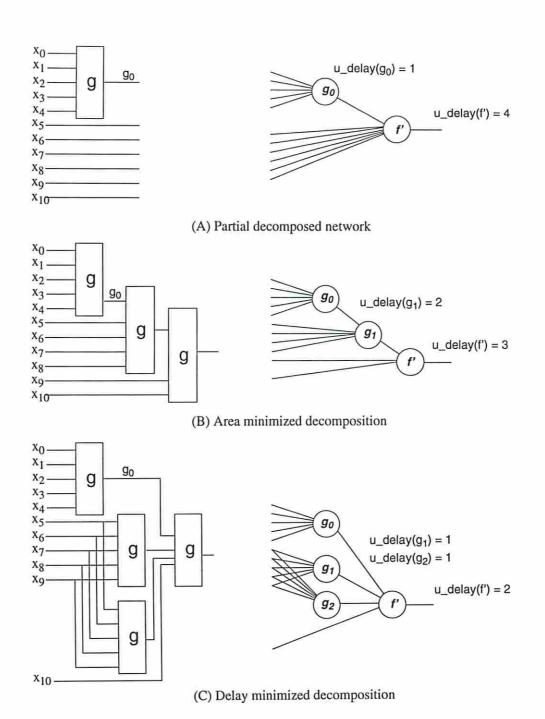

| 4.3  | Delay minimization decomposition                                  |

|------|-------------------------------------------------------------------|

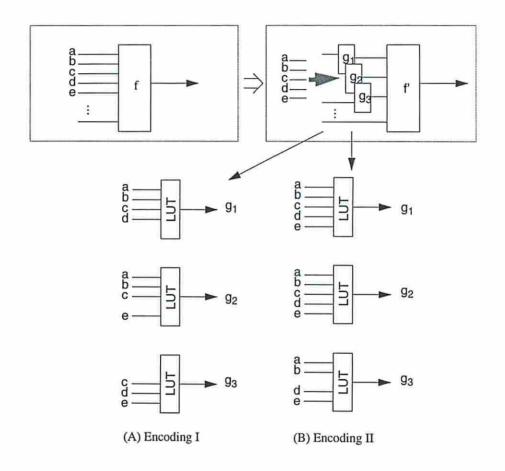

| 4.4  | Encoding effects node fanout                                      |

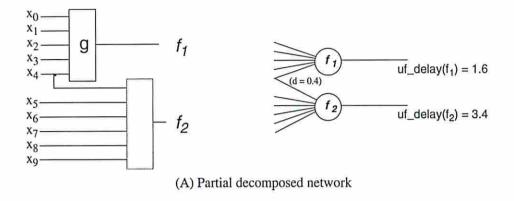

| 4.5  | Delay minimization under unit fanout delay models                 |

| 4.6  | OBDD function decompositions with different encoding 76           |

| 4.7  | Example of multiple-output function decomposition 81              |

| 4.8  | Delay minimum vs. energy minimum decompositions 83                |

| 4.9  | Symmetric property in OBDD 86                                     |

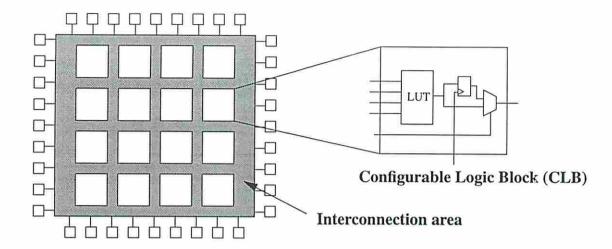

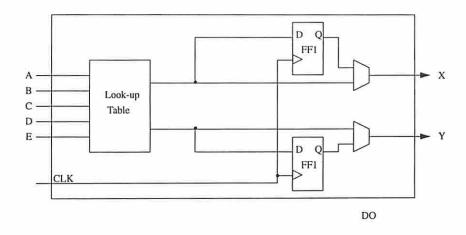

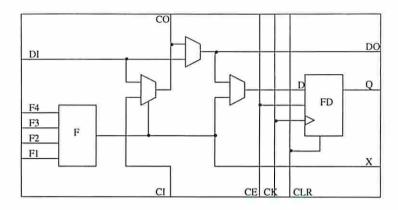

| 5.1  | The FPGA structure                                                |

| 5.2  | The LUT structure                                                 |

| 5.3  | The Xilinx XC3000 CLB                                             |

| 5.4  | The Xilinx XC4000 CLB 98                                          |

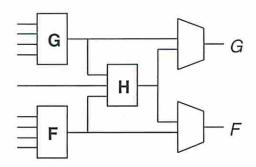

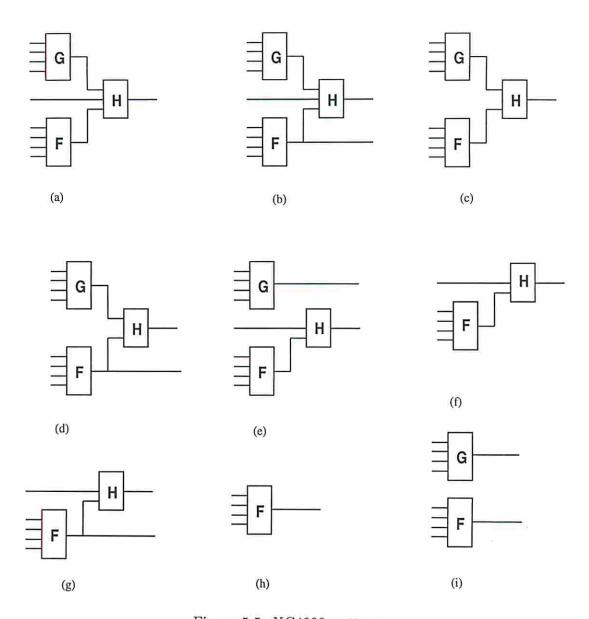

| 5.5  | XC4000 patterns                                                   |

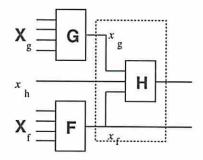

| 5.6  | the non-disjunctive decomposition view of pattern (b) 100         |

| 5.7  | Non-disjunctive mapping for the XC4000 device                     |

| 5.8  | Graphical representation of type I two-layer decomposition 103    |

| 5.9  | The proof of type I two-layer decomposition                       |

| 5.10 | Graphical representation of type II two-layer decomposition $104$ |

| 5.11 | Conditions for type II two-layer decomposition                    |

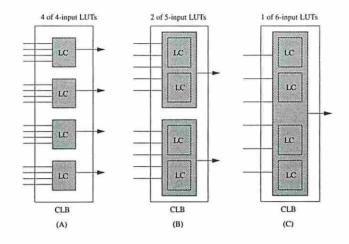

| 5.12 | The Xilinx XC5000 logic cell                                      |

| 5.13 | The different configurations of XC5000 CLB 109                    |

| 6.1  | Selected benchmarks CLBs count for fix and variable bound set     |

|      | decomposition                                                     |

#### Abstract

With the growing complexity of VLSI circuits, automatic synthesis of digital circuits has gained increasing importance. The synthesis process transforms an abstract representation of a circuit into an implementation in a target technology optimizing some objective function. One of the key steps in this process is logic synthesis, which produces an optimal gate level design from a register-transfer level description.

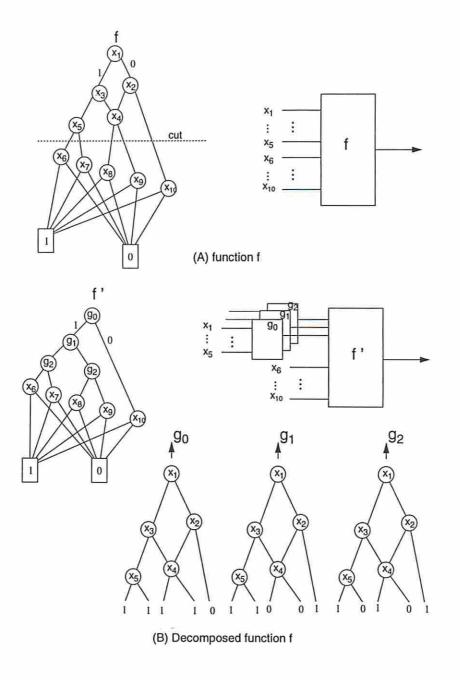

In this thesis, we describe a multi-level logic synthesis approach based on function decomposition. In particular, we present Boolean methods for extracting common subfunctions from multiple-output Boolean functions under different objectives including area, delay, energy, and energy-delay product. The extraction problem is cast as an encoding problem and a number of encoding methods are proposed. These methods include column encoding, shared subfunction encoding, and a graph-based approach for extracting logic with a large number of supporting variables. We use ordered binary decision diagrams to represent Boolean functions so that this approach can be implemented more efficiently.

Application of these methods to the synthesis of look-up table (LUT)-based field programmable gate arrays (FPGAs) is presented next. In many instances, we had to adapt the proposed extraction techniques to the FPGA architecture. For example, we used a two-layer decomposition technique to map to Xilinx XC4000 device and used variable input-size decomposition to map to Xilinx XC5000 device. These techniques produce results which are much better than state-of-the-art techniques in terms of area, delay, and power.

## Optimal Clock Period FPGA Technology Mapping for Sequential Circuits\*

Peichen Pan

Dept. of Electrical & Computer Eng.

Clarkson University

Potsdam, NY 13699

C. L. Liu

Dept. of Computer Science

University of Illinois at Urbana-Champaign

Urbana, IL 61801

Abstract - In this paper, we study the technology mapping problem for sequential circuits for LUTbased FPGAs. Existing approaches map the combinational logic between flip-flops (FFs) while assuming the positions of the FFs are fixed. We study in this paper a new approach to the problem, in which retiming is integrated into the technology mapping process. We present a polynomial time technology mapping algorithm that can produce a mapping solution with the minimum clock period while assuming FFs can be arbitrarily repositioned by retiming. The algorithm has been implemented. Experimental results on benchmark circuits clearly demonstrate the advantage of our approach. For many benchmark circuits, our algorithm produced mapping solutions with clock periods not attainable by a mapping algorithm based on existing approaches, even when it employs an optimal delay mapping algorithm for combinational circuits.

#### 1 Introduction

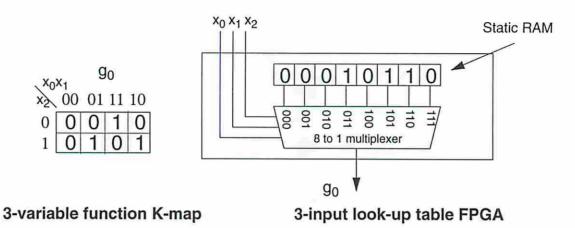

A look-up table (LUT) based FPGA consists of an array of programmable logic blocks together with programmable interconnections [17]. The core of a programmable logic block is a k-input LUT (k-LUT) which can implement any combinational logic with up to k inputs and a single output, where k is a small positive integer. There are also several flip-flops (FFs) in each programmable logic block which can be connected to the inputs and outputs of its LUT to realize sequential behavior.

The technology mapping problem for LUT-based FPGAs is to produce, for a given circuit, an equivalent circuit comprised of LUTs. This problem has been studied extensively. However, almost all proposed mapping algorithms are designed for combinational circuits. Mapping algorithms for combinational circuits (will be referred to as combinational mapping algorithms from now on) have been proposed for different optimization criteria: performance [2, 6, 9, 18], area

\*The work was partially supported by the National Science Foundation under grant MIP-9222408.

33rd Design Automation Conference®

Permission to make digital/hard copy of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for

profit or commercial advantage, the copyright notice, the title of the publication and

its date appear, and notice is given that copying is by permission of ACM, Inc. To

copy otherwise, to republish, to post on servers or to redistribute to lists, requires

prior specific permission and/or a fee.

DAC 96 - 06/96 Las Vegas, NV, USA

©1996 ACM 0-89791-779-0/96/0006..\$3.50

[4, 5, 7, 11, 16], routability [1, 14], and combinations of these [3, 13]. In particular, Cong and Ding [2] proposed an optimal delay combinational mapping algorithm for the unit delay model and Yang and Wong [18] proposed an optimal combinational mapping algorithm for the general delay model.

Existing approaches to technology mapping for sequential circuits use combinational mapping algorithms to map the combinational logic between FFs. These approaches have two obvious shortcomings: (i) failing to consider signal dependencies across FF boundaries, and (ii) not considering the possibility of exposing the combinational logic between FFs in different ways. Note that FFs in a sequential circuit can be repositioned by a technique called retiming [8]. Two recent sequential circuit technology mapping methods [10, 15] also assume the initial positions of the FFs are fixed, though retiming is used as a post-processing step in [15].

In this paper, we study a new approach to sequential circuit technology mapping, proposed in [12]. In this approach the FF positions are assumed to be fully dynamic in the sense that they can be arbitrarily repositioned by retiming. Our main objective is to obtain mapping solutions with minimized clock period, which is the maximum number of LUTs between any two successive FFs. We will present an efficient (polynomial time) algorithm that produces a minimum clock period mapping solution for any sequential circuit<sup>1</sup>.

#### 2 The new approach

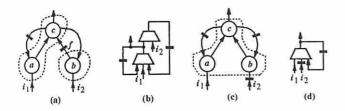

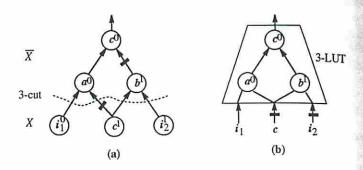

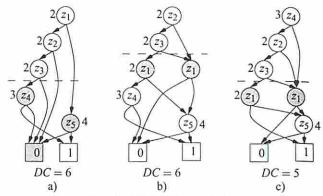

To further motivate the new approach, let us examine two examples. Consider the circuit in Figure 1(a). Suppose that we want to map it to an FPGA architecture in which each LUT has at most 3 inputs. One possible mapping solution, without repositioning the FFs, is shown in Figure 1(a), where the gates enclosed by a dashed circle are mapped to one LUT. Figure 1(b) shows the mapping solution in terms of LUTs. This mapping solution uses two LUTs and has a clock period equal to two. Also note that the clock period of this mapping solution cannot be further reduced by retiming. Actually, it can be shown that any mapping solution must use at least two LUTs and have a clock period two no matter what combinational mapping algorithm is used. However, if gate b is retimed by a value one (the FF f at the output of bis moved to its inputs) as shown in Figure 1(c), all the gates can be mapped to one 3-LUT as shown in Figure 1(d). Note

<sup>&</sup>lt;sup>1</sup>The algorithm has been extended to the general delay model in which case, it produces a mapping solution with a clock period provably close to minimum.

that this mapping solution has a clock period of one.

Figure 1: Advantage of retiming.

To fully exploit the potential of retiming, logic replication is necessary since replication can help produce mapping solutions which are otherwise impossible to obtain. Consider the circuit in Figure 2(a). Assume k=4. It can be shown that any mapping solution must use at least six 4-LUTs and have a clock period at least two, even if retiming is used. However, if we duplicate a (to become a and a'), b (to become b and b'), and c (to become c and c'), then retime the FFs across gates a', b', and c' as shown in Figure 2(b), we can map all the gates (including the duplicated ones) to a single 4-LUT to obtain the mapping solution in Figure 2(c), which has a clock period of one.

Figure 2: Advantage of logic replication.

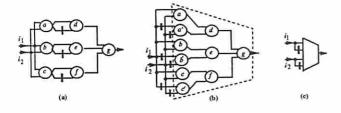

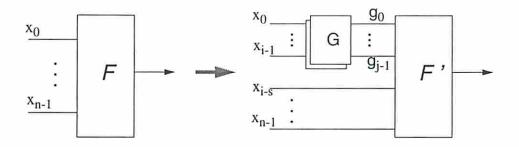

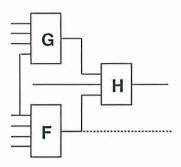

Based on the above observations, we study the technology mapping problem in the most general setting in which the techniques of retiming and replication are exploited. Conceptually, the solution space that will be explored can be described by the diagram in Figure 3. Namely, the mapping solution space consists of all the circuits that can be obtained by retiming and replicating the given initial circuit, then mapping the combinational logic between FFs, followed by another retiming and replication step<sup>2</sup>. It is obvious that the solution space explored in this new approach is enormous since there are too many ways to retime and replicate a circuit.

#### 3 Preliminaries and problem definition

A (synchronous) sequential circuit can be modeled as an edge-weighted directed (multi-)graph. The nodes are the primary inputs (PIs), the primary outputs (POs), and the

Figure 3: Solution space explored in the new approach.

combinational processing elements (PEs) in the circuit. (A PE is either a gate or a LUT depending on whether the circuit is the initial one or a mapping solution.) The edges are the interconnections. There is an edge e from u to v (denoted  $u \stackrel{e}{\rightarrow} v$ ) with weight t if the output of u, after passing through t FFs, is an input to v. The clock period of a circuit is the maximum number of PEs on the combinational paths (paths without FFs) in the circuit.

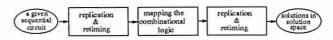

Retiming is a technique of repositioning the FFs in a circuit without changing its functionality or the structure [8]. Retiming a node by a value i means removing i FFs from each fanout edge and adding i FFs to each fanine edge of the node. Figure 4 shows the case in which i=1 or -1. In general, the nodes in a circuit can be retimed collectively (referred to as retiming the circuit). It can be shown that the retimed circuit and the original one have the same functionality if no retiming is performed at the PIs and POs (i.e., the retiming values for the PIs and POs are all zero).

Figure 4: Retiming a node.

Refer again to Figure 3. We use N to denote the circuit to be mapped. We assume that N is k-bounded, namely, each node in N has at most k fanins. We will use w(e) to denote the weight of an edge e in N. Let N' be a circuit obtained from N by replication and retiming and N'' be a mapping solution of the combinational logic of N'. Let S be the circuit obtained from N'' by putting the FFs back and followed by another retiming and replication. (Note that the PEs in N'' are LUTs.) S is then a mapping solution of N. The technology mapping problem addressed in this paper is as follows:

Problem 1 Find a mapping solution with the minimum clock period.

Finally, we list several graph-theoretic concepts. In a directed acyclic graph with one sink but possibly several sources, a  $cut\ (X,\overline{X})$  is a partition of the nodes such that the sink is in  $\overline{X}$  and all the sources are in X. The  $edge-set\ E(X,\overline{X})$  of the cut is the set of edges from X to  $\overline{X}$ , the nodeset  $V(X,\overline{X})$  is the set of nodes in X that are connected to one or more nodes in  $\overline{X}$ . If  $|V(X,\overline{X})| \leq k$ ,  $(X,\overline{X})$  is called a k-feasible cut, or k-cut for short.

#### 4 Formation of LUTs

In this section, we will present a method for forming LUTs for nodes in a sequential circuit.

<sup>&</sup>lt;sup>2</sup>A technology mapping algorithm based on existing approaches may try to alleviate its drawbacks by carrying out these conceptual steps in sequence. However, as long as it actually employs a combinational mapping algorithm, the same drawbacks are still there.

Although the formation of LUTs is rather straightforward for combinational circuits, it is complicated for sequential circuits because a circuit may be arbitrarily retimed and replicated in the new approach. In other words, we are working with a family of circuits. To overcome this difficulty, we introduce the concept of expanded circuits. Our LUT formation procedure will be carried out on the expanded circuits.

An expanded circuit is constructed by replication and it has the property that all paths from any given node to the only output node have the same number of FFs.

The expanded circuits for a node v are defined recursively as follows: As the base case, the circuit with one node  $v^0$  but no edge is an expanded circuit. Suppose  $\mathcal E$  is an expanded circuit. Let I be the set of sources (nodes with indegree 0) in  $\mathcal E$ . We pick a node in I, say  $u^d$ . Then, for each edge  $x \stackrel{e}{\to} u$  in N, add a node  $x^{d_1}$  where  $d_1 = d + w(e)$  to  $\mathcal E$  if it is not there, and add an edge  $x \stackrel{e'}{\to} u^d$  with weight w(e) to  $\mathcal E$ . The resulting circuit is also an expanded circuit.

An important class of expanded circuits consists of:  $\mathcal{E}_v^i$ , for  $i \geq 0$ .  $\mathcal{E}_v^i$  denotes the expanded circuit in which the shortest distance (in terms of the number of edges) from each source that is not a replicate of a PI, to  $v^0$  is i.

For the circuit in Figure 1(a), Figure 5 shows five expanded circuits for node c. From (a) to (e) each expanded circuit is constructed from the preceding one by expanding the shaded node. Actually, the circuit in (a) is  $\mathcal{E}_v^0$ , in (b) is  $\mathcal{E}_v^1$ , in (d) is  $\mathcal{E}_v^2$ , and in (e) is  $\mathcal{E}_v^3$ .

Figure 5: Expanded circuits.

We now show that a LUT for a node can be derived from a cut in the expanded circuits for the node. Let  $(X, \overline{X})$  be a k-cut in an expanded circuit  $\mathcal{E}$  for v. We first notice that all FFs inside  $\overline{X}$  can be moved out by retiming. The retiming is: for each node  $u^d$  in  $\overline{X}$ , its retiming value is d; for all nodes in X, their retiming values are zero. Let  $u^d \stackrel{e'}{\longrightarrow} x$  be an edge in  $E(X, \overline{X})$ . (Note that  $u^d$  is a replicate of node u in N and e' is a replicate of edge e.) It can be verified that the number of FFs on e' is d after the retiming. The LUT derived from this cut is simply the subcircuit induced by the nodes in  $\overline{X}$  with the FFs being removed. Let  $\mathcal{L}$  denote the LUT. If  $u^d$  is in the node-set  $V(X, \overline{X})$  of the cut, it means that u after passing through d FFs is an input to  $\mathcal{L}$ . As a result, the number of inputs to  $\mathcal{L}$  is equal to the number of nodes in  $V(X, \overline{X})$ , which is k. Therefore,  $\mathcal{L}$  is a k-LUT.

As an example, for the 3-cut indicated in the expanded circuit in Figure 5(d) as shown in Figure 6(a), Figure 6(b) shows the corresponding 3-LUT. The inputs to this 3-LUT

are i1, c passing through a FF, and i2 passing through a FF.

Figure 6: Derivation of a LUT from a cut.

Moreover, we can show that for any k-LUT there is a k-cut that can derive the LUT in this fashion, if the expanded circuit is  $\mathcal{E}_v^{kn}$ , where n is the number of nodes in N. Therefore, we have the following main result of this section:

Theorem 1 It suffices to examine the k-LUTs for v that can be derived from the k-cuts in  $\mathcal{E}_v^{kn}$ .

It can be shown the number of nodes in  $\mathcal{E}_v^i$  is O(ni) and the number of edges is O(kni). In particular, the numbers of nodes and edges in  $\mathcal{E}_v^{kn}$  are  $O(kn^2)$  and  $O(k^2n^2)$ , respectively.

# 5 An algorithm for finding an optimal mapping solution

The way we solve Problem 1 is to solve its decision version as stated in the following:

Problem 2 Given a target clock period  $\phi$ , determine a mapping solution with a clock period of  $\phi$  or less, whenever such a mapping solution exists.

If we can solve Problem 2, we can do a binary search on  $\phi$  to find a mapping solution with the minimum clock period.

We describe our algorithm for solving Problem 2 in this section. The algorithm has two phases: the labeling phase and the mapping phase. In the labeling phase, we compute a label (defined later) for each node in N. After we have computed all the labels and determined that there is a mapping solution with a clock period of  $\phi$  or less, we then generate one such mapping solution in the mapping phase. In the next two subsections, we present the details of the two phases, separately.

#### 5.1 The labeling phase

Let S be a mapping solution. We define a value (called l-value) for each LUT in S. To define the l-values, we use a graph whose topology is the same as that of S, and assign a weight  $-\phi \cdot w_1(e) + 1$  to an edge e, where  $w_1(e)$  is the number of FFs on e in S. The l-value of a LUT in S is the maximum weight of the paths from the PIs to the LUT according to the new edge weights.

The label of a node in N is the minimum of the l-values of the k-LUTs for the node, generated according to Theorem 1.

For a node v in N, we will use  $l^{opt}(v)$  to denote its label. We determine  $l^{opt}(v)$  for each node v in N in this phase of the algorithm.

Our method for computing the labels is quite similar to a longest path algorithm. The approach is to compute a lower-bound on the value of each label and to repeatedly improve (increase) the lower-bound. The lower-bounds will be equal to the actual labels when no further improvement is observed for all the lower-bounds. Initially, the lower-bound for all PIs are zero and the lower-bounds for all other nodes are  $-\infty$ . Figure 7 shows the overall algorithm, where l(v) denotes the lower-bound on  $l^{opt}(v)$ . Improving the lower-bounds is carried out by Procedure IMPROVE.

```

L_FIND(N, \phi)

// V denotes the set of nodes in circuit N,

// w(e) denotes the number of FFs on edge e in N

for each node v in V // initialization

1.

if v is a PI

2.

then l(v) \leftarrow 0;

3.

else l(v) \leftarrow -\infty;

4.

updated ← FALSE;

5.

for i \leftarrow 1 to |V| // improve at most n times

6.

for each node v in V

7.

if IMPROVE(v) = TRUE, updated \leftarrow TRUE;

8.

9.

if updated = FALSE, return success;

updated ← FALSE;

10.

return failure;

11.

IMPROVE(v)

Determine lnew;

a.

if l(v) < l_{new}

b.

then

C.

l(v) \leftarrow l_{new};

d.

return TRUE; // improved

e.

```

Figure 7: Algorithm for computing the labels.

return FALSE; // not improved

f.

The purpose of Procedure IMPROVE is to test whether we can improve the current lower-bound on the label of v, based on the current lower-bounds on all labels, and if so, to update the current lower-bound for v.  $l_{new}$  is the new lower-bound for v computed from the current lower-bounds.

Now the remaining issue is to determine  $l_{new}$ . Based on the discussion in Section 3, we have

$$l_{new} = \min_{\left(X, \overline{X}\right)} \left( \max\{l(u) - \phi \cdot d + 1 \mid u^d \text{ is in } V(X, \overline{X})\} \right),$$

where the minimum is taken over all k-cuts in  $\mathcal{E}_{v}^{kn}$ .

We will use the above formula to compute  $l_{new}$ . Our approach is to study the corresponding decision problem, namely,

Problem 3 Check whether  $l_{new} \leq L$  for a given integer L.

We use network flow techniques to solve Problem 3. A flow network G is constructed from  $\mathcal{E}_v^{kn}$  by applying to  $\mathcal{E}_v^{kn}$

a standard network transformation, called node-splitting to reduce the problem of finding a k-cut to that of finding a cut with an edge capacity bound. To do so, each node in  $\mathcal{E}_v^{kn}$  except  $v^0$  is split into two nodes with a bridging edge between them. A supersource is added and connected to all the sources. The bridging edge for node  $u^d$  has capacity one if  $l(u) - \phi \cdot d + 1 \leq L$ . All other edges in G has infinite capacity.

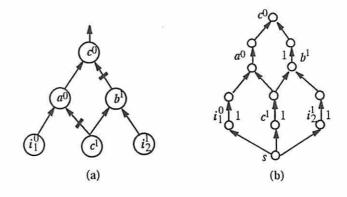

As an example, suppose for the circuit in Figure 1(a), we currently have  $l(i_1) = l(i_2) = 0$ , l(a) = l(b) = 1, and  $l(c) = -\infty$ , and the target clock period is one. In the expanded circuit for c in Figure 8(a), suppose we want to test whether  $l_{new} \leq 1$ . For node  $b^1$ ,  $l(b) - \phi \cdot 1 + 1 = 1$ , so the corresponding bridging edge has capacity one. On the other hand, for node  $a^0$ ,  $l(a) - \phi \cdot 0 + 1 = 2$ , so the corresponding bridging edge has infinite capacity. Figure 8(b) shows the flow network, where the bridging edges for nodes  $i_1^0$ ,  $i_2^1$ ,  $c_1^1$ , and  $b^1$  have unit capacity and all other edges have infinite capacity.

Figure 8: Construction of flow network.

The edge capacity of a cut is the sum of the capacities of the edges in the edge-set of the cut. The following result can be shown for the flow network G:

Lemma 1  $l_{new} \leq L$  iff G has a cut with edge capacity no more than k.

Based on the classical Max-flow Min-cut Theorem, G has a cut with edge capacity no more than k iff the maximum flow in G is at most k. We can, therefore, use an augmenting path algorithm for solving the max-flow problem to determine whether G has a cut with edge capacity no more than k in  $O(k \cdot |E(G)|) = O(k^3n^2)$  time. Thus, we can determine whether  $l_{new} \leq L$  in  $O(k^3n^2)$  time.

Obviously, lnew is from the following set

$$\{l(u) - \phi \cdot d + 1 \mid u^d \text{ is in } \mathcal{E}_v^{kn}\}$$

whose size is  $O(kn^2)$ , the number of nodes in  $\mathcal{E}_v^{kn}$ . We can first sort all the values in the set, and then use binary search to determine  $l_{new}$ . Overall, we have an  $O(k^3n^2\log(kn))$ -time algorithm for determining  $l_{new}$ .

L\_FIND( $N, \phi$ ) needs to call Procedure IMPROVE  $O(n^2)$  times in the worst case. In summary, we have the following result:

Theorem 2 The labels of all nodes in N can be determined in  $O(k^3 n^4 \log(kn))$  time.

Remark: To guarantee that a mapping solution with the target clock period can always be found whenever there exists one, we need to use the expanded circuit  $\mathcal{E}^{kn}$ . This is the worst case scenario. In practice, we may use an expanded circuit  $\mathcal{E}^i$  for an i considerably smaller than kn. For instance, for node c in the circuit in Figure 1(a), it can be shown that it is sufficient to use  $\mathcal{E}^2_c$  (in Figure 5(d)) for examining the 3-LUTs for c. To make our algorithm flexible and to save computation time, we can use i as a control parameter so that the expanded circuit  $\mathcal{E}^i$ , instead of  $\mathcal{E}^{kn}$  is used in Procedure IMPROVE.

#### 5.2 The mapping phase

The purpose of this phase is to generate a mapping solution with a clock period of  $\phi$  or less (if, of course, there is one such mapping solution).

The first step is to assemble a mapping solution from the LUTs corresponding to the cuts that realize the labels. To do so, we trace from the POs backward and to include those LUTs that are on paths from PIs to POs in the mapping solution. Specifically, we keep two lists D and U. D is the set of nodes in N whose k-LUTs have already been included in the partial mapping solution and U is the set of nodes whose k-LUTs are inputs to some k-LUTs in D and have not yet been included in the partial mapping solution. At the beginning, D consists of the PIs and U consists of the POs. At each iteration, a node v in U is removed and added to D. Let the k-LUT that realizes  $l^{opt}(v)$  be  $\mathcal{L}_v$  which is determined in the labeling phase. Then, if u after passing d FFs is an input to  $\mathcal{L}$  we create an edge from  $\mathcal{L}_u$  to  $\mathcal{L}_v$ with weight d in S, and add u to U if it is not in D or U. This process stops when U becomes empty. Let S denote the resulting mapping solution. After the process is finished, D may not contain all the nodes in N. For those nodes not in D, they disappear because they are contained in some of the LUTs.

We now define a retiming r on S. For each LUT  $\mathcal{L}_v$  in S, the retiming value is as follows:

$$r(\mathcal{L}_{v}) = \begin{cases} 0 & v \text{ is a PI or PO} \\ \left\lceil \frac{l^{opt}(v)}{\phi} \right\rceil - 1 & \text{otherwise.} \end{cases}$$

Let  $S_r$  denote the circuit obtained from S by applying retiming r. Note that by definition  $S_r$  is also a mapping solution of N. We have the following result:

Theorem 3 The following three statements are equivalent:

- N has a mapping solution with a clock period of φ or less.

- (ii)  $l^{opt}(v) \le \phi + 1$  for each PO v in N.

- (iii)  $S_r$  has a clock period of  $\phi$  or less.

Based on Theorem 3, we can check whether there is a PO whose label is larger than  $\phi+1$  after the labeling phase. If this is the case, the algorithm will not proceed to the mapping phase because there is simply no mapping solution with the target clock period  $\phi$ . If for each PO, its label is less than or equal to  $\phi+1$ , the algorithm simply return  $S_r$  since it meets the target clock period  $\phi$ .

#### 6 Experimental results

Our optimal clock period mapping algorithm has been implemented in the C language (referred to as SeqMapII). Experiments were carried out on sequential benchmark circuits in the LGSynth91 suite. In this section, we describe our experiments and summarize the results.

For comparison, we also implemented a technology mapping algorithm based on existing approaches which will be referred to as ComMap. ComMap maps a sequential circuit by mapping the combinational logic between FFs using FlowMap — a delay optimal technology mapping algorithm for combinational circuits [2]. ComMap also uses retiming as a pre-processing step as well as a post-processing step. Specifically, it retimes the initial circuit to the minimum clock period before applying FlowMap. It also retimes the mapping solution to the minimum clock period after FlowMap. The resulting circuit is then the output of ComMap.

We tested both ComMap and SeqMapII on a set of benchmark circuits using 5-LUTs. The results are summarized in Table 1. In Table 1, under column initial we list the number of gates and the number of FFs of each benchmark circuit (decomposed using tech\_decomp -a 2 -o 2 in SIS). Under column ComMap, we list the number of LUTs, the number of FFs, and the clock period  $(\phi)$  of the mapping solution produced by ComMap. The same quantities are also listed for SeqMapII. For SeqMapII, we set the control parameter i, the depth of the expanded circuits used to form LUTs, to be 6 in the experiments. (Therefore, the clock periods of the mapping solutions produced by SeqMapII might not be minimum.) Even with such a small depth, SeqMapII consistently produced mapping solutions with smaller clock periods than that produced by ComMap as can be observed from the table. This clearly shows the advantage of the new approach. It can also be seen that the mapping solutions produced by SeqMapII usually have fewer LUTs than that produced by ComMap. This was also expected since SeqMapII can form LUTs by extending across FF boundaries. Overall, the mapping solutions produced by ComMap use 10% more LUTs, 33% larger clock periods, and 2% less FFs. For all the test circuits except s38417, the CPU times of our current implementation of SeqMapII were less than two minutes and in most cases only a few seconds on a SPARC 5 workstation with 32Mb memory. However, for s38417 it took SeqMapII close to 30 minutes due to the large size of the circuit and a larger reduction in the clock period. Overall, the CPU times of SeqMapII are about 10 times that of ComMap for the test circuits.

#### 7 Conclusions

In this paper, we studied the FPGA technology mapping problem for sequential circuits in the most general setting. In our approach, retiming is fully integrated into the mapping process. As a result, the mapping solution space explored by our approach is much larger than what existing approaches are able to explore. Another way to understand our approach is that for our approach, there is no FF boundary at all, in the sense that if one circuit is obtained from another one by retiming, our algorithm will produce the same mapping solution for both circuits. In other words, where to place the

| test    | Initial |      | Co   | mMap | SeqMapII |      |      |    |

|---------|---------|------|------|------|----------|------|------|----|

| circuit | gates   | FFs  | LUTs | FFs  | φ        | LUTs | FFs  | φ  |

| exl     | 326     | 20   | 202  | 56   | 6        | 209  | 60   | 5  |

| ex5     | 105     | 9    | 72   | 29   | 4        | 58   | 24   | 3  |

| mult16a | 261     | 16   | 75   | 58   | 3        | 38   | 55   | 2  |

| mult32a | 533     | 32   | 153  | 202  | 3        | 78   | 207  | 2  |

| s344    | 109     | 15   | 50   | 40   | 3        | 36   | 36   | 2  |

| s349    | 112     | 15   | 49   | 39   | 3        | 33   | 33   | 2  |

| s382    | 148     | 21   | 73   | 49   | 3        | 64   | 43   | 2  |

| s400    | 158     | 21   | 72   | 47   | 3        | 66   | 46   | 2  |

| s444    | 169     | 21   | 77   | 51   | 3        | 64   | 43   | 2  |

| s526    | 252     | 21   | 166  | 84   | 3        | 127  | 89   | 2  |

| s526n   | 251     | 21   | 166  | 85   | 3        | 140  | 97   | 2  |

| s953    | 348     | 29   | 196  | 61   | 5        | 202  | 54   | 4  |

| s1488   | 734     | 6    | 339  | 63   | 5        | 266  | 25   | 4  |

| s9234   | 2352    | 193  | 590  | 270  | 5        | 593  | 276  | 4  |

| s15850  | 3852    | 522  | 1670 | 704  | 9        | 1627 | 818  | 8  |

| s38417  | 8709    | 1583 | 4170 | 2503 | 8        | 3761 | 2507 | 6  |

| Total   |         |      | 8120 | 4341 | 69       | 7362 | 4413 | 52 |

| Ratio   |         |      | 1.10 | .98  | 1.33     | 1    | 1    | 1  |

Table 1: Experimental results.

FFs in a circuit has no effect on our algorithm. On the other hand, for a mapping algorithm based on existing approaches, there always exist FF boundaries and signal dependencies across FF boundaries are severed. We further presented a polynomial mapping algorithm which can produce mapping solutions with the minimum clock periods.

#### References

- N. Bhat and D. Hill. Routable technology mapping for FP-GAs. In ACM/SIGDA Workshop on FPGAs, pages 143-148, 1992.

- [2] J. Cong and Y. Ding. FlowMap: An optimal technology mapping algorithm for delay optimization in lookup-table based FPGA designs. IEEE Trans. on Computer-Aided Design, 13:1-11, 1994.

- [3] J. Cong and Y. Ding. On area/depth trade-off in LUT-based FPGA technology mapping. IEEE Trans. on VLSI Systems, 2:137-148, 1994.

- [4] A. H. Farrahi and M. Sarrafzadeh. Complexity of the lookup-table minimization problem for FPGA technology mapping. IEEE Trans. on Computer-Aided Design, 13:1319-1332, 1994.

- [5] R. J. Francis, J. Rose, and Z. Vranesic. Chortle-crf: Fast technology mapping for lookup table-based FPGAs. In ACM/IEEE Design Automation Conf. (DAC), pages 227-233, 1991.

- [6] R. J. Francis, J. Rose, and Z. Vranesic. Technology mapping for lookup table-based FPGAs for performance. In Intl. Conf. on Computer-Aided Design (ICCAD), pages 568-571, 1991.

- [7] K. Karplus. Xmap: A technology mapper for table-lookup FPGAs. In ACM/IEEE Design Automation Conf. (DAC), pages 240-243, 1991.

- [8] C. E. Leiserson, F. M. Rose, and J. B. Saxe. Optimizing synchronous circuitry by retiming. In Proc. 3rd Caltech Conf. on VLSI, pages 87-116, 1983.

- [9] A. Mathur and C. L. Liu. Performance driven technology mapping for lookup-table based FPGAs using the general delay model. In ACM/SIGDA Workshop on Field Programmable Gate Arrays, 1994.

- [10] R. Murgai, R.K. Brayton, and A. Sangiovanni-Vincentelli. Sequential synthesis for table look up programmable gate arrays. In ACM/IEEE Design Automation Conf. (DAC), pages 224-229, 1993.

- [11] R. Murgai, N. Shenoy, R.K. Brayton, and A. Sangiovanni-Vincentelli. Improved logic synthesis algorithms for table look up architectures. In Intl. Conf. on Computer-Aided Design (ICCAD), pages 564-567, 1991.

- [12] P. Pan and C. L. Liu. Technology mapping of sequential circuits for LUT-based FPGAs for performance. In ACM/SIGDA Intl. Symposium on Field-Programmable Gate Arrays, pages 58-64, 1996.

- [13] P. Sawkar and D. Thomas. Area and delay mapping for table-look-up based field programmable gate arrays. In ACM/IEEE Design Automation Conf. (DAC), pages 368-373, 1992.

- [14] M. Schlag, J. Kong, and P.K. Chan. Routability-driven technology mapping for lookup table-based FPGA's. IEEE Trans. on Computer-Aided Design, 13:13-26, 1994.

- [15] U. Weinmann and W. Rosenstiel. Technology mapping for sequential circuits based on retiming techniques. In Proc. European Design Automation Conf., pages 318-323, 1993.

- [16] N.-S. Woo. A heuristic method for FPGA technology mapping based on the edge visibility. In ACM/IEEE Design Automation Conf. (DAC), pages 248-251, 1991.

- [17] Xilinx. The Programmable Gate Arrays Data Book. Xilinx, San Jose, CA, 1993.

- [18] H. Yang and D. F. Wong. Edge-Map: Optimal performance driven technology mapping for iterative LUT based FPGA designs. In Intl. Conf. on Computer-Aided Design (ICCAD), pages 150-155, 1994.

## Structural Gate Decomposition for Depth-Optimal Technology Mapping in LUT-based FPGA Design

Jason Cong and Yean-Yow Hwang

Department of Computer Science University of California, Los Angeles

#### Abstract

In this paper, we study the problem of decomposing gates in fanin-unbounded or K-bounded networks such that the K-input LUT mapping solutions computed by a depthoptimal mapper have minimum depth. We show (1) any decomposition leads to a smaller or equal mapping depth regardless the decomposition algorithm used, and (2) the problem is NP-hard for unbounded networks when  $K \ge 3$ and remains NP-hard for K-bounded networks when  $K \ge 5$ . We propose a gate decomposition algorithm, named DOGMA, which combines level-driven node packing technique (Chortle-d) and the network flow based optimal labeling technique (FlowMap). Experimental results show that networks decomposed by DOGMA allow depthoptimal technology mappers to improve the mapping solutions by up to 11% in depth and up to 35% in area comparing to the mapping results of networks decomposed by other existing decomposition algorithms.

#### 1. Introduction

The lookup-table (LUT) based FPGAs have been a popular technology for VLSI ASIC design and system prototyping. A K-input LUT (K-LUT) can implement any function of up to K variables. The goal of LUT-based FPGA technology mapping is to cover a given network using LUTs such that either area or delay is minimized or routability is maximized in the final LUT network. The delay of a network can be estimated by the number of levels (i.e. depth). Two factors affect the mapping solution depth: the gate decomposition before mapping and the mapping algorithm. Several LUT mapping algorithms have been proposed for depth minimization [6, 9, 2]. In particular, the FlowMap algorithm [2] guarantees a depth-optimal mapping solution for any K-bounded network. However, FlowMap can not be applied directly to unbounded networks. Gate decomposition can be classified into structural decomposition and Boolean decomposition. The structural decomposition replaces multi-fanin (simple) gates by fanin trees while the Boolean decomposition decomposes the functionality of gates. This paper focuses on structural decomposition for depth minimization in LUT mapping.

33rd Design Automation Conference®

Permission to make digital/hard copy of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for

profit or commercial advantage, the copyright notice, the title of the publication and

its date appear, and notice is given that copying is by permission of ACM, Inc. To

copy otherwise, to republish, to post on servers or to redistribute to lists, requires

prior specific permission and/or a fee.

DAC 96 - 06/96 Las Vegas, NV, USA

□1996 ACM □-89791-779-0/96/0006..\$3.50

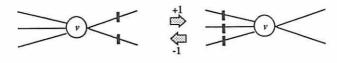

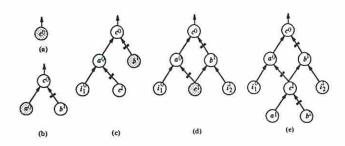

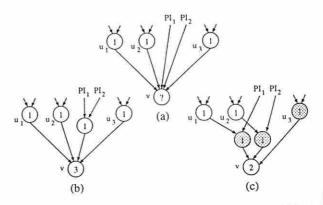

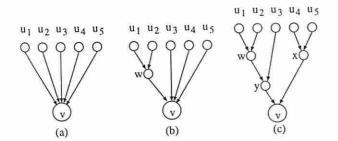

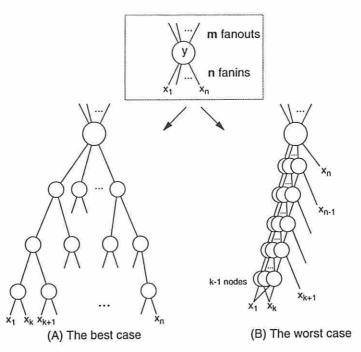

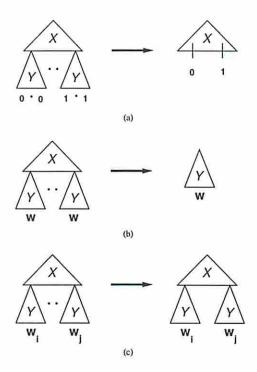

Gate decomposition affects the mapping solution depth significantly. For example, assume K=3. The network N in Figure 1(a) is not K-bounded. If node  $\nu$  is decomposed in the way shown in Figure 1(b), there is no way to obtain a mapping solution of depth less than 3. However, if the decomposition shown in Figure 1(c) is carried out for node  $\nu$ , a mapping solution of depth equal to 2 can be obtained. Even for K-bounded networks, the depth of mapping solutions computed by FlowMap may decrease if gates are further decomposed before mapping [4].

Several gate decomposition routines have been used for LUT-mapping. The tech\_decomp and the speed\_up in SIS [10] and the dmig in [1] focus on minimizing the number of levels in the decomposed network. They do not directly minimize the depth of the mapping solution. Chortle-d [6] computes depth-optimal gate decomposition and mapping solutions for tree networks (may be unbounded) but produces suboptimal results for general networks. In this paper, we study the structural gate decomposition problem to decompose gates in a general network such that a mapping solution of minimum depth can be obtained.

The remainder of this paper is organized as follows. Section 2 defines basic terminology, presents properties of structural gate decomposition and formulates the problem. Section 3 gives the complexity results. A novel gate decomposition algorithm for depth-optimal mapping is presented in Section 4. Experimental results are presented in Section 5 and Section 6 concludes the paper.

Figure 1 Decomposition of node v (K=3). (a) initial network, (b) decomposition yielding mapping depth = 3, (c) decomposition yielding mapping depth = 2.

#### 2. Problem Formulation

Let K be the input size of an LUT. Let input(v) be the set of fanin nodes of node v. A primary input (PI) node has no fanins and a primary output (PO) node has no outgoing edges. A network N is K-bounded if every node  $v \in N$  satisfies  $|input(v)| \le K$ . Otherwise, it is an unbounded network. Given a subnetwork H, we use input (H) to denote the set of distinct nodes outside H which supply inputs to nodes in H. Given a node v in network N, let  $N_{\nu}$  denote the subnetwork consisting of node  $\nu$  and all the predecessors of v. The minimum mapping depth of v in N, denoted  $MMD_N(v)$ , is defined as the minimum depth among all possible K-LUT mapping solutions of  $N_{\nu}$ . If  $N_{\nu}$ is unbounded, let  $MMD_N(v) = \infty$ . PI nodes have a mapping depth of 0. The minimum mapping depth of a network N, denoted MMD (N), is the largest mapping depth among all PO nodes. Given a K-bounded network N, the FlowMap [2] algorithm computes  $MMD_N(v)$  for every node  $v \in N$  in polynomial time. A cut in  $N_{\nu}$  is a partition  $(X_{\nu}, X_{\nu})$  of nodes in  $N_{\nu}$  such that PI nodes are in  $X_{\nu}$  and  $\nu \in X_{\nu}$ . The cutset of a cut, denoted  $n(X_v, \overline{X}_v)$ , is defined as input  $(X_v)$ . A cut is K-feasible if  $|n(X_{\nu}, X_{\nu})| \le K$ . The height of a cut, denoted  $height(X_{\nu}, X_{\nu})$ , is the maximum mapping depth for nodes in  $n(X_v, X_v)$ . We have the following lemma based on results in [2].

**Lemma 1** A node  $\nu$  has  $MMD_N(\nu) = p$  if there is a K-feasible cut of height of p-1 in  $N_{\nu}$  but no K-feasible cut of height of p-2 or smaller exists.

Let node  $v \in N$  satisfies |input(v)| > 2. Given a decomposition algorithm D, we define a decomposition step at v by D, denoted  $D_v$ , as follows: Decomposition step  $D_v$  (i) chooses two nodes  $u_1$  and  $u_2$  from input(v), (ii) removes edges  $(u_1,v)$  and  $(u_2,v)$ , (iii) introduces a new node w and new edges  $(u_1,w)$ ,  $(u_2,w)$ , (w,v) and adds them to N. The resulting network is denoted as  $D_v(N)$ . For example, Figure 2(b) shows the result of one decomposition step at node v from Figure 2(a). Obviously, the introduced node w have the same gate type as v. We present two properties of the structural gate decomposition.

Figure 2 Decomposition of node  $\nu$ . (a) Before decomposition, (b)  $D_{\nu}(N)$  after one decomposition step of  $D_{\nu}$ , (c) after a sequence of decomposition steps.

**Lemma 2** Given a network N, any decomposition algorithm D, and any node  $v \in N$ , it must be true that  $MMD(D_v(N)) \le MMD(N)$ .

**Lemma 3** If  $MMD_N(u) = MMD_N(v)$  for all  $u \in input(v)$  in a K-bounded network N, then  $MMD(N) = MMD(D_v(N))$  for any decomposition algorithm D.

According to Lemma 2, the further a network is decomposed, the smaller the mapping depth might be. Therefore, we decompose every gate into a binary fanin tree. Figure 2(c) is a complete decomposition of node  $\nu$ . Every decomposition step introduces one intermediate node and it requires  $|input(\nu)|-2$  steps to decompose  $\nu$ . We formulate the following problems.

Structural Gate Decomposition for K-LUT Mapping (SGD/K) Given a simple-gate unbounded network  $N_{\infty}$ , decompose  $N_{\infty}$  into a 2-input network  $N_2$  such that for any other 2-input network decomposition  $N'_2$  of N,  $MMD(N_2) \leq MMD(N'_2)$ .

Structural Gate Decomposition for K-LUT Mapping of K-bounded Network (K-SGD/K) Given a simple-gate K-bounded network  $N_K$ , decompose  $N_K$  into a 2-input network  $N_2$  such that for any other 2-input network decomposition  $N_2$  of N, MMD  $(N_2) \le MMD$   $(N_2)$ .

There are two issues related to the problem of gate decomposition. (1) A smaller depth might be obtained when several gates are decomposed simultaneously instead of independently [4]. This is because the intermediate nodes could be shared during the decomposition of multiple gates of the same functional type. (2) Gate decomposition can be performed before the mapping phase in a two-step approach or embedded into the mapping process being part of an integrated approach. For example, Chortle-d [6] is an integrated approach (since it decomposes gates and maps LUTs in an interleaving manner) while dmig + FlowMap in [2] uses a two-step approach. We can show that the best two-step approach produces the same optimal mapping depth as that by the best integrated approach [4]. In this paper, we consider only independent gate decompositions Nevertheless, our gate in a two-step approach. decomposition algorithm takes into account the impact of gate decomposition on mapping to obtain a decomposed network which is most suitable for FlowMap to achieve a minimum mapping depth.

#### 3. Complexity of SGD/K and K-SGD/K Problems

In this section, we only state our complexity theorems. Complete proofs can be found in [4].

Theorem 1 The SGD/K problem is NP-hard for  $K \ge 3$ .

**Theorem 2** The K-SGD/K problem is NP-hard for  $K \ge 5$ .

## 4. Gate Decomposition Algorithm for Depth-Optimal LUT Mapping

Our decomposition algorithm, named DOGMA (Depth-Optimal Gate decomposition for MApping),

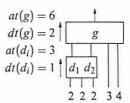

combines the level-driven node packing technique in Chortle-d and the network flow based labeling technique in FlowMap. Given a network N, DOGMA decomposes nodes from PIs to POs in a topological order. Let N(v)denote the network after decomposing the node v. DOGMA labels each node v by  $MMD_{N(v)}(v)$  as follows. Nodes in input(v) are grouped in such a way that each group consists of nodes with the same label (i.e. minimum mapping depth). Groups are processed in an ascending order according to their labels. For a group of nodes labeled p, nodes are packed into a minimum number of bins such that a K-feasible cut of height p-1 exists for the nodes in each bin (checked based on Lemma 1). Such a bin is called a min-height K-feasible bin. A node ui is created for each bin  $B_i$  with fanins from nodes in  $B_i$  and a fanout to v. Node  $u_i$  will be given a label p. Note that according to Lemma 3, no matter  $u_i$  is further decomposed or not, the minimum mapping depth of the network is always the same. We then proceed to the group of a next higher label p+1. For each node  $u_i$  created in the previous step, a buffer node  $w_i$  (with label p+1) is created with  $u_i$  as input. (All the buffer nodes will be removed after decomposition). These buffer nodes together with nodes in the group of label p + 1are again packed into a minimal number of min-height Kfeasible bins. We continue this process until all nodes are packed into one bin which corresponds to the node v.

DOGMA is similar to Chortle-d in that decomposition is done by packing nodes into a *minimal* number of min-height K-feasible bins. However, Chortle-d integrates gate decomposition with technology mapping, and computes mapping depth based on the partially generated LUT network. Since the fanin constraint is not a *monotone* clustering constraint [2], Chortle-d may obtain inaccurate node mapping depth. Besides, Chortle-d enumerates all packing combinations for nodes on reconvergent paths, which is quite expensive. In contrast, DOGMA computes mapping depth as well as packs nodes into bins (to be discussed) using the network flow based computation. The mapping depth is always accurate and the reconvergent paths are taken into account naturally.

The problem remains to be solved is the min-height K-feasible bin packing problem defined as follows.

Min-Height K-Feasible Bin Packing Problem Given a set  $S_p \subseteq input(v)$  of nodes of minimum mapping depth p when decomposing node v, partition  $S_p$  into a minimal number of bins such that there is a K-feasible cut of height p-1 for nodes in each bin.

We shall give three heuristics and one exact method to solve the problem. Our heuristics are based on the maxflow algorithm and bin-packing heuristics. We define the total cut size  $TC_p(S)$  of a set S of nodes with label p to be the size of the min-cut of height p-1 which separates S from all PIs. A set X of nodes of label p can be packed into one bin as long as  $TC_p(X) \le K$ . Nodes are packed in a decreasing order of individual cut sizes. The first two heuristics, named MC-FFD and MC-BFD, to the min-height

K-feasible bin packing problem are based on the first-fit-decreasing (FFD) and best-fit-decreasing (BFD), which are two heuristics for the bin packing problem [8]. The third method is the maximal-share-decreasing (MC-MSD) heuristic which packs nodes that can maximally share a cut together. The fourth method is inspired by the dynamic programming approach for the number partitioning problem [7]. Instead of partitioning numbers, we ask whether there is a way to partition the nodes in  $S_p$  into k subsets  $X_1, X_2, \dots, X_k$  such that  $TC_p(X_i) \le K$   $(1 \le i \le k)$ . We can solve the problem by dynamic programming. By searching the minimal k  $(k = 2, 3, \dots)$ , the min-height K-feasible bin packing problem can be solved optimally. We refer to this method as the MC-DP algorithm. The details of these algorithms can be found in [4].

#### 5. Experimental Results

We have implemented the DOGMA algorithm with MC-FFD, MC-BFD, MC-MSD, and MC-DP packing methods using the C language and incorporated our implementation into the RASP FPGA synthesis system [5]. In our experiments, we optimize the MCNC benchmark circuits for area using standard SIS scripts, decompose them into simple gate networks, apply gate decomposition routines to obtain 2-input networks, and obtain the final LUT networks using a depth-optimal technology mapper. We choose K=5 in the experiments.

We compare the performance of our four methods for the min-height K-feasible bin packing in DOGMA and observe that the impact of the four methods on mapping results is almost the same. Since MC-FFD is faster than other three methods, DOGMA employs MC-FFD to solve the packing problem. We compare DOGMA with two decomposition routines: the tech\_decomp in SIS [10] and the dmig in [1]. The tech\_decomp routine is based on a balanced-tree heuristic which only minimizes the gate level locally. The dmig routine minimizes the gate level of the decomposed networks. The decomposed networks by the three algorithms are all mapped by CutMap [3], an enhancement of FlowMap. The results are shown in Table 1. We see CutMap produces the same or smaller depth for circuits decomposed by DOGMA. On average, DOGMA allows CutMap to achieve 10% and 4% depth reduction comparing to tech decomp and dmig, respectively.

We compare DOGMA + CutMap with existing gate decomposition and depth-oriented mapping algorithms. The tested circuits are area-optimized MCNC benchmarks. The mappers TechMap-D [9], FlowMap [2], and CutMap [3] are used for comparison. The *dmig* was used in [2] while the *speed\_up* was used in [9] and [3] to prepare 2-input networks for technology mapping. The results are in Table 2. Comparing results from [2,3] with ours, we see gate decomposition routines *speed\_up*, *dmig*, and DOGMA decompose gates equally well in terms of mapping depth. However, networks decomposed by DOGMA allow CutMap to reduce 16% of LUTs in the mapping solutions.

|         | tech_decomp |             | dmig |     | DOGMA |    |

|---------|-------------|-------------|------|-----|-------|----|

| Circuit | LUT         | d           | LUT  | d   | LUT   | d  |

| 5xp1    | 24          | 3           | 23   | 3   | 24    | 3  |

| 9sym    | 66          | 5           | 66   | 5   | 59    | 5  |

| apex2   | 154         | 6           | 155  | 5   | 151   | 5  |

| apex4   | 770         | 7           | 792  | 6   | 770   | 5  |

| clip    | 37          | 4           | 37   | 4   | 38    | 3  |

| con1    | 3           |             | 3    | 2   | 3     | 2  |

| duke2   | 160         | 2<br>5<br>9 | 173  | 4   | 177   | 4  |

| e64     | 108         | 9           | 108  | 9   | 108   | 9  |

| misex l | 18          | 2 3         | 18   | 2   | 16    | 2  |

| misex2  | 32          | 3           | 31   | 3   | 36    | 2  |

| misex3  | 179         | 17          | 174  | 16  | 176   | 16 |

| rd73    | 25          | 3           | 27   | 3   | 23    | 3  |

| rd84    | 52          | 4           | 52   | 4   | 54    | 4  |

| sao2    | 47          | 4           | 44   | 4   | 42    | 4  |

| vg2     | 23          | 4           | 29   | 3   | 29    | 3  |

| Total   | 1698        | 78          | 1732 | 73  | 1706  | 70 |

|         | -0.5%       | +11%        | +2%  | +4% | 1     | 1  |

Table 1 Comparison of tech\_decomp, dmig and DOGMA.

In [9], TechMap-D obtained the smallest depth because it integrated logic synthesis into technology mapping. However, 35% more LUTs are generated comparing to DOGMA + CutMap.

|         | [9]       | [2]      | [3]       | Ours     |

|---------|-----------|----------|-----------|----------|

|         | speed_up  | dmig     | speed_up  | DOGMA    |

|         | TechMap-D | FlowMap  | CutMap    | CutMap   |

| Circuit | LUT(d)    | LUT(d)   | LUT(d)    | LUT(d)   |

| 5xp1    | 17 (2)    | 22 (3)   | 23 (3)    | 24 (3)   |

| 9sym    | 9 (3)     | 60 (5)   | 62 (5)    | 59 (5)   |

| 9symml  | 9 (3)     | 55 (5)   | 58 (5)    | 50 (4)   |

| C499    | 148 (4)   | 68 (4)   | 143 (5)   | 68 (4)   |

| C880    | 213 (7)   | 124 (8)  | 205 (8)   | 98 (8)   |

| alu2    | 197 (8)   | 155 (9)  | 144 (8)   | 138 (9)  |

| apex6   | 252 (5)   | 238 (5)  | 233 (4)   | 231 (5)  |

| apex7   | 86 (4)    | 79 (4)   | 80 (4)    | 68 (4)   |

| count   | 71 (4)    | 31 (5)   | 69 (3)    | 31 (5)   |

| des     | 1395 (8)  | 1310 (5) | 986 (5)   | 938 (5)  |

| duke2   | 175 (4)   | 174 (4)  | 178 (4)   | 173 (4)  |

| misex1  | 18 (2)    | 16 (2)   | 15 (2)    | 16 (2)   |

| rd84    | 16 (3)    | 46 (4)   | 45 (4)    | 53 (4)   |

| rot     | 315 (6)   | 234 (7)  | 239 (6)   | 210 (7)  |

| vg2     | 36 (4)    | 29 (3)   | 39 (4)    | 27 (3)   |

| z4ml    | 9 (2)     | 5 (2)    | 12 (3)    | 5 (2)    |

| Total   | 2966(69)  | 2646(75) | 2531(73)  | 2189(74) |

|         |           | +21%(+1% | )+16%(-1% | 1(1)     |

Table 2 Comparison of DOGMA + CutMap with previous results.

#### 6. Conclusion

In this paper, we study the structural gate decomposition for depth-optimal LUT mapping. We show gate decomposition leads to a smaller or equal mapping depth regardless the decomposition algorithm used, and the problem is NP-hard for unbounded networks when  $K \ge 3$  and remains NP-hard for K-bounded networks when  $K \ge 5$ . We propose a gate decomposition algorithm (DOGMA) for depth-optimal mapping. Experimental results show a reduction of up to 10% in mapping depth. Together with CutMap, we achieve comparable mapping depth with up to 35% reduction in area comparing to previous results.

#### Acknowledgement

This work is partially supported by NSF Young Investigator (NYI) Award MIP-9357582, and grants from Xilinx, Xerox PARC, and AT&T Microelectronics under NSF NYI and California MICRO programs. The authors would like to thank Dr. Robert Francis for his helpful discussions.

#### References

- [1] Chen, K. C., J. Cong, Y. Ding, A. B. Kahng, and P. Trajmar, "DAG-Map: Graph-based FPGA Technology Mapping for Delay Optimization," *IEEE Design and Test of Computers*, pp. 7-20, Sep. 1992.

- [2] Cong, J. and Y. Ding, "An Optimal Technology Mapping Algorithm for Delay Optimization in Lookup-Table Based FPGA Designs," *IEEE Trans. on Computer-Aided Design*, Vol. 13, pp. 1-12, Jan. 1994.

- [3] Cong, J. and Y.-Y. Hwang, "Simultaneous Depth and Area Minimization in LUT-Based FPGA Mapping," Proc. ACM 3rd Int'l Symp. on FPGA, pp. 68-74, Feb. 1995.

- [4] Cong, J. and Y.-Y. Hwang, "Structural Gate Decomposition for Depth-Optimal Technology Mapping in LUT-based FPGA," in UCLA Computer Science Dept. Tech. Report CSD-950045, (December 1995).

- [5] Cong, J., J. Peck, and Y. Ding, "RASP: A General Logic Synthesis System for SRAM-based FPGAs," Proc. ACM 4th Int'l Symp. on FPGA, Feb. 1996.

- [6] Francis, R. J., J. Rose, and Z. Vranesic, "Technology Mapping of Lookup Table-Based FPGAs for Performance," Proc. IEEE Int'l Conf. on CAD, pp. 568-571, Nov. 1991.

- [7] Garey, M. and D. Johnson, Computer and Intractability: A Guide to the Theory of NP-Completeness, Freeman, San Francisco (1979).

- [8] Horowitz, E. and S. Sahni, Fundamentals of Computer Algorithms, Computer Science Press, Potomac, Maryland (1978).

- [9] Sawkar, P. and D. Thomas, "Performance Directed Technology Mapping for Look-Up Table Based FPGAs," Proc. 30th ACM/IEEE Design Automation Conf., pp. 208-212, June 1993.

- [10] Sentovich, E., K. Singh, L. Lavagno, C. Moon, R. Murgai, A. Saldanha, H. Savoj, P. Stephen, R. Brayton, and A. Sangiovanni-Vincentelli, "SIS: A System for Sequential Circuit Synthesis," U.C.Berkeley Technical Report UCB/ERL M92/41, May, 1992.

## A Boolean Approach to Performance-Directed Technology Mapping for LUT-Based FPGA Designs

Christian Legl\* Bernd Wurth\*\* Klaus Eckl\*

\*Institute of Electronic Design Automation, Technical University of Munich, 80290 Munich, Germany

\*\*Synopsys, Inc., 700 E. Middlefield Rd., Mountain View, CA 94043

Abstract — This paper presents a novel, Boolean approach to LUT-based FPGA technology mapping targeting high performance. As the core of the approach, we have developed a powerful functional decomposition algorithm. The impact of decomposition is enhanced by a preceding collapsing step. To decompose functions for small depth and area, we present an iterative, BDD-based variable partitioning procedure. The procedure optimizes the variable partition for each bound set size by iteratively exchanging variables between bound set and free set, and finally selects a good bound set size. Our decomposition algorithm extracts common subfunctions of multiple-output functions, and thus further reduces area and the maximum interconnect lengths. Experimental results show that our new algorithm produces circuits with significantly smaller depths than other performance-oriented mappers. This advantage also holds for the actual delays after placement and routing.

#### 1 INTRODUCTION

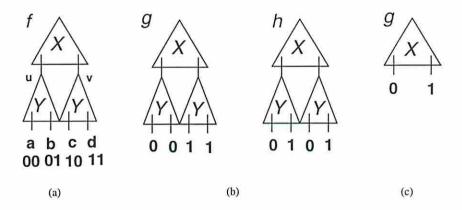

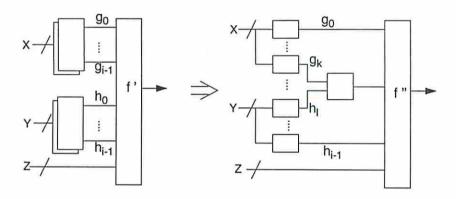

An important class of FPGAs is based on the lookup-table (LUT) as the basic programmable logic block. A k-LUT implements any Boolean function of up to k variables. The LUTs are wired by various kinds of programmable interconnects [1]. Minimizing the delay of LUT-based FPGA designs is an important task because the programmable interconnects introduce extra delay compared with conventional gate array or standard cell technologies. The performance of an FPGA design is determined by the number of LUTs and the interconnect delays on the critical path.

Performance-driven technology mapping for LUT-based FPGAs is to transform a Boolean network, which has been produced in the technology independent logic optimization phase, into a functionally equivalent LUT network with minimum circuit delay. Technology mapping of a Boolean network is usually performed in two steps: The first step is the decomposition of nodes with more than k inputs into smaller nodes with k or less inputs. The resulting network is called k-bounded. A subsequent covering step finds a circuit of LUTs covering the k-bounded network.

A variety of technology mapping algorithms tackle performance optimization by minimizing the depth of k-bounded networks. Chortle-d, which is based on tree decomposition and bin-packing, is depth-optimal for trees [2]. DAG-Map heuristically minimizes the depth of a general k-bounded network [3]. The FlowMap algorithm is a significant advance since it guarantees a depth-optimal covering for general k-bounded networks [4].

However, minimizing the network depth does not consider the interconnect delays. Since the maximum interconnect length on the chip is correlated with the circuit area, minimizing the area also contributes to delay minimization. This is considered in the FlowMap-[5] algorithm, which achieves depth-optimal mappings as FlowMap but reduces the number of LUTs. Recent algorithms improve on the FlowMap algorithm by modeling interconnect delay more accurately. This is done by assigning different delays to different nets (nominal delay model [6]) or even to the different interconnections of the same net [7]. The combination of the technology mapping and layout synthesis phases has been proposed to achieve small interconnect delays and improve routability [8, 9].

Another class of performance-directed algorithms performs Boolean operations during the covering step. Collapsing of criti-

33rd Design Automation Conference®

Permission to make digital/hard copy of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for

profit or commercial advantage, the copyright notice, the title of the publication and

its date appear, and notice is given that copying is by permission of ACM, Inc. To

copy otherwise, to republish, to post on servers or to redistribute to lists, requires

prior specific permission and/or a fee.

DAC 96 - 06/96 Las Vegas, NV, USA 01996 ACM 0-89791-779-0/96/0006...\$3.50 cal nodes and re-decomposition are employed in MIS-pga(delay) [8], TechMap-D [10] and FlowSYN [11]. The FlowMap-based FlowSYN algorithm, which uses an efficient functional decomposition method, outperforms FlowMap-r in terms of circuit depth and area.

All these performance-directed mapping algorithms concentrate on the covering step. To obtain a k-bounded network in the decomposition step, the DMIG algorithm [3] and SIS-algorithms [12] like xl.k.decomp, speed\_up, and tech\_decomp are used. The decomposition step typically yields a network in which each gate has at most two inputs. This maximizes the flexibility during the covering step. A reason for the little attention given to the decomposition step is the fact that technology independent logic optimization generates Boolean networks with relatively small nodes. Thus, decomposition has only local effect, whereas a state-of-the-art covering step can deal with the entire network and therefore dominates the final result.

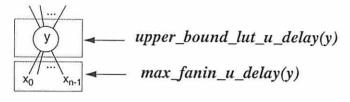

In this paper, we present a novel, Boolean approach to performance-directed technology mapping. As a first step, delay-driven collapsing is performed. In contrast to previous mapping approaches, large network portions are collapsed such that the decomposition step can have a significant impact. As the core of our approach, we have developed a powerful, functional decomposition algorithm that creates k-bounded networks with small depth and area. The main components of the decomposition algorithm are: First, a BDD-based, iterative variable partitioning procedure that efficiently evaluates a large number of variable partitions for their effect on circuit depth and area. Second, we have developed cost functions that estimate the delay and area of Boolean functions after decomposition and determine the effectiveness of the variable partitioning procedure. Third, we use a multiple-output decomposition approach which extracts common subfunctions.

The rest of the paper is organized as follows. Section 2 reviews the state of the art in functional decomposition. In Section 3, we present our performance-directed variable partitioning procedure. Section 4 describes the overall approach. We show experimental results in Section 5, and conclude the paper in Section 6.

### 2 REVIEW OF FUNCTIONAL DECOMPOSITION

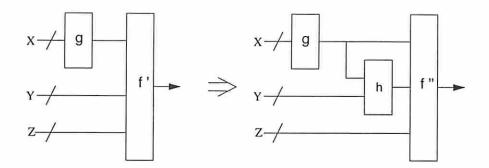

Single-output decomposition. We first review the functional single-output decomposition which is based on the theory of Curtis [13], Roth and Karp [14]. Functional single-output decomposition breaks a function  $f(\mathbf{x}, \mathbf{y})$  into the composition function  $g(\mathbf{v}, \mathbf{y})$  and the subfunction vector  $\mathbf{d}(\mathbf{x}) = (d_1(\mathbf{x}), \dots, d_c(\mathbf{x}))$  such that  $f(\mathbf{x}, \mathbf{y}) = g(\mathbf{d}(\mathbf{x}), \mathbf{y})$ . We deal with disjoint decompositions, where the bound set  $BS = \{x_1, \dots, x_b\}$  and the free set  $FS = \{y_1, \dots, y_{n-b}\}$  are disjoint sets where b is the size of the bound set and n is the number of inputs of f. In non-trivial decompositions, composition function g as well as the subfunctions  $d_i$  have fewer inputs than the original function f. Therefore, functional decomposition can be recursively used to compute k-bounded networks.

Two problems must be solved to perform functional decomposition. First, the input variables of f must be partitioned into the bound set and the free set. This is the variable partitioning problem. Second, given a variable partition, a minimum number c of subfunctions  $d_i$  must be computed. This number c depends on the variable partition.

We deal with the second problem first. To compute subfunctions  $d_i$ , the notion of compatible BS-vertices was introduced [14]. Two BS-vertices  $\hat{\mathbf{x}}_v \in \{0,1\}^b$  and  $\hat{\mathbf{x}}_w \in \{0,1\}^b$  are compatible, denoted by  $\hat{\mathbf{x}}_v \sim \hat{\mathbf{x}}_w$ , if and only if  $\forall \hat{\mathbf{y}} \in \{0,1\}^{n-b}$ :  $f(\hat{\mathbf{x}}_v,\hat{\mathbf{y}}) = f(\hat{\mathbf{x}}_w,\hat{\mathbf{y}})$ . For completely specified functions, compatibility is an equivalence relation, which partitions the set of BS-vertices into compatible classes. The number of compatible classes is denoted by  $\ell$ . The decomposition condition states that a decomposition with the subfunction vector  $\mathbf{d}$  exists if and only if  $\forall \hat{\mathbf{x}}_v, \hat{\mathbf{x}}_w \in \{0,1\}^b$ :  $\hat{\mathbf{x}}_v \not\sim \hat{\mathbf{x}}_w \Longrightarrow \mathbf{d}(\hat{\mathbf{x}}_v) \neq \mathbf{d}(\hat{\mathbf{x}}_w)$ , i.e., different

codes  $d(\hat{x})$  must be assigned to incompatible BS-vertices. Thus, the minimum number c of subfunctions is  $c = \lceil \log_2 \ell \rceil$ . A simple method to compute subfunctions and to fulfill the decomposition condition is to assign a unique code of length c to each compatible class.

It is obvious that the computation of  $\ell$  is an important subtask of functional decomposition. Roth and Karp [14] described how  $\ell$  is computed using a SOP representation of the function f. Lai et al. showed that the computation is significantly sped up if the function f is represented by a BDD in which the bound set variables are ordered before the free set variables [15]. Lai introduced a set of BDD nodes called  $cut\_set(f,b)$  comprising all BDD nodes that have a level greater than b and a predecessor with a level less than or equal to b. Each node  $v \in cut\_set(f,b)$  is in a one-to-one correspondence to a compatible class. Thus, the number of compatible classes is given by the cardinality of  $cut\_set(f,b)$ .