# EARLY SYSTEM ARCHITECTURE OPTIMIZATION FOR MULTI-CHIP SYSTEMS

by

Dong-Hyun Heo

A Dissertation Presented to the FACULTY OF THE GRADUATE SCHOOL UNIVERSITY OF SOUTHERN CALIFORNIA

In Partial Fulfillment of the Requirements for the Degree DOCTOR OF PHILOSOPHY

(Computer Engineering)

December 1997

Copyright 1997 Dong-Hyun Heo

# Dedication

To my mother, wife, and children

### Acknowledgements

I take this opportunity to express my gratitude to those who have made this thesis possible. I am grateful to my advisor Prof. Alice Parker for her constant guidance and inspiration during my dissertation work. She has been a great source of encouragement and support. I also wish to thank Profs. Peter Beerel and Cliff Neuman for being on my dissertation committee, and Profs. Melvin Breuer, C.P. Ravikumar, and Douglas Ierardi for being on my guidance committee.

I would like to thank my colleagues Diogenes Silva, Suhrid Wadekar, J.C. Batista-Desouza, Chih-Tung Chen, and Pravil Gupta for their friendship and help. I benefitted greatly from interacting with them.

There are many other friends who made my years at USC pleasant. Among them, I especially thank for Kang Woo Lee, Jae Won Oh, Jung Hyun Han, Jae Heon Jung, Jong Woo Bae, and Jong Hyun Kahng.

My family have been a continuous source of love, support and sacrifice. I dedicate this thesis to them. I especially thank my wife Hye-Kyung for her patience through these years.

This research was supported by the Advanced Research Projects Agency (Contract No. JFBI90092) and National Science Foundation (Contract No. GER-9023979). I would like to thank these organizations for their support.

# Contents

| D  | edicat | ion                                              |

|----|--------|--------------------------------------------------|

| A  | cknov  | vledgements                                      |

| Li | st Of  | Figures                                          |

| Li | st Of  | Tables                                           |

| A  | bstrac | et x                                             |

| 1  | Intro  | oduction                                         |

|    | 1.1    | Background                                       |

|    | 1.2    | The System-level Design Problem                  |

|    | 1.3    | System-level Design Automation                   |

|    | 1.4    | System-level Design Methodologies                |

|    | 1.5    | Problem Approach                                 |

|    | 1.6    | Thesis Organization                              |

| 2  | Rela   | ted Research                                     |

|    | 2.1    | System-level Synthesis                           |

|    | 2.2    | The USC project                                  |

|    | 2.3    | Design Methodologies and Design Process Model 19 |

|    | 2.4    | System Specification                             |

|    | 2.5    | Transformation                                   |

|    | 2.6    | Simulation and Verification                      |

|    | 2.7    | Design Space Exploration                         |

|    | 2.8    | Hardware/software codesign and partitioning      |

|    | 2.9    | Multichip Design                                 |

|    | 2.10   | Comparison with Previous Research                |

| 3 | The | Multi  | -Chip Design Problem and Model                             | 30 |

|---|-----|--------|------------------------------------------------------------|----|

|   | 3.1 | The M  | ulti-Chip Architecture Design                              |    |

|   |     | Proble | m with an Example                                          | 30 |

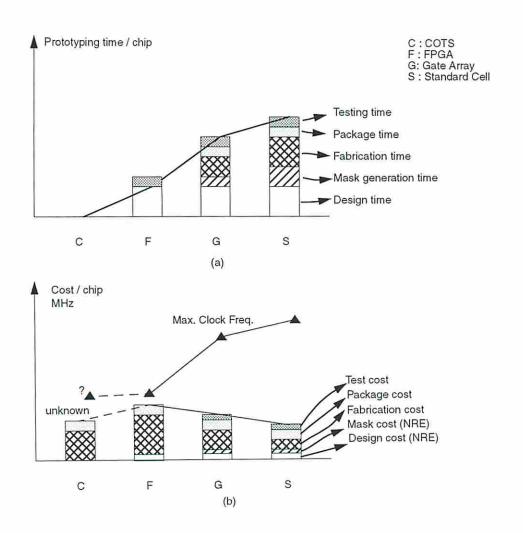

|   |     | 3.1.1  | Physical Design Style Selection                            | 33 |

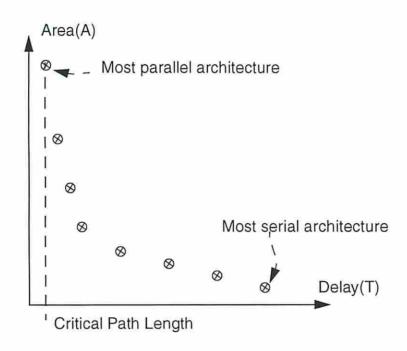

|   |     | 3.1.2  | Datapath Architecture Selection                            | 36 |

|   |     | 3.1.3  | Task-Level System Partitioning                             | 38 |

|   |     | 3.1.4  | Die Selection                                              | 39 |

|   |     | 3.1.5  | Die Clustering and Package Selection                       | 40 |

|   |     | 3.1.6  | Substrate Technology Selection                             | 42 |

|   |     | 3.1.7  | Channel Allocation and Bus Selection                       | 43 |

|   |     | 3.1.8  | Task scheduling                                            | 45 |

|   | 3.2 | A Mul  | ti-Chip Design Problem and A Model                         | 45 |

|   |     | 3.2.1  | Specification and User Specified Constraints               | 46 |

|   |     | 3.2.2  | Library                                                    | 46 |

|   |     | 3.2.3  | Target architecture                                        | 48 |

|   |     | 3.2.4  | The Problem Statement                                      | 50 |

|   |     | 3.2.5  | The Problem Approach                                       | 51 |

|   | 3.3 | A Firs | t-Order Analytical Model for Multi-Chip System Design      | 52 |

|   |     | 3.3.1  | Modeling a Design Step and Its Relationship to Other Steps | 52 |

|   |     | 3.3.2  | Physical Design Style and Datapath Architecture            |    |

|   |     |        | Selection Subproblem                                       | 55 |

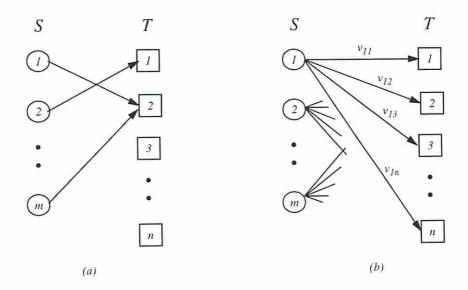

|   |     | 3.3.3  | Task-Level System Partitioning Subproblem                  | 57 |

|   |     | 3.3.4  | Die Selection Subproblem                                   | 60 |

|   |     | 3.3.5  | Die Cluster Subproblem                                     | 62 |

|   |     | 3.3.6  | Substrate Technology Selection Subproblem                  | 65 |

|   |     | 3.3.7  | Package Selection Subproblem                               | 66 |

|   |     | 3.3.8  | Bus Selection Subproblem                                   | 66 |

|   |     | 3.3.9  | Task Scheduling                                            | 68 |

|   |     | 3.3.10 | System Metric Functions                                    | 69 |

|   |     |        | 3.3.10.1 The System Cost Metric Function                   | 69 |

|   |     |        | 3.3.10.2 System Performance Metric Function                | 70 |

|   |     |        | 3.3.10.3 System Time-To-Market Metric Function             | 71 |

| 4 | ED. | EN. M  | ILP-Based Optimization Tool                                | 74 |

|   | 4.1 |        | and Linearization                                          | 74 |

|   | 4.2 |        | em Instantiation and the M-Language                        | 75 |

|   | 4.3 |        | imental Results                                            | 77 |

|   |     | 4.3.1  | Examples                                                   | 77 |

|   |     | 4.3.2  | Library Setup for Experiments                              | 79 |

|   |     | 4.3.3  | Experimental Results for Rapidprototyping                  | 80 |

|   | 4.4 | Concli | e e e e e e e e e e e e e e e e e e e                      | 84 |

| 5 | GA]  | RDEN: Genetic Algorithm-Based Optimization Tool                     | 86  |

|---|------|---------------------------------------------------------------------|-----|

|   | 5.1  | Genetic Algorithm                                                   | 87  |

|   | 5.2  | GARDEN Implementation                                               | 88  |

|   |      | 5.2.1 Encoding and Data Structure of a Solution                     | 89  |

|   |      | 5.2.2 Initialization                                                | 91  |

|   |      | 5.2.3 Selection                                                     | 95  |

|   |      | 5.2.4 Crossover                                                     | 95  |

|   |      | 5.2.5 Mutation                                                      | 00  |

|   |      | 5.2.6 Evaluation and Fitness Functions                              | 02  |

|   | 5.3  | Termination Conditions                                              | 07  |

|   | 5.4  | Experimental Results                                                |     |

|   |      | 5.4.1 Examples                                                      |     |

|   |      | 5.4.2 The Effect of Physical Style Selections                       | 09  |

|   |      | 5.4.3 The Effect of the Number of Task Partitions                   | 12  |

|   |      | 5.4.4 The Influence of MCMs                                         |     |

|   |      | 5.4.5 The Example Designs Optimized by GARDEN 1                     |     |

|   |      | 5.4.6 The Run Time Distribution of GARDEN                           |     |

|   | 5.5  | Conclusion                                                          | 20  |

| 6 | Con  | aclusions and Future Work 1                                         | 24  |

| • | 6.1  | Conclusion                                                          | 24  |

|   | 6.2  | Future Work                                                         |     |

|   |      |                                                                     |     |

| A | • •  | dix A                                                               |     |

|   |      | earization for MILP                                                 |     |

|   | A.1  |                                                                     | .36 |

|   | A.2  | Linearization of Non-linear Formulations for Task-Level System Par- | 20  |

|   |      | titioning                                                           |     |

|   | A.3  |                                                                     |     |

|   | A.4  | Linearization of System Metric Functions                            | .47 |

| A | ppen | dix B                                                               |     |

|   | Con  | nplete List of Linearized Formulae                                  | 50  |

|   | B.1  | Definition of Sets                                                  |     |

|   | B.2  | Physical Design Style and Architecture Selection Subproblem 1       | 50  |

|   | B.3  | Task-Level System Partitioning Subproblem                           |     |

|   | B.4  | Die Selection Subproblem                                            | 153 |

|   | B.5  | Package Selection Subproblem                                        | 155 |

|   | B.6  |                                                                     | 155 |

|   | B.7  | User Constraints on the System Metrics and the Objective Function   | 156 |

|   |      | B.7.1 The System Cost Constraint                                    |     |

|   |      | B.7.2 System Performance Metric Function                            |     |

|              | B.7.3 Objective Function: Modified System Time-To-Market Metric Function | 6 |

|--------------|--------------------------------------------------------------------------|---|

| Appen<br>MIL | $\mathbf{ix} \ \mathbf{C}$ Formulation in the $M$ Language               | 7 |

| Appen        |                                                                          |   |

| The          | VHDL Descriptions of Tasks in the JPEG and MPEG examples 16              | 3 |

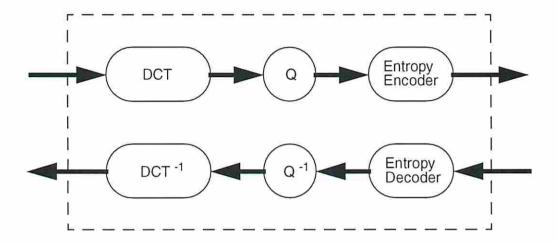

| D.1          | JPEG Package                                                             | 3 |

|              | Forward DCT Specification                                                |   |

|              | Quantizer Specification                                                  |   |

|              | Huffman Encoding Specification                                           |   |

|              | Inverse DCT Specification                                                |   |

|              | Dequantizer Specification                                                |   |

|              | Huffman Decoder Specification                                            |   |

|              | Motion Estimation Specification                                          |   |

|              | *************************************                                    |   |

| Appen        | ix E                                                                     |   |

| The          | Libraries Used in the Experiments                                        | 0 |

# List Of Figures

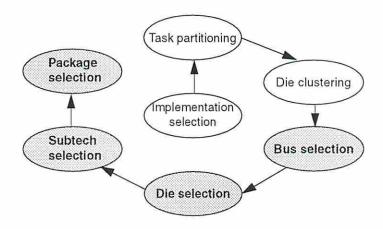

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5        | Characteristics of the design problems at different abstraction levels.  Development cycle of a digital system and concurrent engineering.  Four domains and steps of system-level design  Breaking the cyclic dependencies among design steps  Our system architecture design methodology | 3<br>4<br>8<br>11<br>14    |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

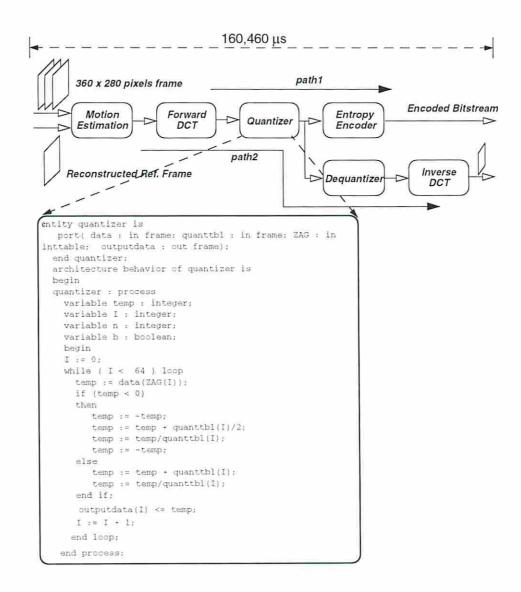

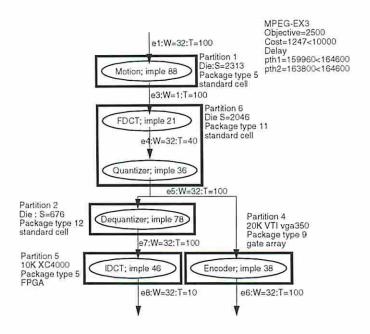

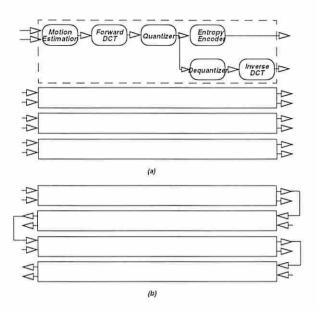

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5        | A specification for the MPEG encoder                                                                                                                                                                                                                                                       | 31<br>34<br>37<br>40       |

| 3.6<br>3.7<br>3.8<br>3.9               | processor[OHK92]                                                                                                                                                                                                                                                                           | 41<br>49<br>50<br>53<br>71 |

| 4.1<br>4.2<br>4.3<br>4.4               | Software architecture of EDEN                                                                                                                                                                                                                                                              | 76<br>78<br>82<br>84       |

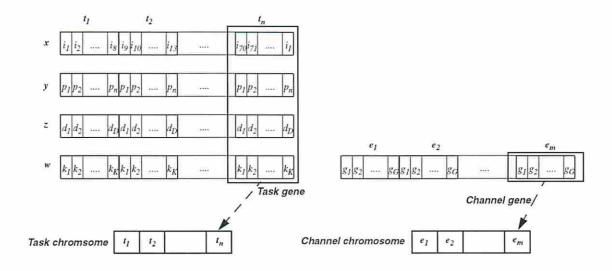

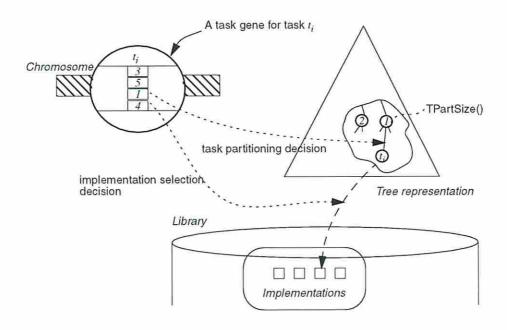

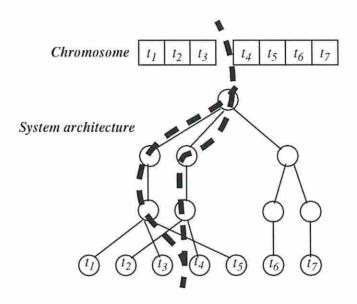

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6 | A generic genetic algorithm[Mic92]                                                                                                                                                                                                                                                         | 87<br>90<br>90<br>93<br>94 |

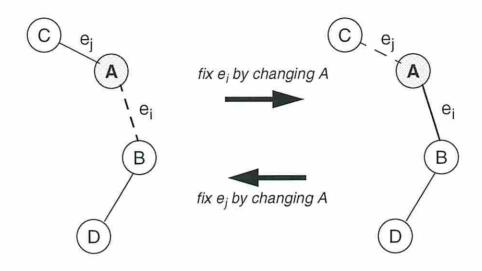

| 5.7<br>5.8<br>5.9                      | point                                                                                                                                                                                                                                                                                      | 96<br>98<br>98<br>99       |

| 5.10  | Algorithm for the crossover operation                                       |

|-------|-----------------------------------------------------------------------------|

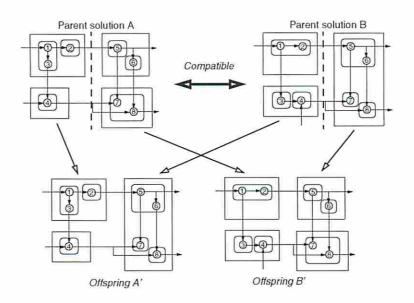

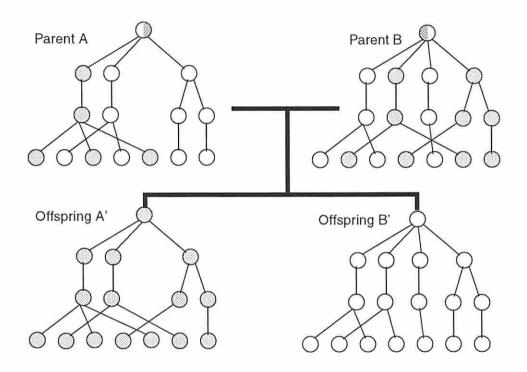

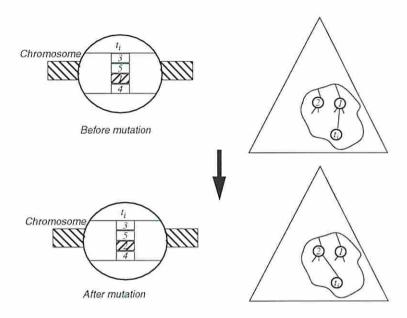

| 5.11  | Illustration of crossover operations based on compatibility 100             |

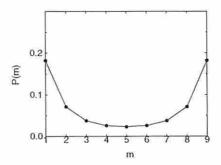

| 5.12  | Illustration of a mutation operation for task-level system partitioning 101 |

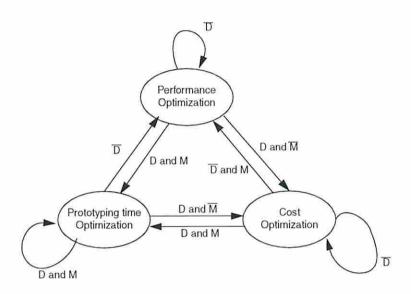

| 5.13  | Optimization sequence in GARDEN                                             |

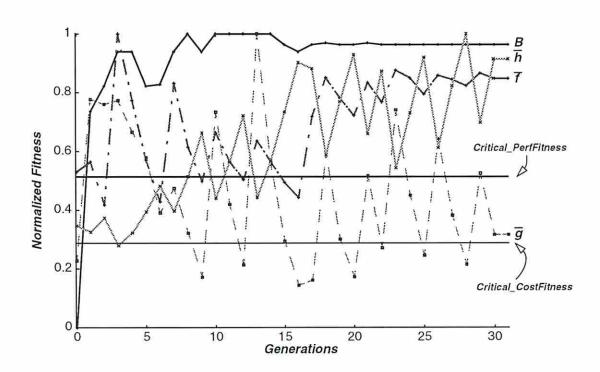

| 5.14  | Normalized fitness functions                                                |

| 5.15  | Examples used in GARDEN experiments. (a) parallel example (b)               |

|       | serial example                                                              |

| 5.16  | (c) Example 2                                                               |

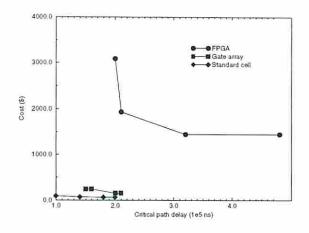

| 5.17  | Design space reachable by different physical design styles 111              |

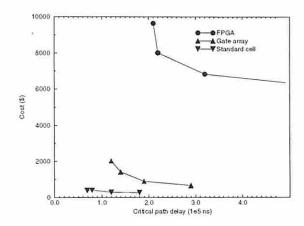

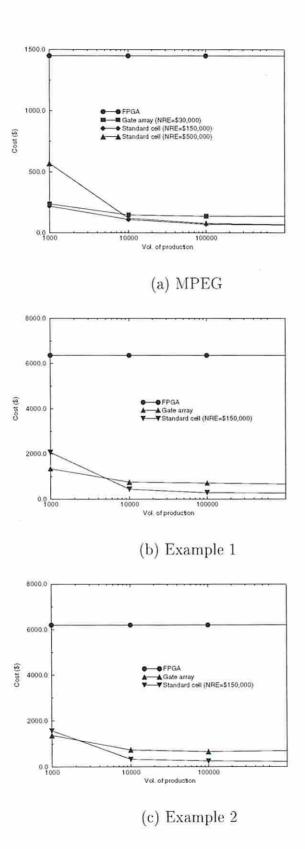

| 5.18  | The variation of system cost per unit with the volume of production 113     |

| 5.19  | The variation of system cost by the change in the number of task            |

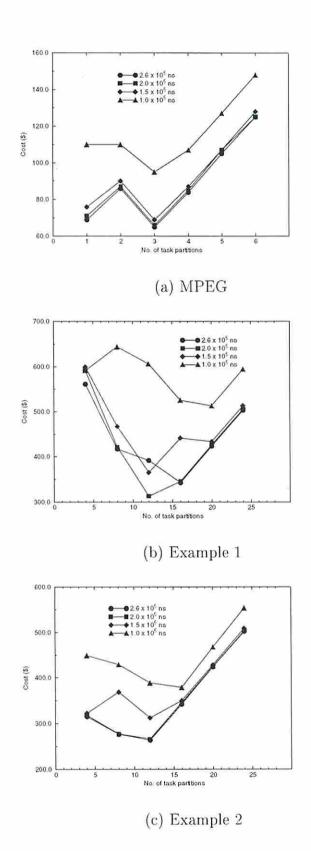

|       | partitions                                                                  |

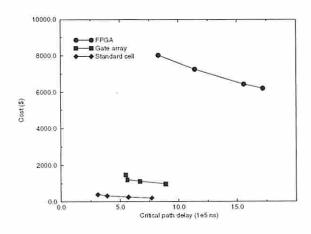

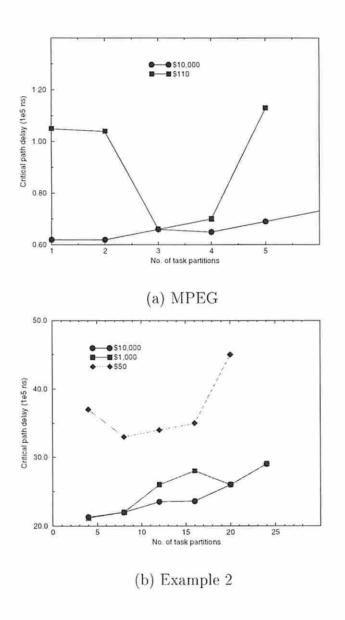

| 5.20  | The variation of system performance with the number of task par-            |

|       | titions                                                                     |

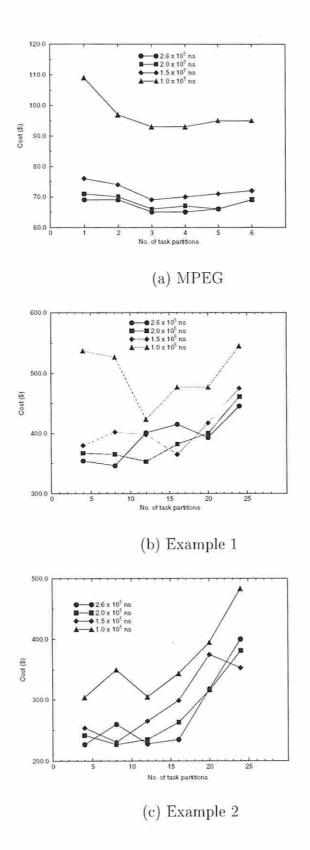

| 5.21  | The variation of system cost per unit with the number of task par-          |

|       | titions when MCMs are used                                                  |

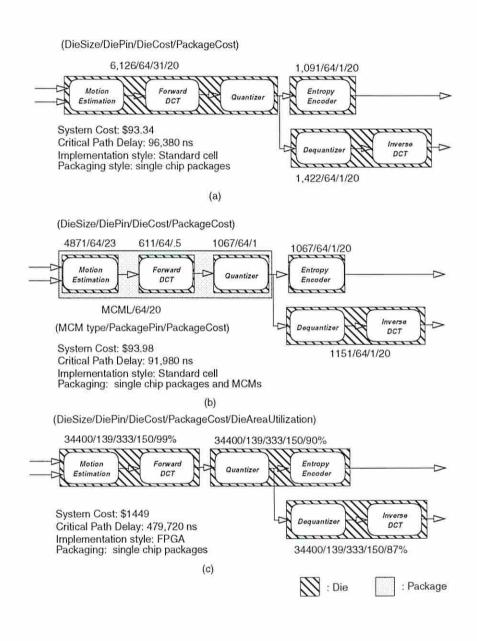

| 5.22  | Example designs optimized by GARDEN for the MPEG encoder 121                |

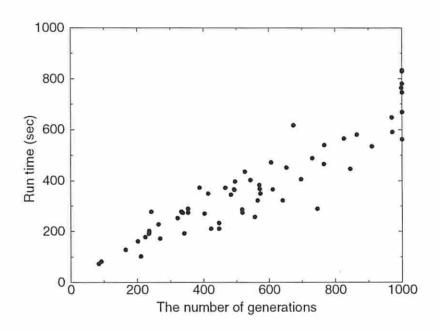

| 5.23  | The run time vs. the number of generations of GARDEN 122                    |

| W 194 |                                                                             |

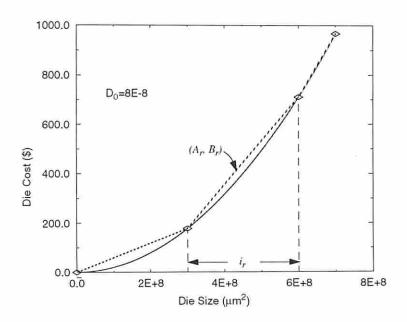

| A.I   | Piece-wise approximation of die cost vs. die size for the standard          |

|       | cell implementation                                                         |

# List Of Tables

| 1.1 | MPEG encoders implemented in different target architectures              | 4   |

|-----|--------------------------------------------------------------------------|-----|

| 1.2 | Comparison of library elements at different levels of design abstraction | 6   |

| 1.3 | Design entities in different abstraction levels                          | 8   |

| 3.1 | Characteristics of different MCM technologies                            | 43  |

| 4.1 | The number of datapath architectures for tasks in the JPEG codec         |     |

|     | predicted by BEST                                                        | 80  |

| 4.2 |                                                                          | 82  |

| 4.3 |                                                                          | 83  |

| 4.4 |                                                                          | 83  |

| 4.5 | Summary of MPEG experiment results                                       | 83  |

| 5.1 | The number of task partitions (No. of TP) and the prototyping            |     |

| *   | time (PTime) for the optimized architectures for the MPEG encoder.1      | 12  |

| E.1 | Package library                                                          | 200 |

| E.2 | Die library                                                              | 201 |

| E.3 | Bus Library                                                              | 202 |

| E.4 |                                                                          |     |

#### Abstract

In this research, we developed a model for multi-chip implementation of a digital system that captures the complex process of system-level design decisions. We also designed tools that automate the system architecture optimization process, producing trade-off informations on design alternatives. A set of system-level decisions, namely physical design style selection, datapath architecture selection, task-level system partitioning, die selection, die clustering, substrate technology selection, package selection, and bus selection are automated. These decisions are modeled as binary decisions and a set of functions is designed which quickly computes metrics for design entities based on the first-order effect of a given set of design decisions. Among metrics, the prototyping time of a system is defined as a metric for a digital system and the cost of a die is computed by considering the effect of yield. The interrelationships among the system-level design decisions are captured as validity constraints which allows the software to detect the inconsistency among design decisions and therefore reduce the risk of incorrect design decisions. The design model can be used for the purpose of both automatic optimization or interactive optimization.

Based on the model developed, two automatic optimization tools have been developed. The first tool, EDEN, is an MILP-based optimization tool constructed by linearizing the model specifically for designs that can be rapidly prototyped. As a part of EDEN, a language called M and a constraint generator called GEM were developed to automate the instantiation of the linearized formulation for a specific design problem. The second tool, GARDEN, is based on a Genetic Algorithm. Novel schemes for solution encoding, population initialization, crossover, mutation, and fitness function are presented to apply a genetic algorithm framework to

the complex optimization problem considered in this research. GARDEN is implemented in an object-oriented manner and includes many heuristics developed from our understanding of the multi-chip system design problem.

With this research, the possibility of developing a more sophisticated model and automation tools for system-level design decisions is shown, which help designers to handle more complex systems, reduce the risk of development process iterations and design a better system in a shorter time.

## Chapter 1

#### Introduction

## 1.1 Background

The growing popularity of internet, multimedia, and telecommunication applications has increased the demand for complex electronic systems. Several conflicting requirements are often associated with these systems, such as low cost, high performance, low prototyping time, short time-to-market, high testability, and low power dissipation. Reducing the time-to-market is acknowledged by all industries as the most important objective in system design, due to the fierce competition in the market and narrowing market windows. The cost of a unit is an important factor in consumer electronics applications. Power dissipation and energy consumption are important in battery-operated mobile computing and communication equipment. Performance is a prime consideration in many applications which involve real-time processing of image data sets. Designing systems considering all the factors mentioned above is understandably a difficult task.

On the technology side of digital system development, new technologies keep emerging and old technologies become economically feasible. Decreasing feature size, high-density programmable devices, and new packaging techniques are a few examples of such changes. Designers can consider employing such newly-available technologies for improving system characteristics. However, increasing the number of design options further complicates the job of system design, which is already unbearably complex.

Today's system designers are forced to think at an even higher level of abstraction and rely heavily on the design automation tools so as to be able to deal with the complexity of modern-day electronic systems under increasing time-to-market pressure. However, current design automation tools lag the demands of designers of such complex systems. Though employing the existing tools for system design steps reduces the design time, many system-level design issues cannot be handled with such tools. For example, while a combination of high-level synthesis tools, logic synthesis tools, and layout tools are sufficient to synthesize application-specific *integrated circuits*, the same is insufficient when the designer want to set up an overall implementation strategy of a specification into a system of multiple chips. To handle the system-level issues, new types of design automation tools are called for.

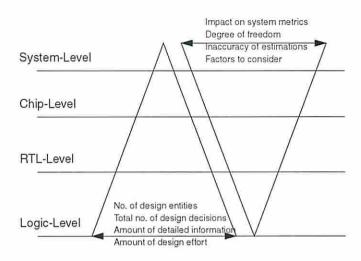

Figure 1.1 summarizes the general characteristics of the design problems at different abstraction levels. In general, at a higher abstraction level, a design problem has a smaller number of design entities and therefore, takes less time to solve. Also design decisions have a bigger impact on system quality because of more degrees of freedom. However, making correct higher-level design decisions is very difficult because of the degrees of freedom and "distance" to a final implementation. Making the right decisions in the early system development phase is a challenging task. Introducing a systematic way of analyzing the effect of different alternatives and optimizing a system architecture can reduce the number of possible design iterations and optimize a system better.

In this section, we introduce the notion of design at the *system-level* of abstraction. In the next section, we explain how system-level design is different from designing at other levels. In Section 1.3, we define the system-level design steps. In Section 1.4, we define a *system design methodology* as an ordered set of design steps and investigate the properties of these design steps. We review the system design methodologies that are currently in use and point out the problems associated with the current practices. Finally, we briefly state the problem and approach which we propose in order to automate system-level design tasks.

Figure 1.1: Characteristics of the design problems at different abstraction levels.

### 1.2 The System-level Design Problem

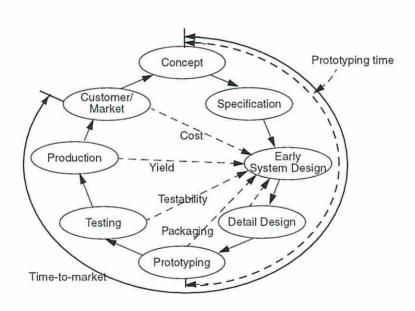

What are system-level design tasks? Since a system can be implemented in different target architectures as shown in Table 1.1, specific design steps are different for different target architectures. However, there are common characteristics shared by different system-level design tasks that differentiate these tasks from those of lower-level design steps. Figure 1.2 shows a schematic view of the development cycle of a digital system. The high level of abstraction of system design places the system-level design problem in an early phase of development where an overall system implementation strategy is set up. Peculiar characteristics of the system-level design problem come from its position in the development cycle. First, design steps encompass a broader range of development issues outside the design process itself. Second, the designer must make the right decisions based on rough information about lower level implementations.

Although across the whole development process any design decision brings a change in final system characteristics, the amount of change caused by a design decision is different across abstraction levels. In the literature, many authors have

| Target Architecture     | Comments                                          | Reference             |

|-------------------------|---------------------------------------------------|-----------------------|

| Full software           | Both single and multiple processor implementation | [GR94]                |

| Mixed HW/SW             | Two video RISC processors are used                | Optbase, Dallas, TX   |

| Full hardware<br>(ASIC) | H.261 video conferen-<br>cing standard            | [FLS+92]              |

| Full hardware (custom)  | A custom designed single chip                     | [RHU <sup>+</sup> 93] |

Table 1.1: MPEG encoders implemented in different target architectures

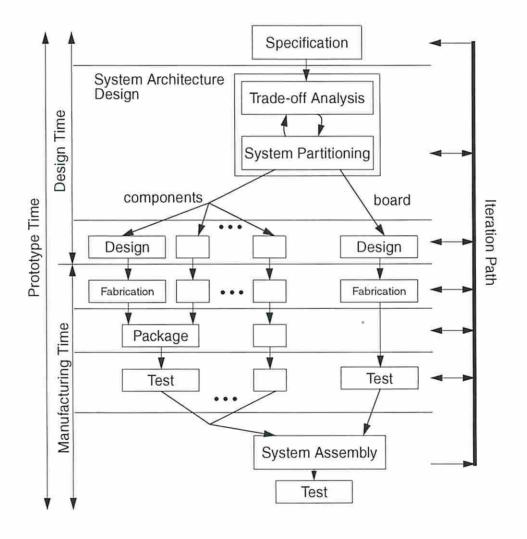

Figure 1.2: Development cycle of a digital system and concurrent engineering

pointed out the importance of making design decisions at the system level because the overall characteristics of a system are determined by decisions made at an early stage, although the time for making such design decisions does not occupy a significant part of the whole development process. "Requirements and architecture development together represent only 10% of total cost. However, once an architecture is selected, much of the development and life cycle cost of the system, as well as achievable performance, are determined" [SAM95, SA95]. In short, the importance of system-level design decisions is similar to that of an opening game of a chess match or making the sketch for a painting. Elaborate work on the details of a portion of a painting will not compensate for a bad overall sketch.

Since the impact by system-level decisions is so significant, other development issues cannot be ignored in making such decisions. For example, one of the important steps in designing a digital system is to select implementation styles for components in a system. A system can be implemented in hardware or software and a hardware module can be realized using a programmable device, an off-the-shelf component, or as an application-specific integrated circuit. In making design decisions on implementation styles of components, not only the performance and size of chips or software modules in a system must be considered but also other factors such as yield effect, packaging, and time-to-market should be considered.

In order to make good system-level design decisions, extensive trade-off analysis is necessary without knowing implementation details. Only by setting up a correct implementation strategy and resource budget based on such trade-off analysis among design alternatives a good system would be resulted in. While synthesizing each component of a system and integrating them together is itself a formidable task, without correct decisions in the beginning, it could be wasted. For example, for a system which is composed of a number of functional tasks, a system-level issue is to determine how to budget silicon area for each functional task such that the performance requirements are met, the cost is minimized, and the power dissipations is constrained. Without the right budgeting, the effort and time to optimize the design of each functional task separately could be in vain because the resulting system might be of superior performance but too expensive or there might be no economically feasible packaging method for the given design. This emphasizes the

| Abstraction  | Library Elements       |             |                      |  |

|--------------|------------------------|-------------|----------------------|--|

|              | Processing             | Storage     | I/O                  |  |

| System-level | DCT, MMU, CPU,         | RAM, ROM    | bus and I/O circuits |  |

|              | Software module        | ^           | ···                  |  |

| High-level   | Adder, Comparator, ALU | Register    | Bus, Mux             |  |

| Logic-level  | NAND, NOR, NOT         | F/F, Latch  | Wire                 |  |

| Gate-level   | Transistors            | Capacitance | Metal, Poly          |  |

Table 1.2: Comparison of library elements at different levels of design abstraction approach that making the right architectural trade-offs is usually more important than optimizing components.

## 1.3 System-level Design Automation

We have enumerated the general characteristics of the system-level design problem in the previous section without explaining why they have such characteristics. In this section, we view our problem from the design automation point to understand from where the characteristics of the system-level design problem are derived as well as to form a basis for automating system-level design tasks. For this purpose, we investigate how the design automation model of lower abstraction design tasks can be extended to include our system-level design problem.

The design of electronic systems and design automation tools at the physical level, logic level and register-transfer level of abstraction are well documented in the literature. At the physical design level, software packages are available for automatic generation and optimization of floor plans, placement of building blocks, and routing of interconnect. At the logic level, software tools have been reported for automatic generation of gate-level netlists starting from Boolean expressions. Tools have also been reported for technology mapping, which takes a generic gate-level netlist and maps it to a component-level netlist making use of components from a specified cell library. High-level synthesis tools which begin with a behavioral-level description of the circuit and synthesize an optimal register-transfer level architecture have also been developed.

Design problems at different levels of abstraction are characterized by the types of library elements (see Table 1.2). Besides library elements, different operational models, specification methods, and possible architectures are developed and used for different levels of abstraction. For the lower design levels such as logic design, the operation of a design is often modeled as an FSM, specified with a truth table or state diagram and the data are exchanged in the form of signals or bits. Such a logic function can be implemented with random logic, programmable arrays, or ROMs[McC86]. At the RTL level, the operation is modeled as a control dataflow graph and the data are represented as variable, integer, or floating-point numbers. An RTL design can be implemented in a number of different classes of architectures. Typical examples are pipelined and non-pipelined [PP88], and synchronous and asynchronous [MC80]. At the system level, a design can be viewed as communicating multiprocesses executing concurrently. Processes exchange more complicated forms of data such as arrays, aggregated data structures, and bit streams. Possible architectures to implement a system specification can be multichip systems, embedded systems, or reconfigurable systems.

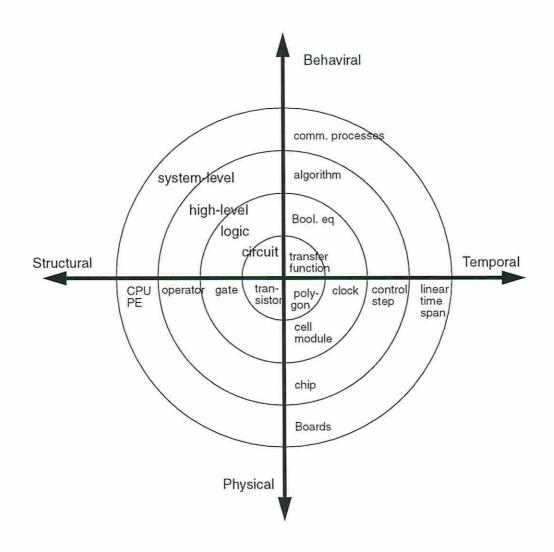

The relationships among different abstraction levels and different representations of a digital system were noted and formalized by Knapp, Parker and Granacki[KP85]. They observed that there are four different domains in which a digital system can be represented, namely data flow, timing and sequencing, structural, and physical. A design problem is defined as a translation process from the behavioral domain to the physical domain. The system-level design problem can also be modeled similarly. As shown in Figure 1.3, we added another outer layer for system-level design to extend their model.

An example of design steps as mappings between different domains is as follows: Specification is a process to create a design entity. Synthesis is a process in which a behavioral representation of a system (e.g. truth table) is translated into the structural representation (e.g. schematic). Verification is the process of comparing the structural representation and the behavioral representation. Layout is a process of translating a structural representation into a physical representation. Different types of design entities are involved in steps at different abstraction levels. In Table 1.3, we compared design entities at different abstraction levels.

Figure 1.3: Four domains and steps of system-level design

| Typical       |                    | Levels           |                |                |

|---------------|--------------------|------------------|----------------|----------------|

| step          | Gate-level         | Logic-level      | High-level     | System-level   |

| Specification | Transfer Function  | Truth Table      | Data-f-low     | Task-flow      |

|               |                    | State-diagram    | Language       |                |

| Verification  | Circuit Simulation | Logic Simulation | HDL simulation | 1-1            |

| Synthesis     | Schematic          | Logic netlist    | RTL netlist    | Partitioning   |

| Physical      | Layout             | Layout           | Layout         | Packaging Plan |

| Design        |                    |                  |                |                |

Table 1.3: Design entities in different abstraction levels

Another common characteristic of most design steps is that they are constrained optimization problems. For example, synthesizing a schematic from a truth table can be viewed as a constrained optimization problem if the designer tries to construct a schematic with a given library of gates that meets performance constraints and minimizes the module size. For the system-level, there are more metrics simultaneously involved to create a more complicated constrained optimization problem.

Across abstraction levels, the characteristics of design activities as described above are shared among design steps. On the other hand, design issues involving each step are different at different levels and the amount of impact which each design step has on a system is different across levels. Synthesizing a logic circuit and an RTL netlist are both constrained optimization problems and there is a translation process from the behavioral domain to the structural domain. But the impact of reducing the size of a large module is bigger than the impact of reducing the number of gates; similarly, satisfying the timing constraints in an RTL netlist is more important than satisfying the delay constraints of a data path logic circuit unless the logic circuit will be used many times in a system. Steps at the system level are also different from design steps at lower levels because the result of a step may not be something that can be directly simulated or laid out. The outputs mostly take an abstract form reflecting overall characteristics and a global plan about a possible implementation.

At a lower level of abstraction, the metrics associated with design entities are well defined. For instance, the cost and performance of logic are well-defined metrics e.g. area and the maximum delay from inputs to outputs, although delay definitions vary enormously. But at the system-level, such metrics are often complicated or hard to define e.g. the cost of a system not only includes the cost of fabricating a piece of silicon but many other costs such as amortized development cost, the cost of testing, and so on. Therefore, at a lower level of abstraction, designers can focus relatively easily on satisfying and/or optimizing well-defined metrics. System-level design problems demand that designers evaluate complicated and not well-defined metrics such as cost, manufacturing, development time, and user satisfiability.

In general, the lower a level is, the easier it is to assess the effect of a design decision because "distance" from a decision to a final implementation is shorter and the number of possible implementation choices is smaller. For example, the effect on size of adding a gate to a module can be predicted more accurately than the change of the size of a chip resulting from moving a task from one chip to another.

# 1.4 System-level Design Methodologies

In the previous section, we described a design problem as a translation from the behavioral to the physical domain and did not explicitly mention the ordering of design tasks in a certain way. The ordering of design tasks is important in the development process. There are a few reasons for ordering. The characteristics of design problem itself is one and the logistics of a design house is the other. Design steps cannot be executed in any order because of the dependencies among them. A design process can be represented a directed graph in which each node represents steps and each arc represents the necessary information from a source step to a destination step for the destination step to be performed. In order for a design to be completed, all steps should be visited in a certain order at least once while not violating dependencies among them. Such an ordering of steps is called a design methodology. For example, using one methodology of designing a combinational logic with gates in a library, a truth table representation is created (specification). The designer creates a schematic (synthesis). The schematic is simulated (verification) and laid out into a layout (layout).

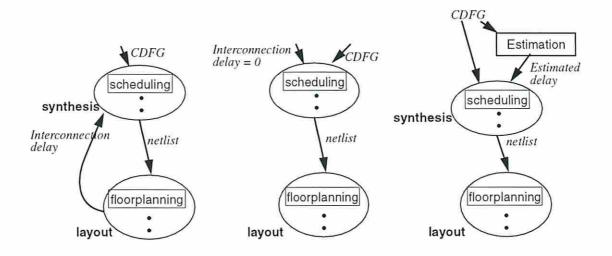

The dependencies among design steps are often cyclic. When there is a cyclic dependency between two steps, ordering them becomes difficult. It is not possible to optimize the design by optimally solving steps in sequence because design decisions for one step can be made only after the other step have been solved. Such cyclic interdependencies among steps exist not only in one translation process but across different translation processes. For example, it is well known that the two physical design steps, namely placement and routing, have such a cyclic

dependency. Scheduling, allocation, and binding also exhibit a cyclic interdependency as part of the RTL synthesis process. An example of cyclic dependencies across processes is the relationship between floor-planning and scheduling. The designer should consider floor-planning during the scheduling of operations since the delay of the critical path is influenced by the wiring length between modules while floorplanning can be influenced by scheduling[WP91]. Solving the interrelated subproblems across processes simultaneously is difficult. McFarland, Parker and Camposano called this as "integrating levels of design" [MMC88].

Based on our understanding of the design process model, we can understand existing design methodologies. The objectives of a design methodology are two fold. One objective is how to handle the complexity of design problems and the other is how to handle cyclic dependencies among design steps. Traditionally, a top-down design methodology is used to manage the complexity of a design, while the cyclic dependency problem is approached with construct-improve methodology or through the use of estimators.

Figure 1.4: Breaking the cyclic dependencies among design steps

A typical top-down design process used for moderately complex ASICs is *capture-simulate-layout* methodology. The design is captured in a schematic, then the

netlist is simulated to verify the functionality of the system and finally the chip is laid out using layout tools. The top-down methodology can be extended to include logic synthesis or high-level synthesis when the complexity of a design problem is very large. This methodology will be called *synthesize-simulate-layout*.

In the *construct-improve* methodology, a cyclic dependency among steps is broken with reasonable assumptions about the results of later steps. When a problem is found after one design step, the problem is fixed in the preceding design step. For the above example of the cyclic dependency between the floorplanning and scheduling, if the interconnection delay due to wires is not significant compared to the operator delays, we can solve the operation scheduling problem early by ignoring wiring delay. If the interconnection delay after floorplanning is found too long to be ignored, we can perform the operation scheduling again with the backannotated wire-delay information. Since such design iterations are very expensive in terms of development time and cost, there has been an effort to reduce the number of iterations by using sophisticated estimation tools which predict the results of subsequent design steps. Such estimations become more important as the coupling of steps becomes stronger. Estimating wiring delay and incorporating it in synthesis steps is critical for the current submicron semiconductor technology in which the interconnection delay is a dominant factor in determining the timing of a system.

Top-down and construct-improve types of design methodologies cannot be simply extended for the system-level design steps. This is because, at the system-level, the "integrating of levels" extends to not only the design process but also to the whole development cycle: manufacturing, customer satisfaction, and time-to-market. Furthermore an iteration in the development cycle is much longer and more expensive. For example, system partitioning is closely related to package selection. System partitioning determines the number of partitions to be packaged and the sizes of partitions. If system partitioning is carried out without considering the packaging issue, a partitioned system might not be able to be packaged due to the huge size of one of the partitions or the required packages are too expensive so as to violate the system cost constraint. Therefore, in a system architecture design, it is important to consider the availability of components and the influence

of selections on system characteristics in the early system-level design stage to reduce the project risk.

Therefore, it is desirable to develop a design methodology and tools for the early stage of the system development which has following properties:

- The methodology concurrently consider issues that encompass the whole development cycle at the beginning of a design process, as shown in Figure 1.2, and

- The designer can view and evaluate quickly as many designs as possible so that the designer can make informed decisions based on a thorough trade-off analysis of design alternatives provided.

Though the importance of such methodologies and tools that perform the above roles has long been emphasized to design better systems in a shorter time, system-level architecture trade-off analysis and optimization remains as an implicit part of the current design process. There are few tools and frameworks compared to the software engineering field[Boe88]. Recently, interest in defining such methodologies for hardware system development is growing. The RASSP project is one such research project that focuses on reducing the development time by improving the current design methodology[Ric94]. In this thesis, we present one approach to build such tools based on a system design model that reflects concurrent engineering issues and can be used to evaluate the effect of possible design alternatives in early development phase.

# 1.5 Problem Approach

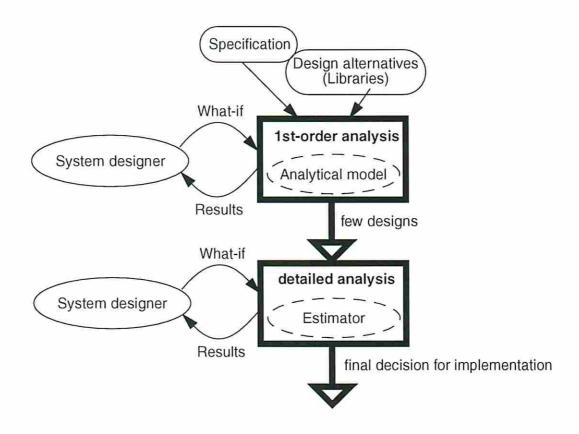

Our approach to achieve the aforementioned goals is shown in Figure 1.5. The design procedure is divided into a system architecture design phase and a component design phase. During the system architecture design phase, the designer generates a small number of good candidate designs using optimization tools that work at a high abstraction level but are incorporated with lower-level estimators. The designer further narrows the candidate designs from designs suggested by optimization tools and manually optimizes the selected designs with an interactive

what-if analysis tool. The final round of candidate designs is further verified with more detailed and specialized estimators. From the detailed information for candidate designs, finally a design is selected and a detailed design process can be started.

Figure 1.5: Our system architecture design methodology

The focus of our approach is the trade-off between the accuracy and the speed of estimation tools. While higher accuracy of predicted results can be achieved by emulating the design process more closely, such an approach is often impractical in the early stage because of the huge design space and the excessive computation time. On the other hand, a less accurate but faster estimator can evaluate many designs quickly but the predictions can deviate enormously from the final implementation. For example, although a predicted partition size fits into a selected die type, there is still a chance that the selected die type is too small. Therefore,

to reduce the whole system architecture design time while generating a reliable result, gradually detailed estimation and optimization with designer interaction is desirable.

To implement the above design methodology, in this thesis, we define a multichip architecture design problem as a subset of the system-level design problem and investigate the possibility of developing a fast estimation method and optimization tools that automate the system-level architectural trade-offs.

# 1.6 Thesis Organization

The organization of this thesis is as follows:

Chapter 2 surveys related research on system-level design automation.

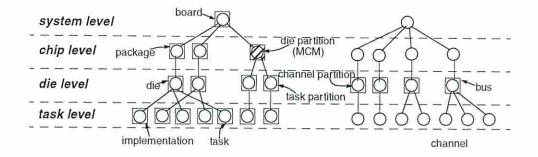

In Chapter 3, our approach for modeling the multi-chip system design problem is described. The binary variable representation of system design decisions and the first-order analytical model that computes metrics of design entities at different abstraction levels and checks the validity of a solution will be presented.

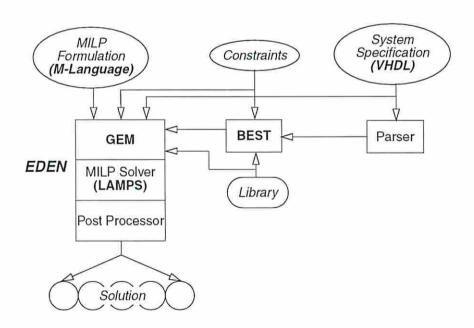

A Mixed Integer Linear Programming (MILP) approach for optimizing the multi-chip system architecture for rapid-prototyping will be given in Chapter 4. The software architecture for an MILP-based optimization tool called EDEN will be detailed. Experimental results of the system architecture are also presented.

In Chapter 5, another optimization approach for multi-chip system design based on a Genetic Algorithm will be described. The design of GARDEN, the optimization tool using a genetic algorithm will be detailed. Experimental results are given that demonstrate how GARDEN can be used for various trade-off analyses of a system architecture.

Finally, a summary of this thesis and outline of future research are given in Chapter 6.

## Chapter 2

#### Related Research

## 2.1 System-level Synthesis

Attempts to automate system-level design have only been recent. Design tasks are different from each other depending on target architectures since computing systems can be implemented using hardware, software, or a mix of hardware and software modules. An example of different implementations of the same system behavior was given in 1.1.

Hardware-software codesign is an area of system-level design which has been researched the most. Design of application-specific multiprocessor systems with heterogeneous processor types has been studied at the University of Southern California, and will be discussed later. Hardware implementation can be classified into reconfigurable systems and hardwired systems. Reconfigurable systems implement specifications using arrays of programmable logic devices. Because of their capability of on-the-fly change of system behavior, such systems are used for emulating a complex digital system or a military system in which a high performance light-weight system is required and the system is expected to perform several predetermined functions. Hardwired systems which aim at high performance are typically implemented in multi-chip systems. In this chapter, our aim is to summarize the salient work in the area of system-level design automation.

### 2.2 The USC project

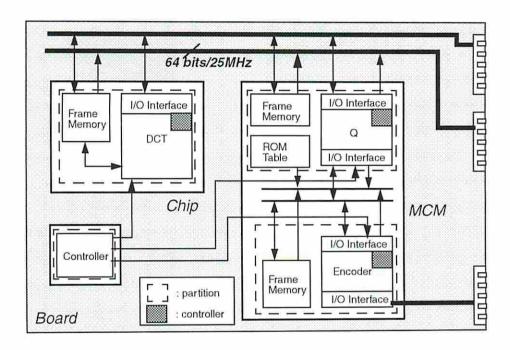

The Advanced Design Automation System (ADAM) suite of tools [GKP85] was developed at the University of Southern California. ADAM design tools synthesize a low-cost RTL implementation from the given behavioral specification using the modules from a given operator library such that the RTL implementation satisfies the timing constraints provided by the designer. Input specification to the ADAM system is either in the form of a VHDL description or a control data flow graph. The Design Data Structure (DDS) is used for internal representation of designs [KP85]. The datapath generated by ADAM is an RTL netlist of selected library components and the control path is a finite state machine description. Unified System Construction (USC) [PCG93] is a successor of the synthesis part of the ADAM design automation research project, and aims to develop an integrated set of automation and prediction tools to produce system-level designs. The target architectures that the system can produce are (a) heterogeneous multiprocessors [Pra93, DP94], (b) asynchronously communicating multi-chip ASIC systems, or (c) synchronously communicating multiple ASIC systems[HRP96]. The main application domain of USC is that of real-time systems. Tools which are developed up to this point can perform behavioral-level partitioning [Che94], behavioral-level estimation [KP95], task-level system partitioning and package selection [HRP96], and global task scheduling on an application specific heterogeneous multiprocessor [Pra93, DP94]. BEST[Kuc91] is a comprehensive tool for estimating the number of operators, registers, multiplexers, wiring space, and delay for a process, starting from the control-data flow graph description of the process. To synthesize a synchronous multi-chip system of a specification which does not fit on a single chip, CHOP[KP95] performs behavioral partitioning at the operation level based on behavioral estimations done by BEST. MCS[Hun92] schedules the partitioned behavioral specifications across chip boundaries synchronously so as to satisfy the user specified timing constraints as well as pin constraints posed by chips. SOS[Pra93] pioneered the automation of synthesis of application-specific heterogeneous multiprocessor systems. Prakash[Pra93] used a task flow graph model to represent a system specification. The library for SOS consists of general or special-purpose microprocessors and special hardware processors. Prakash developed a formal model of multiprocessor synthesis using mixed integer linear programming (MILP). By solving the MILP formulation, SOS synthesizes noninferior designs which satisfy (or minimize) the timing constraints defined on the task flow graph while minimizing (or satisfying) the system cost. The synthesis results of SOS include selecting the number and types of processors in the library which best handle the given tasks and synthesizing a multiprocessor architecture by determining the interconnection style. SOS also statically schedules tasks in the task-flow graph on the chosen processors as well as the data-transfer activities among processors. SOS computes the amount of local memory which is used as storage for the code and temporary computation result for each processor in the synthesized system. Batista[DP94] extended SOS in his work, MEGA, to synthesize heterogeneous multiprocessor systems with task-level pipelining. The genetic programming paradigm was used in MEGA. Batista considered two other computing models in addition to the traditional deterministic computing model: (a) the execution time of a task on a given processor is treated as a random variable rather than a constant, and (b) the execution time of a task is divided into two parts, a mandatory part and an optional part. The first model is useful in situations where the execution time of a task cannot be estimated accurately because the number of iterations of the loops in the algorithm is dependent on the nature of the input data or there are natural statistical variations in design properties due to design and fabrication. The second model is useful in some applications such as image processing. Chen[Che94] proposed process-level partitioning across packages as an alternate way of behavioral partitioning. In his work also, the task flow graph description of a system was used. Different implementations of each task in the task flow graph and package information were supplied in a library. ProPart[Che94] synthesizes a multi-chip system by selecting an implementation for each process, partitioning the processes across multiple chips, and selecting a package type for each chip which minimizes the cost of the system while satisfying the timing constraints given on the task-flow graph. Chen formulated the problem first using ILP and then used a genetic algorithm to speed up the run time of ProPart. Chen also studied the problem of concurrent scheduling of internal behavior of tasks and I/O transactions with unbounded delay, using the communicating process model of a system.

# 2.3 Design Methodologies and Design Process Model

In software engineering research, the design methodology for building complex software systems has been studied for decades, and methods for software project planning, estimating development cost, and scheduling system development have long been understood[Boe88, Pre87]. The waterfall model is the most influential software process model. In this model, a software development process consists of successive stepwise refinement stages namely, operational plan, operational specification, coding specification, coding, parameter testing, assembly testing, shakedown, and system evaluation. In addition to the stages, feedback loops from one stage to the previous stage exist along with prototyping in parallel with requirement analysis. The waterfall model requires an elaborate specification and documentation step between stages, which is difficult in the early stage of software development. Boehm [Boe88] proposed a spiral model in which 4 basic development steps are repeated with gradual refinement on the software requirements and implementation. The 4 basic steps are "determine objectives, alternatives, constraints", "evaluate alternatives, identify, resolve risks", "develop, verify, nextlevel product", and "plan next phases". As the development process goes through each cycle, more elaborate specification, detailed architecture consideration, and a more refined system are evolved by prototyping, simulation, and benchmarking. Therefore, the spiral model allows incomplete specification in the early phase of design, and reduces risk by evaluating the risk factor and prototyping at each round of the development process.

An important recent change in the hardware system development process is the emphasis on concurrent engineering. The sequential approach of designing a system has an inherent possibility of an iteration in a system development cycle due to failure to address issues of a later development task in early development tasks.

With people of different disciplines such as design, test, manufacturing, marketing, etc. participating in the early phase of system development, concurrent engineering tries to reduce the aforementioned risk of an development iteration. Therefore, a mechanism that ensures the end product will meet constraints posed by different groups of people is necessary. Darr and Birmingham [DB96] developed such a tool called Automated Configuration Design Service (ACDS) for a system that is built with a set of available components. ACDS is composed of catalog agents which maintain the information on available components, a system agent which requests parts that meet the specification and constraints from catalog agents, and constraint agents which monitor the feasibility of a current design. System design by multi-disciplinary people can be coordinated by ACDS to detect infeasible designs and prune the design space.

Gajski et al. [GNRV96] classified digital system design methodologies currently in use in the industry, namely capture-and-simulate methodology and describe-andsynthesize methodology. Capture-and-simulate methodology is a primary design methodology for ASICs in last few decades. In this methodology, an informal specification is translated into a block diagram by the chip architect and functional blocks are refined into logic circuits. Then each circuit is simulated and laid out. With the development of logic synthesis and high-level synthesis, the function of a block diagram is often described at a higher level of abstraction such as a Boolean equation or a state diagram and then translated into a logic circuit. For system-level design, Gajski et al. proposed a specify-explore-refine (SER) methodology. They pointed out that the design space exploration was an important but informal step in the system design which is often not pursued thoroughly in the design process. In SER methodology, the exploration stage is further divided into allocation and partitioning. In the allocation step, the physical implementation for a class of objects such as channels is selected from libraries based on the constraints defined by designers. Then, the class of objects is partitioned into multiple instances of selected components. For each configured system, system metrics are estimated. By manually changing design decisions, designers further optimize the system configuration.

Rapid-prototyping of Application Specific Signal Processor (RASSP) [SAM95] is concerted effort to develop a design methodology and design automation tools for DSP applications to reduce the cost and development time by four-fold. In order to achieve this, RASSP uses the following aspects in its design methodology:

- requirement traceability,

- virtual prototyping in which a software model of the hardware is developed,

- synthesis and reuse of Hardware/Software modules, (design reuse)

- use of VHDL, and

- system engineering EDA tools (pricing models and design adviser).

The RASSP design methodology starts with a VHDL specification of the system. The VHDL specification is used to simulate the system behavior. Many VHDL models are required for complex modules as well as standard parts because design reuse is an important issue. Then the architectural trade-off is made for a problem like hardware-software partitioning. Each module is refined and implemented at a more detailed level by virtual prototyping. The integration among modules is also tested using virtual prototyping.

### 2.4 System Specification

There are many languages developed for the specification and verification of hardware. VHDL[Ins88] is the most well-known and probably most widely used language. VHDL can be used for the specification, verification, and synthesis of hardware at different levels. HardwareC[MK88] was developed mainly for synthesis, and is based on the C programming language. Though not developed for hardware specification and verification, there are other languages devised for the purpose of describing protocols among communicating processes. Specification and Description Language(SDL)[BS91] has been developed by the CCITT for the specification of a telecommunication system. CSP (Communicating Sequential Processes)[Hoa78] is a programming language developed to formally specify the communication and synchronization between processes.

The capability of HDLs describing desired behaviors algorithmically greatly reduced the amount of specification work for complicated hardware and the overall functionality is easily verified. However, the language description is still tedious for an early design phase and not intuitive. There are other efforts that focus on building a graphic interface with which the designer can capture design at a conceptual stage. StateChart[DH89] and SpecChart[NVG91] are tools that help the designer to describe a system as a set of a concurrent processes. The communication channel among processes is described as a global variable and the process behavior is captured as a state diagram. The final design is translated into a VHDL description, which is simulated with VHDL simulators.

While the above tools are designed to have a general applicability, there are other graphic tools with description languages that are designed for specific types of digital systems. Ptolemy[KL93] uses synchronous dataflow(SDF) to describe the behavior of a DSP application. The Alta group developed a set of tools for specifying multimedia and telecommunication applications around a components library which is a well-defined set of building blocks in designing the aforementioned systems. The design can test various architectural level configurations of building blocks in a library.

The system specification is often given in a natural language which is not formal but convenient. Translating an informal specification into a formal specification would greatly reduce the burden of specifying a system in a formal language. Granacki and Parker [GP87] developed a translator using artificial intelligence natural language understanding techniques which can construct a formal specification of a system from a specification written in natural language.

Internal representations for system specification are developed as part of specification effort. Codesign Finite State Machine (CFSM) was proposed by Chiodo *et al.* [CGJ<sup>+</sup>94]. The CFSM is a model based on a network of FSMs communicating with each other. The reactive nature of CFSM is suitable for a control-dominated system. Both hardware and software specification in a higher-level language such as Esterel, StateCharts, and a subset of VHDL can be translated into CFSM. Similarly, the concurrent process model of SpecChart is internally represented as a set

of FSMs[NVG91]. Srivastava and Brodersen used a queuing network representation for the system specification described in VHDL in their work for SIERA[SB95].

#### 2.5 Transformation

Transforming a given specification is another area of research to improve the system quality before starting detail designs. Process transformation for system-level design was proposed by Hagerman and Thomas [HT92]. Two types of transformations, namely module expansion and behavior merging, are used to explore the trade-off between implementation size and performance. Module expansion merges two physical modules into one while behavior merging combines two processes into one. Adams and Thomas[AT95] considered another transformation scheme for hardware-software codesign. A given behavioral description is clustered into a number of tasks and metrics for each task in different implementations that can be moved are defined. Then, fractions of code are moved among processes or to new processes to make architectural trade-offs.

### 2.6 Simulation and Verification

To speed up the verification process of a system during development, the underlying representation for a system specification is constructed such that the simulation based on the high-level modeling of components is possible. A system-level simulation tool called Ptolemy was developed at the University of California, Berkeley[KL95]. Systems such as multi-rate signal processing systems, asynchronous signal processing systems, and communication networks can be simulated. Blocks in Ptolemy can be represented in one of the supported paradigms such as synchronous dataflow, dynamic dataflow, discrete event, and digital-hardware modeling. A system can be specified using multi-paradigm components depending on the demands of the application. Chiodo et al.. [CGJ+94] used CFSM as a model for co-simulating both hardware and software. The time behavior of a CFSM is constructed with an equivalent FSM network. Then a timed sequence of events is checked to determine whether it is consistent with the specification.

Thomas, Adams, and Schmit[TAS93] presented a co-simulation environment. Under the given single processor system architecture model, hardware simulation is performed with Verilog processes that communicate with software processes by means of the Unix socket utility.

## 2.7 Design Space Exploration

With the capability of simulating a multi-paradigm system specification, various manual trade-off analyses are possible. However, no work is known to us to automate the design space exploration in the system-level design, though the importance of design decisions are pointed out by a number of researchers[SA95, SAM95, Gaj94, GNRV96]. An example of manual trade-off analyses with Ptolemy by changing parameters during simulation is given for a multiprocessor-system design for a full-duplex telephone channel simulator[KL93]. In general, any system-level simulation tool can be used for the trade-off analyses purpose.

# 2.8 Hardware/software codesign and partitioning

There are a number of design steps in developing an embedded system. Hardware/software partitioning, co-specification, co-simulation, software module generation, and interface synthesis are such design steps. Since works on other design steps are described in previous sections, works on hardware/software partitioning are described. A considerable research work devoted to hardware/software partitioning because partitioning a given system specification into hardware and software parts is a very important system architectural design decision for embedded system design. Since partitioning can be performed at different granularity[EHB93], Ernst, Henkel and Benner classified partitioning schemes into coarse-grain partitioning and fine-grain partitioning.

Gupta and DeMicheli[GM92] used a heuristic to perform fine-grain hardware/software partitioning. Starting from an all-hardware implementation, operations are selected to move into software implementations depending on a number of criteria.

The communication overhead, presence of unbounded delay operations, and/or decoupling of control and execution are examples of such criteria.

Ernst, Henkel and Benner[EHB93] developed a fine-grain partitioning scheme called hardware extraction. A specification is divided into basic blocks which do not have control structures such as branching or loops. The performance of blocks in both hardware and software implementations is estimated. A partitioning is optimized using simulated annealing along with the estimated performance of blocks. In computing the cost function for a partitioning, the delay caused by moving a block from software to hardware is also considered.

Thomas, Adams, and Schmit developed a set of guidelines for coarse-grain hardware-software partitioning [TAS93]. Those guidelines are based on the type of an application, the characteristics of the task function, the static properties of task behaviors, and the amount of custom hardware.

Vahid, Gong and Gajski[VGG94] proposed a heuristic that is based on binary search for hardware-software partitioning. In the proposed heuristic, instead of using a weighted cost function that considers both performance constraints and hardware size simultaneously, the possible range on the amount of custom hardware is divided into a set of ranges and used as a size constraint. The cost function is defined such that it returns 0 if there is at least one partitioning that does not violate both types of constraints. Then, the smallest hardware size is obtained by performing binary search within a possible range of hardware size with this cost function.

Kalavade and Lee [KL94] reported a constructive heuristic which traverses a task-flow graph and maps nodes into hardware or software based on an appropriate objective function.

## 2.9 Multichip Design

## Task-level System Partitioning

Traditionally partitioning a netlist into multiple chips is one of important design tasks in developing a digital system due to the size and pin count constraints of packages. A better optimization scheme by partitioning a specification at the behavioral level was proposed by Lagnese and Thomas [LT89]. Chen further moved the partitioning problem to the task-level [Che94]. Chen used a Genetic Algorithm and MILP to perform task-level partitioning. Clustering of functional objects to improve the partitioning process was proposed by Vahid and Gajski [VG95]. An interactive partitioning method using a set of process transformation primitives has been proposed [IOJ94].

## The Physical Design Style Selection

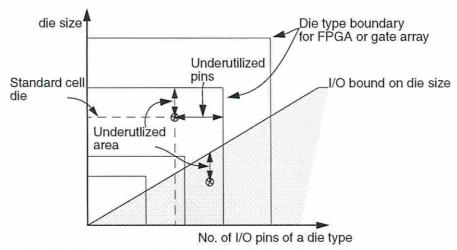

Although the selection of a physical design style among different ASIC design styles available today is an important step in the beginning of a digital system development, there is no intensive research effort on automating a physical design style selection for VLSI chip design because of the difficulty of quantifying the effect of physical design style selection. Instead, many selection guidelines were published based on the qualitative difference among possible physical design styles [Hol87, HR91, EBCH86]. The efficiency of silicon area usage, performance, and turn-around time are primary trade-off points in selecting a physical design style for a chip.

## Datapath Architecture Selection

Chen [Che94] pioneered a datapath architecture selection for a functional task in a specification. Chen used used mathematical programming to find a datapath architecture for each task in a specification such that the overall system cost is minimized while satisfying performance constraints. Later, Kalavade and Lee described the extended partitioning problem [KL95] in which several possible implementations were considered that may exist for every mapping of tasks to different implementation styles. The extended partitioning problem is to find a hardware/software mapping, an implementation point  $(A_i, t_i)$ , and a global schedule for each node such that the user-specified latency is achieved. The problem attempts to optimize the area cost of the implementation. The authors assume the availability of two curves for every node, namely, a hardware implementation curve

and a software implementation curve. These curves are described as sets of tuples of the form  $(A_i, t_i)$ , where  $A_i$  represents the area (or memory) requirement of the *i*-th implementation and  $t_i$  is the execution time corresponding to the implementation. Adams and Thomas partly addressed the issue of datapath architecture selection in the global allocation problem [AT95], where an implementation point is selected from the several alternatives generated by a high-level synthesis program.

## System I/O synthesis

Another important design step in a digital system development is the synthesis of the I/O subsystem, in which scheduling of I/O activities and the type of a bus used for the communication among processes are determined. Filo et al.. [FKCM93] classified the communication among processes as blocking and nonblocking. Blocking communication implies that two processes engaged in communication wait for one another, whereas in non-blocking communication the sender/receiver continues its operation without waiting for an acknowledgment from its communication partner. Blocking communication corresponds to handshaking and non-blocking corresponds to synchronous communication. File et al.. proposed an algorithm which optimizes the interface by reducing the amount of blocking communication. PUBSS is a system to generate a relatively scheduled I/O description called Behavioral FSM from a specification in VHDL and then solves a set of linear equations to minimize the handshaking in communication[WM93]. Narayan and Gajski NG94 proposed heuristics which find the width of a bus that serves as the physical path for a set of interface communication channels. Filo et al. [FKCM93] proposed an algorithm which optimizes the interface by reducing the amount of blocking communication.

## Die clustering and MCMs

The emergence of MCMs as a package alternatives, it has been noticed that exploiting the advantages of MCMs over other packaging methods requires a good partitioning scheme. Partitioning a system into multiple dies for maximal utilization of MCMs is attempted at different abstraction levels.

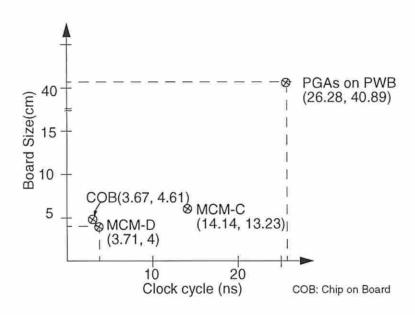

There are trade-off studies comparing the cost and performance of a single big chip to that of several smaller chips packaged into an MCM. In the report by Dehkordi et al..[DRB+95], an exhaustive partitioning method was used to find an optimal partition of the SUN MicroSparc system. The partitioned system with MCMs is considerable cheaper than the existing single design. Another similar trade-off study by O'Brien et al.. [OHK92] showed the cost advantage of MCMs over a single chip by partitioning an IBM RS/6000 system into a set of 8 chips. Both results show that task-level partitioning and package selection are the main factors in determining the total system cost and that such decisions should be considered in early design stages. Shih et al. [SKT92] proposed an algorithm for structural partitioning of a system graph (a graph of interconnected combinational blocks and registers) into chips on a MCM. Though it is not directly developed for MCMs, Chen [Che94] used mathematical programming and a genetic algorithm to partition a system specification into a number of packages to minimize the cost of a system. Khan and Madisetti [KM94, KM95] used quadratic non-linear programming to partition a system for MCMs for yield consideration and low power. In their formulation, the yield is fixed to a given value and consequently limits the size of dies which can be used in a system.

# 2.10 Comparison with Previous Research

Work related to hardware-software codesign by Gupta et al. [GM92] aims at the rapid prototyping of embedded systems. Their main focus is on hardware-software partitioning, software module generation, and interface synthesis. In hardware-software partitioning, multiple implementations of tasks were not explicitly considered. Many issues related to the portions of the system designed in hardware are not addressed, e.g. selection of implementation style, partitioning of tasks into chips, and selection of packages which influence the system cost and performance. The work presented in SIERA [SB95] is not an automation tool, but a system design methodology developed from long experience in designing real-time digital systems. The most important steps such as hardware-software partitioning are done manually. The target architecture is a hierarchical bus-based system. After